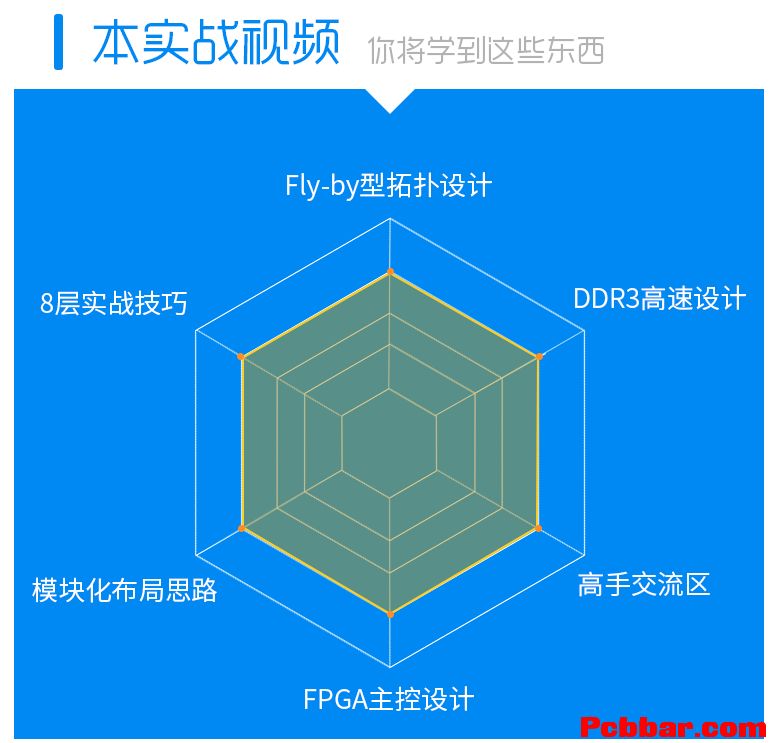

本视频教学以allegro1 6.6和IMX6为平台,重点介绍DDR3内存的设计思路,一共四颗DDR3,采用菊花链( Fly-By)的拓扑结构。讲解了DDR3设计的信号class分组,信号的同组同层布线、信号时序等长及常用规则注意事项,信号完整性、电源完整性的规划等,让学习者知其然知其所以然,DDR3的设计看_上去是很高大上的,但是只需要弄懂其中的几个基本要点,也很简单的。本视频采用的8层板设计,也是大家学习多层板的利器。

本视频录制是结合了工程师丰富的项目实战经验,讲述整个DDR3设计的思路以及各个PCB设计环节中的一些细节技巧,细节决定成败,愿学习我们视频的朋友们,多多注重我们视频讲解的布局思路、布线思路。处理细节,早日成就PCB高手!

学习目标

1、掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程

2、掌握DDR3设计的知识要点

3、掌握3W原则的PCB设计

4、了解菊花链拓扑结构及设计规则

5、掌握蛇形等长走线

课程介绍

1、原理图简单讲解、网标输出、错误解析

2、DDR菊花链拓扑结构布局分析

3、叠层设置以及阻抗规则设置

4、Fanout处理、Class设置、布线规划

5、DDR3数据线布线( 1 )

6、DDR3数据线布线(2 )

7、DDR3地址、控制线布线(1)

8、DDR3地址、控制线布线(2)

9、 电气规则讲解与规则设置

10、DDR3数据线时序等长( 1 )

11、DDR3数据线时序等长(2 )

12、DDR3地址、控制线时序等长( 1 )

13、DDR3地址、控制线时序等长(2 )

14、地平面处理与电源平面分割

15、后期丝印处理、文本添加、整板铺地铜处理

16、gerber文件输出、贴片文件输出

[size=17.1429px]DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间不需要考虑等长;地址、控制、时钟信号:地址、控制信号以时钟作参考,误差控制在100MIL以内,Address、Control与CLK归为一组,因为Address、Control是以CLK的下降沿触发的由DDR控制器输出,DDR颗粒由CLK的上升沿锁存Address、Control总线上的状态,所以需要严格控制CLK与Address/Command、Control之间的时序关系,确保DDR颗粒能够获得足够的建立和保持时间。

[size=17.1429px]关注等长的目的就是为了等时,绕等长时需要注意以下几点:

确认芯片是否有Pin-delay,绕线时要确保Pin-delay开关已经打开; 同组信号走在同层,保证不会因换层影响实际的等时;同样的换层结构,换层前后的等长要匹配,即时等长;不同层的传播延时需要考虑,如走在表层与走在内层,其传播速度是不一样的,所以在走线的时候需要考虑,表层走线尽量短,让其差别尽量小(这也是为什么Intel的很多GUIDE上面要求,表层的走线长度不超过250MIL等要求的原因); Z轴的延时:在严格要求的情况下,需要把Z轴的延时开关也打开,做等长时需要考虑(ALLEGRO中层叠需要设置好,Z轴延时才是对的)。 蛇形绕线时单线按3W,差分按5W绕线(W为线宽)。且保证各BUS信号组内间距按3H, 不同组组间间距为5H (H为到主参考平面间距),DQS和CLK 距离其他信号间距做到5H以上。

[size=17.1429px]而另一个核心重点便是电源处理。DDR3中有三类电源,它们是VDD(1.5V)、VTT(0.75V)、VREF(0.75V,包括VREFCA和VREFDQ)。

[size=17.1429px] 1. VDD(1.5V)电源是DDR3的核心电源,其引脚分布比较散,且电流相对会比较大,需要在电源平面分配一个区域给VDD(1.5V);VDD的容差要求是5%,详细在JEDEC里有叙述。通过电源层的平面电容和专用的一定数量的去耦电容,可以做到电源完整性。

[size=17.1429px] 2. VTT电源,它不仅有严格的容差性,而且还有很大的瞬间电流;可以通过增加去耦电容来实现它的目标阻抗匹配;由于VTT是集中在终端的上拉电阻处,不是很分散,且对电流有一定的要求,在处理VTT电源时,一般是在元件面同层通过铺铜直接连接,铜皮要有一定宽度(120MIl)。 [size=17.1429px]

[size=17.1429px] 3.VREF电源 ,VREF要求更加严格的容差性,但是它承载的电流比较小。它不需要非常宽的走线,且通过一两个去耦电容就可以达到目标阻抗的要求。DDR3的VERF电源已经分为VREFCA和VREFDQ两部分,且每个DDR3颗粒都有单独的VREFCA和VREFDQ,因其相对比较独立,电流也不大,布线处理时也建议用与器件同层的铜皮或走线直接连接,无须在电源平面层为其分配电源。注意铺铜或走线时,要先经过电容再接到芯片的电源引脚,不要从分压电阻那里直接接到芯片的电源引脚。 [size=17.1429px]

[size=17.1429px]

[size=17.1429px]

[size=17.1429px]

|  /1

/1