|

|

引言% R5 i' h7 w; U3 H+ j I

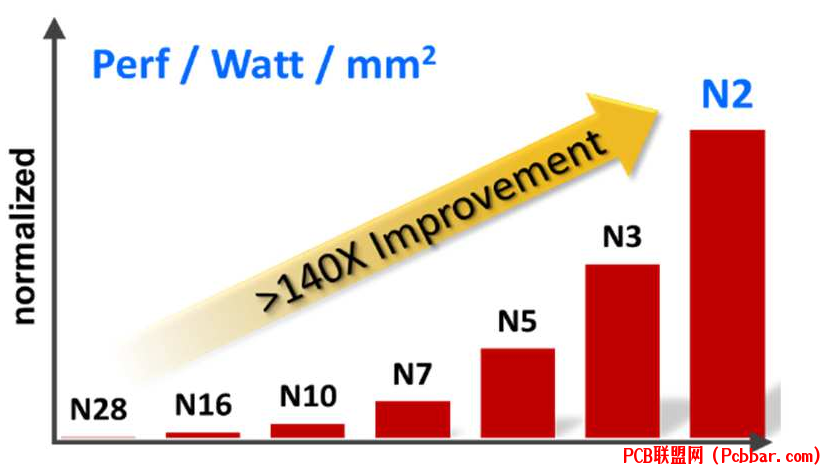

半导体行业随着台积电2纳米(N2) CMOS平台技术的开发取得重大进展。这项技术专门针对人工智能、移动设备和高性能计算(HPC)应用中的节能计算需求进行优化。特别是在2023年第一季度生成式人工智能取得突破性进展后,业界对先进节能逻辑技术的需求持续增长[1]。' b3 u& p) W6 O2 F, T0 B

asensnvtyga6401668514.png

1 F3 \. o+ r1 j! M0 l2 L

1 F3 \. o+ r1 j! M0 l2 L

justqvki5l36401668614.png

3 p3 n: H9 [# a% x3 `# ?图1:展示了从28纳米到N2的每平方毫米性能/功耗比提升,显示了跨技术节点超过140倍的节能计算加速。

# J$ I' n- u7 l* O Q

' L, I: F0 W0 ]+ `' v/ EN2技术在半导体制造领域代表显著进步,采用了节能型环绕栅纳米片晶体管、优化的中端及后端互连,以及业界最高密度的SRAM宏单元,达到约38Mb/mm2。与前代3纳米制程相比,N2带来显著提升:速度提高15%或功耗降低30%,同时芯片密度提升超过1.15倍。

: U/ A4 @. v& `: n, B

$ J/ t w% J! [! L7 F5 \1

" o6 a( Z& F0 O, Z: W0 _# TN2 NanoFlex技术架构1 c) s, R+ B" _

N2平台技术引入创新的NanoFlex方案,通过纳米片宽度调制和多单元架构提供灵活的设计选择。该技术的开发重点关注PPACt(功耗、性能、面积、成本和上市时间)各项指标。

6 K- e# l7 }# z4 F. f6 f

3nd2z1on1yh6401668715.png

, p8 V4 h1 t' S5 d9 A5 A6 f

, p8 V4 h1 t' S5 d9 A5 A6 f

图2:展示N2 NanoFlex技术通过结合短单元和高单元库实现超过15%性能提升。* u7 y5 |1 r! H3 i

8 b- z, P2 N$ f

r4aekzoftwa6401668815.png

$ X) t* C2 Z# k

$ X) t* C2 Z# k

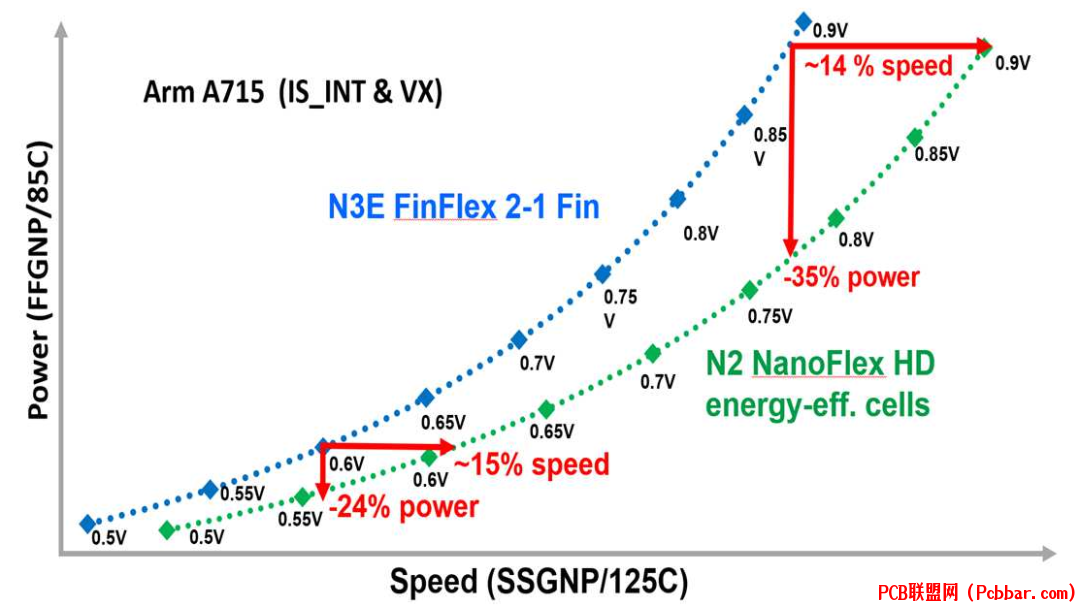

图3:对比N2 NanoFlex HD单元和N3E FinFlex单元的性能,显示在各种电压范围内实现14-15%的速度提升。

/ _' E9 @! `$ q" S, A" {& _0 Z% m7 ^* L4 B* a

该平台提供跨越200mV的六档阈值电压解决方案,使设计人员能够针对不同功耗和性能需求进行优化。这种灵活性对于满足各类节能计算应用需求具有特殊价值,同时保持最佳逻辑密度。

( y) b4 \$ h+ A. h$ ~$ ~4 i

# B4 Q3 P2 N! c" W2 f2 b( u" {6 L9 o* {

节能型纳米片晶体管与互连技术

6 E6 b9 }6 _0 q9 L5 q# sN2平台标志着从FinFET到纳米片技术的成功转型。这一发展历程包括多代Si FinFET技术,从16纳米发展到7纳米节点。9 i) D. V+ J4 |, A5 m) d+ `9 m( v! w

nfsy5d4ii3v6401668915.png

# d. F8 P; M4 F" x: C1 [图4:展示N2晶体管特性,呈现优异的漏致势垒降低(DIBL)和亚阈值摆幅性能。: q/ J. A( P# U+ i7 N

* m3 k) [6 {' u( p% d2 F4 I# p8 @

aflkyunpzaf6401669015.png

8 ]4 T3 |; J# O图5:展示跨越约200mV的六档阈值电压范围,针对低漏电和高性能应用进行优化。

! O" W' [) m4 j$ R% q) G

4 \& k4 V2 |5 k) V# y' f2 W/ @: }纳米片晶体管在性能指标上展现显著改进。该技术分别在N型和P型场效应晶体管上实现70%和110%的I/CV速度提升。特别值得注意的是在低电压工作条件下(0.5V-0.6V)性能功耗比得到提升。6 M0 d8 c' G2 L/ h

0v4wu54ldtk6401669115.png

& q5 i+ C8 y2 o" w

& q5 i+ C8 y2 o" w

图6:比较驱动电流和迁移率提升,显示N型和P型晶体管在I/CV速度上的显著改进。2 _& n& t/ n- ~( L/ L9 P

~7 {/ E1 b5 p* E9 s3

" i4 C" A+ k. ?7 ^& a" d" s& Z5 \与3D Fabric技术集成% z* O& D4 _; X9 b+ n9 H+ ?$ \4 u a. x

N2平台的主要创新在于与3D Fabric技术的无缝集成。该平台包括新型铜质重分布层(RDL),具有平坦钝化层和硅通孔(TSV),针对系统集成和扩展进行了优化。

$ X% q. s1 C' V* a

5k3qvs55ndl6401669216.png

- l, A; h, {. t/ M7 E7 t图7:展示N2与3D Fabric技术的集成能力,显示新型铜RDL和钝化层结构。! n6 Q8 Z. ?- Z7 W1 A( ?5 _: h( @

; k( c, `4 V% w% i1 s该技术专门设计用于支持先进封装解决方案,包括SoIC(集成芯片系统)3D堆叠和各种CoWoS(晶圆级芯片堆叠)变体。这种集成能力对加速人工智能、移动设备和HPC产品设计的系统集成和扩展具有重要作用。

, c7 N1 V1 |2 r! s- g0 K* v8 S" g: y' _6 {0 `

4

4 v4 V1 h- G1 P3 f& ?$ ]: ySRAM与逻辑性能- G* m1 |! P* K3 C

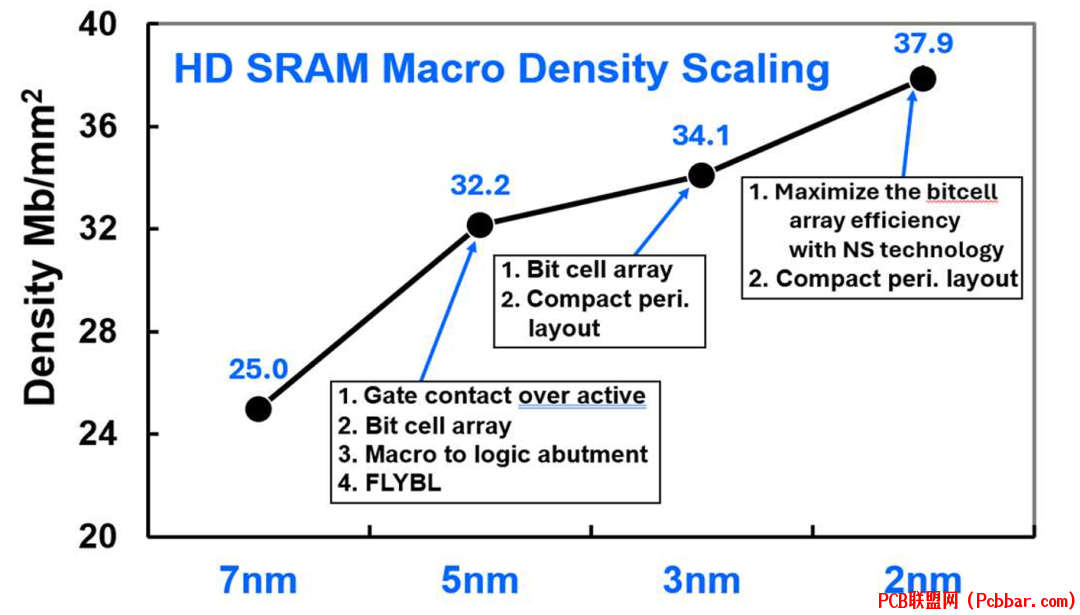

N2平台在SRAM密度扩展方面取得显著成果,达到约38Mb/mm2。这一提升来自位单元阵列效率和外围布局的多项优化。

+ k8 C3 B0 i P4 V' |0 y

i2khmo1302j6401669316.png

3 `& p M1 Z) q* G- O图8:展示从7纳米到2纳米的SRAM宏单元密度扩展,N2达到约38Mb/mm2。" g. z1 B0 {$ ?5 E9 J7 _

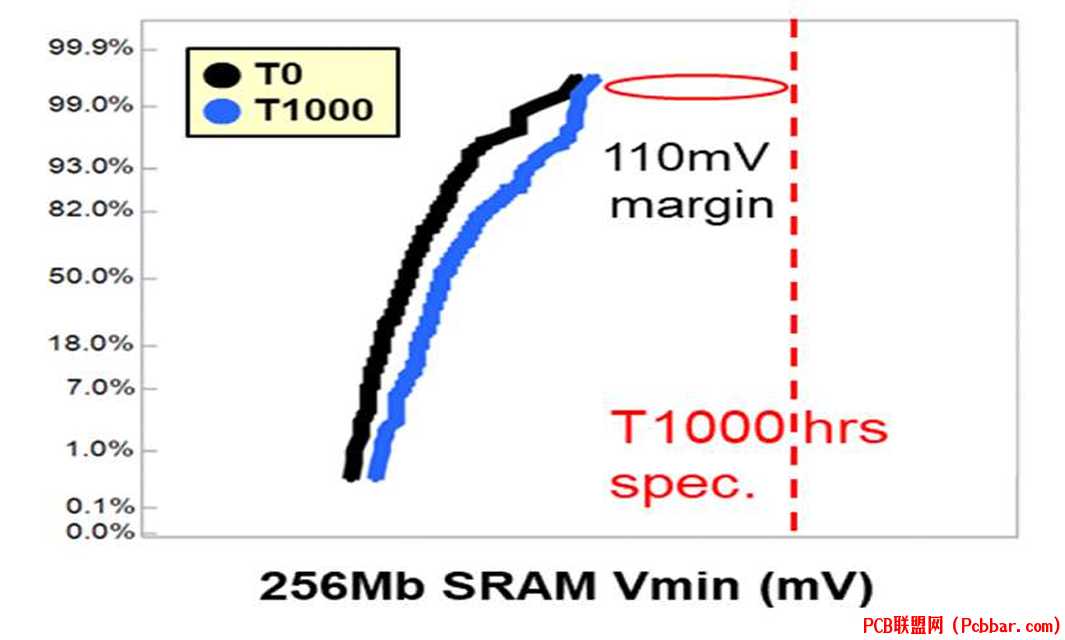

: Z8 ~' L7 C( H该平台展现了可靠的稳定性和性能特征。256Mb SRAM显示稳定的高良率,不经修复即可达到超过80%平均良率和90%峰值良率。该技术成功通过了1000小时高温工作寿命(HTOL)认证,具有约110mV裕量。

# d: P$ A( n8 R1 k2 E

eiof4orzwbi6401669416.png

0 X% s2 p9 u) K6 b& X9 l% ?, A$ I图9:可靠性测试结果显示N2技术满足晶圆级可靠性要求并通过1000小时HTOL规范。$ y$ |% n$ e8 q* t# U' e5 R

% O; A" J6 q( I# M( u8 LN2平台目前处于风险生产阶段,计划于2025年下半年开始量产。增强版本N2P在保持完全GDS兼容性的同时提供5%额外速度提升,计划于2025年完成认证,2026年实现量产。

# X A' e4 I, G* s# `3 ]9 U3 I7 X+ n0 V" L& _ k" W! s! h

参考文献1 B0 [* b" x2 _+ y% H) B

[1] G. Yeap et al., "2nm Platform Technology featuring Energy-efficient Nanosheet Transistors and Interconnects co-optimized with 3DIC for AI, HPC and Mobile SoC Applications," in 2024 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2024, pp. 1-4.7 U$ e3 s7 R! j( L9 Z- x9 E7 S

END

- {8 u5 i( _- C0 ]9 V9 |" z" f! h* l1 [3 |5 U( [

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

* T. l, d8 L) R3 F9 P v0 {+ }) x点击左下角"阅读原文"马上申请

6 l0 a+ F4 i7 ~

& X% X' K" N6 Z }1 r, |3 x欢迎转载

3 F% f! j: i* x) a ]7 F; z4 T( ]6 V

转载请注明出处,请勿修改内容和删除作者信息!

% g, q- {# c2 X; u4 @4 J- e. j5 w- w6 s

/ `4 U& n" u" Y+ x

# S% I0 p/ t7 o! J9 |

akb0nibksii6401669516.gif

_$ ]' ]: f/ ~ @

% J& H. Q# Y6 L$ u; ]3 d/ M2 J' r' R关注我们

7 \5 Z, v5 X* _- @6 z6 ~7 ^6 l, l8 H" d) p0 x7 J" r

2 Q7 r: U- X5 z( g3 c5 C

frskxzwqi5f6401669616.png

* C' r) P8 s! a! `: I

* C' r) P8 s! a! `: I

| $ s, H9 m! d, f* h: G

wtt1gxq4x5c6401669717.png

2 q% Z- O1 [- u* V9 Z/ T/ A Z! E | . q8 B* l2 q& V

a2ylh0alqh26401669817.png

) m: p* X: l Y4 Y

) m: p* X: l Y4 Y

|

0 w9 \4 m! t; `. F5 k" w% _# q5 {6 X6 q( v( o# B, F ?

, w. ~( v, a, M6 l

" p1 V: m9 j, {

关于我们:

1 e1 k! S. x; q6 K4 }/ k( d深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。! X9 h+ i9 g* U+ L9 L4 U

A8 s- n$ z* B7 x- D* Rhttp://www.latitudeda.com/# S) C- l7 P6 s

(点击上方名片关注我们,发现更多精彩内容) |

|