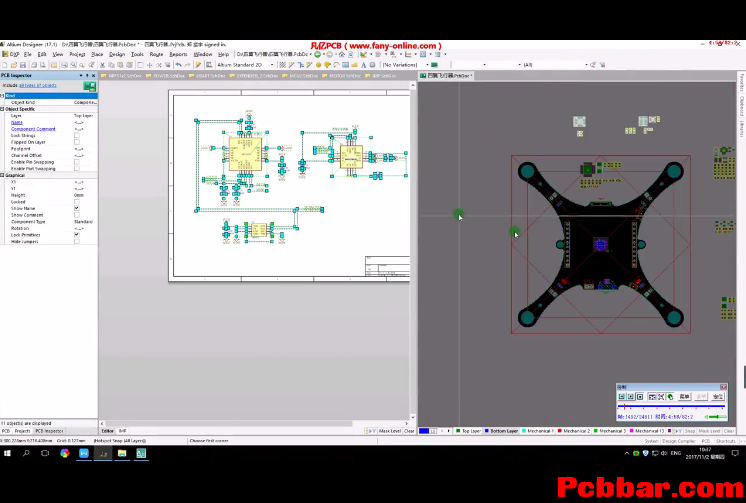

Altium designer 四层 pcb设计速成实战视频 凡亿PCB

视频链接:https://item.taobao.com/item.htm?spm=a1z10.3-c-s.w4002-21870448573.9.751e7d4aOdG3Iv&id=594484273562

4层PCB进阶教程,全程手把手教学,完整实操案例,6+1技术指导支持,真实案例+全程实战+技术支持,15天速成高速pcb设计高手教程。

此课程包括:

第一部分 原理图

1.1、原理图的模块简介

1.2、原理图的编译与检查

1.3、原理图的导入

第二部分 PCB设计前期处理

2.1、PCB常用参数设置

2.2、PCB的叠层及阻抗

第三部分 布局

3.1、模块化布局

3.2、菊花链(fy-by)拓扑结构的分析及布线规划

第四部分 布线

4.1、CLASS及常用规则的创建

4.2、PCB的扇孔处理

4.3、SDRAM的布线

4.4、Flash的布线

4.5、排针的布线

4.6、走线联通性处理及电源分割4.7、SDRAM的蛇形等长

4.8、菊花链(fly-by)的蛇形等长

第五部分

PC B的后期处理

5.1、走线优化及常规规避emc的一些做法

5.2、丝印调整及常见DRC检查

5.3、Gerber及生产资料的输出与整理

[size=0.83em]AD 4层6.jpg (286.68 KB, 下载次数: 0) [size=0.83em]AD 4层6.jpg (286.68 KB, 下载次数: 0)

下载附件 [url=]保存到相册[/url]

[color=rgb(153, 153, 153) !important]20 分钟前 上传

布局布线要求 1)所有的显示接口(不论采用的是接口或者FPC)尽量放在板边,方便插拔; 2)主芯片与显示接口的位置不要放的太远,尽量缩短走线的距离,走线属于高速高速信号; 3)走线拐角尽量用圆弧或者钝角,不能为直角或者锐角,需要保证阻抗的连续性; 4)LVDS的信号线需要严格遵守差分规则来走线,要求阻抗为100欧姆,误差控制±10%。差分对内的误差需要控制在5mil,差分对间的误差控制在100mil,差分等长走线方法可以参照前文差分的绕线方法; 5)MIPI、EDP的信号线需要严格遵守差分规则来走线,要求阻抗为100欧姆,误差控制±10%,差分对内的误差控制在5mil,差分对间的误差控制在30mil。 6)MIPI/LVDS网络的总长度,包括PCB走线长度、FPC连接线长度、接收端PCB走线长度,尽量控制在10inch以内,最长不要超过了15inch,不然信号质量会受到影响; 7)EDP网络的总长度,传输速率在2.7Gbps以下的,尽量将走线控制在10inch以内,如果有要求传输速率在5.4Gbps的信号,将走线长度控制在5inch以内; 8)为了抑制电磁辐射,MIPI、LVDS、EDP等高速信号的差分线尽量走线内层,靠近GND平面的走线层来走线,保证走线不要跨分割,否则会造成差分线阻抗的不连续性和增加外部噪声对差分线的影响,如果是走在表层,尽量包地处理或者拉大跟其它信号的间距,保证20mil以上; 9)MIPI、LVDS、EDP等高速信号的差分线尽可能的减少过孔换层,过孔会造成线路阻抗的不连续,如果需要打孔换层来走线,保证差分过孔的一致性,以及在换孔位置就近安排一个回流地过孔,以用于信号回流。 以上要求布局布线要求,尽可能的严格处理实施,如图4-32。

|