8层Altium designer 18/17 HDI盲埋孔pcb设计课程 凡亿pcb视频

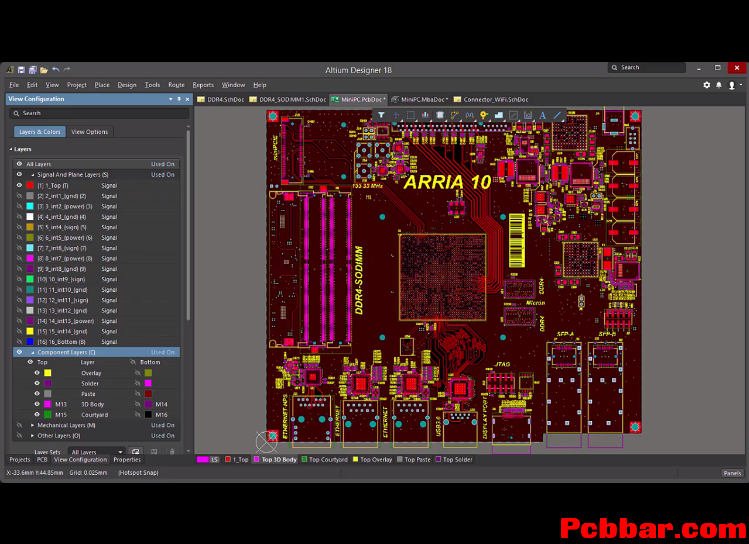

此套视频通过案列飞行控制板的0.4MM、0. 5MM,0.8MM BGA的讲解1阶、 2阶埋孔孔出线以及通孔的BGA的出线方式,不再是常规走线的方法。同时案例也是一个完整的工控板,包含各类型的PCB模块,如经典的DDR、PMU. DCDC等,包含高速单端走线、高速蛇形走线、高速差分蛇形走线、平面分割等布线要点。庖丁解牛的方法,从局部到整体,系统化、综合性的学习整个PCB的设计!你如果正在想方设法进阶你的PCB设计技能,那么你选择这个视频不会有错,你想学的我们都会教你,即使视频中没有讲解完善的我们售后技术支持也给你讲得明明白白,讲得你服为止!

布局布线要求 1)所有的显示接口(不论采用的是接口或者FPC)尽量放在板边,方便插拔; 2)主芯片与显示接口的位置不要放的太远,尽量缩短走线的距离,走线属于高速高速信号; 3)走线拐角尽量用圆弧或者钝角,不能为直角或者锐角,需要保证阻抗的连续性; 4)LVDS的信号线需要严格遵守差分规则来走线,要求阻抗为100欧姆,误差控制±10%。差分对内的误差需要控制在5mil,差分对间的误差控制在100mil,差分等长走线方法可以参照前文差分的绕线方法; 5)MIPI、EDP的信号线需要严格遵守差分规则来走线,要求阻抗为100欧姆,误差控制±10%,差分对内的误差控制在5mil,差分对间的误差控制在30mil。 6)MIPI/LVDS网络的总长度,包括PCB走线长度、FPC连接线长度、接收端PCB走线长度,尽量控制在10inch以内,最长不要超过了15inch,不然信号质量会受到影响; 7)EDP网络的总长度,传输速率在2.7Gbps以下的,尽量将走线控制在10inch以内,如果有要求传输速率在5.4Gbps的信号,将走线长度控制在5inch以内; 8)为了抑制电磁辐射,MIPI、LVDS、EDP等高速信号的差分线尽量走线内层,靠近GND平面的走线层来走线,保证走线不要跨分割,否则会造成差分线阻抗的不连续性和增加外部噪声对差分线的影响,如果是走在表层,尽量包地处理或者拉大跟其它信号的间距,保证20mil以上; 9)MIPI、LVDS、EDP等高速信号的差分线尽可能的减少过孔换层,过孔会造成线路阻抗的不连续,如果需要打孔换层来走线,保证差分过孔的一致性,以及在换孔位置就近安排一个回流地过孔,以用于信号回流。 以上要求布局布线要求,尽可能的严格处理实施。

|