此视频是专门针对DDR3设计来的,采用飞思卡尔IMX6主控芯片, 4片DDR3同层设计,采用DDR3常见的T点拓扑结构,一个大T点两个小T点的方式

讲解了DDR3设计的信号class分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然, DDR3的设计看上去是很高大上的,但是只需要弄懂其中的几个基本要点,也很简单的。本视频采用的8层板设计,也是大家学习多层板的利器,这个视频我们有专门录制叠层的视频教程免费赠送,主要讲解怎么叠层,怎么计算阻抗,差分走线、单端走线线宽怎么设计等等。配合我们的高速设计使用,方便大家更系统的掌握高速PCB设计。

1、掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程

2、掌握DDR3设计的知识要点3、掌握3W原则的PCB设计

5、掌握蛇形等长走线,阻碍线的使用6、掌握叠层阻抗计算的方法

1、原理图( orcad )与PCB同步及前期处理

[size=17.1429px]先回顾一下什么是T-Branch:

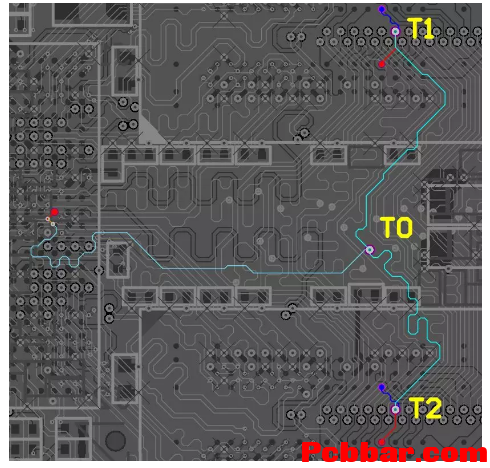

上图是典型的T点结构,四片DDR上下各两片,分别在顶层和底层。 信号从CPU的Memroy interface出来之后到过孔T0进行分叉,支路通过T1,T2的扇出过孔后最终连接到Memory芯片的Pad T3,T4,T5,T6。 T1-T3 = T1-T4 = T2-T5 = T2-T6

[size=17.1429px]Allegro VS Altium

[size=17.1429px]看到这儿,使用Allegro的同学们笑了,这不是很简单吗?可以把T0、T1、T2定义为虚拟T点,然后创建一系列的Pin Pairs。在CM中定义规则后进行线长调制。 [size=17.1429px]使用Altium的小伙伴们却一脸茫然,T0~T6不都属于同一个网络(Net)吗?AD怎么对同一网络的不同分支调等长?资深的AD用户可能会想到"From-To"对象,但是很遗憾,"From-To"有一个非常致命的Bug,在复杂的板子中(随机现象,不知道原因),在PCB面板中的From-To Editor中计算出来的Routed长度经常是“0”,也就是无法查看Pin-Pair之间的layout长度,当然对于线长规则(Matached Net Length Rule)也无效,更不用说利用规则来调制线长...当然From-To还有个很麻烦的地方,其对象必须是器件的Pad,对于自由的过孔或焊盘来说,无法定义From-To,这对于T点拓扑来说显得非常麻烦。 [size=17.1429px]简单来说,xSignal就是升级版的From-To,和Allegro的Pin Pairs管脚对差不多,但是又支持类似"X-Net"的结构,可以计算夸端接电阻(不同网络)的信号长度。但是......xSignal也继承了From-To的缺点,无法对自由的过孔或焊盘进行定义......这点在实际使用中极其不变,希望Altium可以在将来的版本中改进。 [size=17.1429px]不过无论如何,Altium终于有了趁手的工具来做T-Branch的线长调制了。 [size=17.1429px]去DRAM_A0网络做为参考: [size=17.1429px]

[size=17.1429px]其中T0是第一个过孔,T1和T2为DDR扇出的过孔。T0、T1、T2不属于任何器件,属于自由过孔。 [size=17.1429px]将自由过孔做成器件(封装) [size=17.1429px]之前提到了,xSignal不支持Free Pad/Via,无奈之下,只能将自由对象做成一个器件: [size=17.1429px]

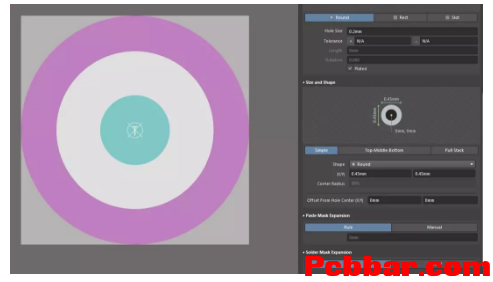

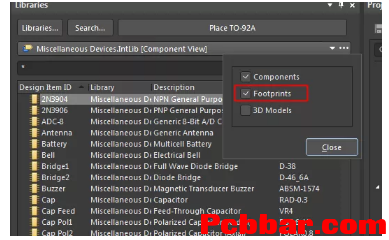

[size=17.1429px]千万注意,做封装的时候务必使用Pad,不要用Via,否则器件放置到PCB上无法设置网络,也没法别识别为“管脚”,也就不能进行xSignal的定义。 [size=17.1429px]Pcblib制作完成后直接加载到库面板,记得在下面的位置勾选“Footrpint”,不然无法看到单独的PCBLib库: [size=17.1429px]

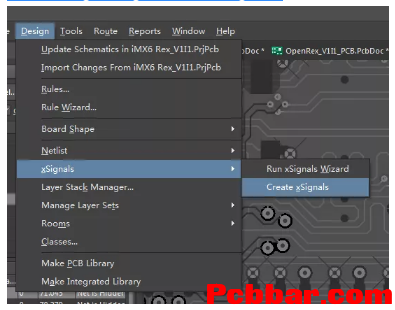

[size=17.1429px]然后将器件T0、T1、T2分别放置到正确的位置。 [size=17.1429px]创建第一层Pin Pair(T0-T1=T0-T2) [size=17.1429px]首先来创建第一层的PP,做T0-T1及T0-T2的等长。 [size=17.1429px]点击菜单Design 》xSignals》Create xSignals: [size=17.1429px]

[size=17.1429px]在源器件中筛选出T0,目标器件中筛选出T1、T2(同时选中),然后点击"Analyze"进行分析: [size=17.1429px]创建第二层Pin Pair [size=17.1429px]第一个分支的PP已经创建完成,接下去创建第二层的PP,即T1-T3 = T1-T4 = T2-T5 = T2-T6。由于T1、T2是两个T点,因此需要创建两次。这里T4对应的芯片U4、T3对应的芯片U5、T1对应芯片U2、T2对应芯片U3(抱歉顺序有点乱)。 [size=17.1429px]首先创建T1的PP,源器件选择T1,目标器件同时选中U4、U5,然后Analyze: [size=17.1429px]又成功创建了PP3、PP4,将这两个xSignal放到Class T-Level_2中。 [size=17.1429px]再次创建T2的PP,源器件选择T2,目标器件同时选中U2、U3,然后Analyze: [size=17.1429px]成功创建PP5、PP6,将这两个xSignal也放到xSignal Class T-Level_2中,和PP3、PP4在同一个Class中。因为后续这4个PP需要做等长。 [size=17.1429px]打开Class编辑器,确认一下我们创建的xSignal Class是否正确: [size=17.1429px]当然,我们也可以在xSignal创建完毕之后,手动在Class Explorer中调整xSignal属于的类。 [size=17.1429px]xSignal(或者说PP)创建完成后,就可以设置规则了。在Highspeed分类中找到Matched Net Length规则: [size=17.1429px]在Query框中输入需要定义规则的对象:InxSignalClass('To_Level_1'),也就是为T0-T1、T0-T2这对PP定义匹配线长规则。在Tolerance中输入允许的误差,完成规则定义。 [size=17.1429px]同样的,可以为xSignalClass T_Level_2定义一个线长匹配的规则。 [size=17.1429px]布线并进行线长调制 [size=17.1429px]先用直线进行正常的布线,完成后可以使用命令Route》Interactive Length Tuning命令进行蛇形线的调制: [size=17.1429px]将鼠标移至需要调制的网络Branch,根据规则约束进行线长的调制: [size=17.1429px]在Length Tuning过程中,可以使用Tab打开面板或快捷键1,2,3,4,逗号,句号来设置调制的样式: [size=17.1429px]查看xSignal(PP)长度 [size=17.1429px]完成线长匹配后,可以在PCB面板的xSignal中查看布线的PP长度。 [size=17.1429px]在xSignal出现之前的AD中,只有Routed Length可以用来查看布线长度。如果网络中的节点超过3个,Routed Length也就无能为力了。xSignal几乎完美地解决了这一问题。 [size=17.1429px]

|