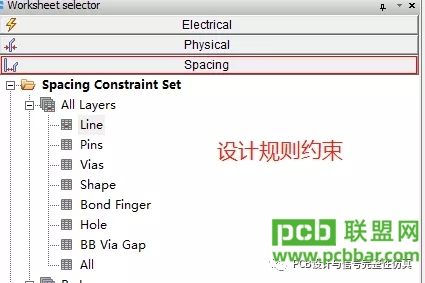

layout中对于走线最基础的关注点是阻抗和串扰。对于阻抗,在开始设计PCB之前,我们会计算出满足阻抗要求的单端走线以及差分线等。对于串扰则是通过设置走线与走线之间的间距。这两者我们都会在设计的时候将参数填写到规则管理器中进行布线约束。

但实际设计中通常不能完全遵守设计规则,比如在Fanout区域需要降低走线线宽等,这也是区域规则存在的原因。除了这种由于设计条件的限制造成的设计偏差,也有一些是设计者本身的疏忽造成的,比如走线存在垮分割、走线贴着参考平面边缘以及本身规则设置不完善导致有线宽或是间距的变化,进一步还有阻抗的变化引起串扰的变化等。

这些设计上的疏忽会导致阻抗或是串扰量的变化,而这种变化单凭设计者本身依靠经验去检查很容易就出现疏漏。这个时候可以借用仿真工具Sigrity中的走线阻抗耦合检查工具快速对指定信号或是整版信号进行检查。

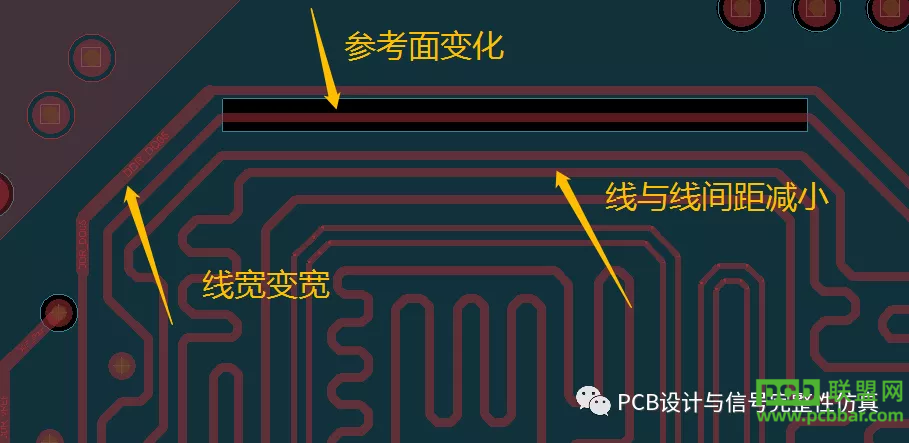

为了演示软件功能,在这里准备了一个DEMO板,并对DEMO板做一些修改。这些修改包括局部挖空参考面(模拟跨分割)、线宽变化(模拟阻抗变化)、线间距变化(模拟耦合度变化)。

DEMO板准备好之后就开始仿真。

新规矩,流程走一遍。

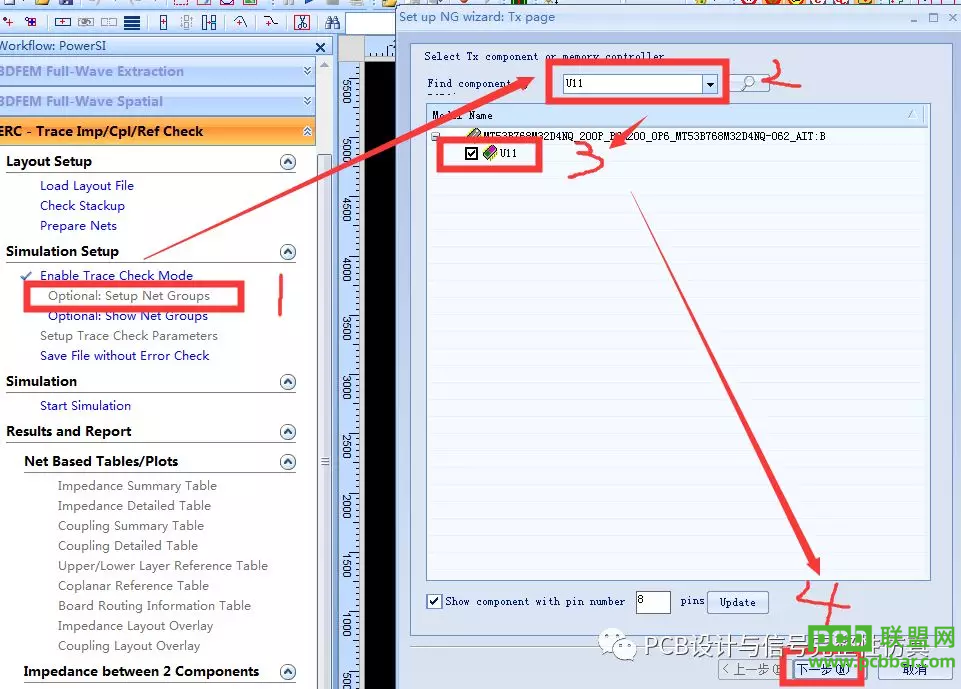

进行阻抗耦合检查的功能块在PowerSI中,启动之后加载PCB文件(DEMO是allegro的PCB,可以直接打开),使能Trace Imp/Cpl/Ref Check。 检查层叠是否正确,如果不正确,需要手动修改。Sigrity会读取PCB文件包含的层叠信息,但并不总是正确读取的,有时候会出现错误,需要核对一下。 软件中可以选择对整版信号进行仿真,也可以选择对指定信号进行仿真。这里我们只选择刚刚处理过的信号进行仿真,也就是主芯片U12到DDR颗粒U11的信号。

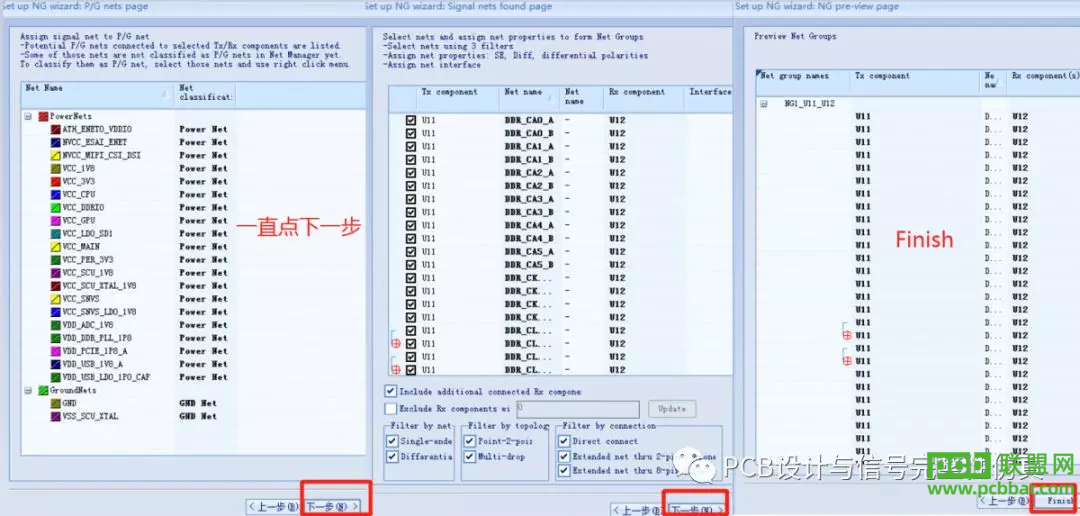

流程为点击设置网络分组(Setup Net Groups),在弹出的对话框中搜索U11(设置为TX器件),然后在搜索结果中勾选U11,点击下一步,这样TX部分的设置就完成了

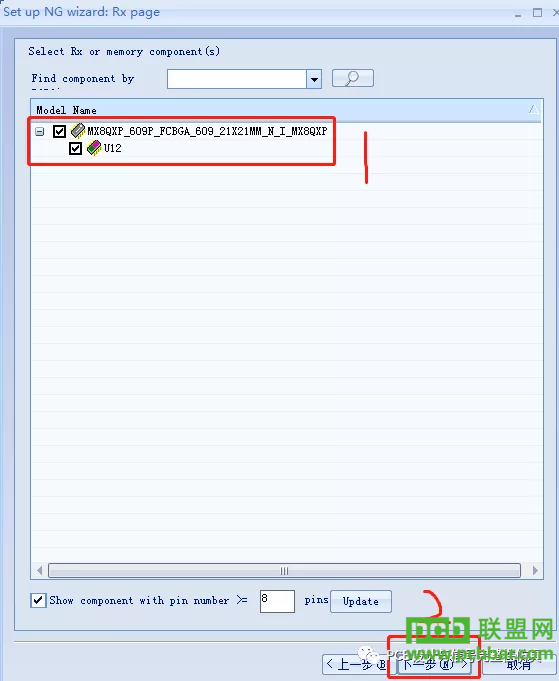

软件会自动进入到RX的设置,由于我们的内存颗粒只和主控IC连接,所以这里只有一个U12可以选择,勾选之后下一步。

接下来设置电源和GND网络,设置后这些网络不会参与到阻抗的计算中,设置与否对结果没太大影响,直接下一步进入到仿真网络的选择,这里可以选择感兴趣的网络进行仿真,也可以全选,直接下一步,最后会让对参数设置进行确认,点击Finish完成设置。(此次流程中这几步的设置都比较粗糙,这是由于做这个仿真计算速度很快,没必要精细化的分组处理。当然如果有需求也可以进行详细的分组设置。)

最后

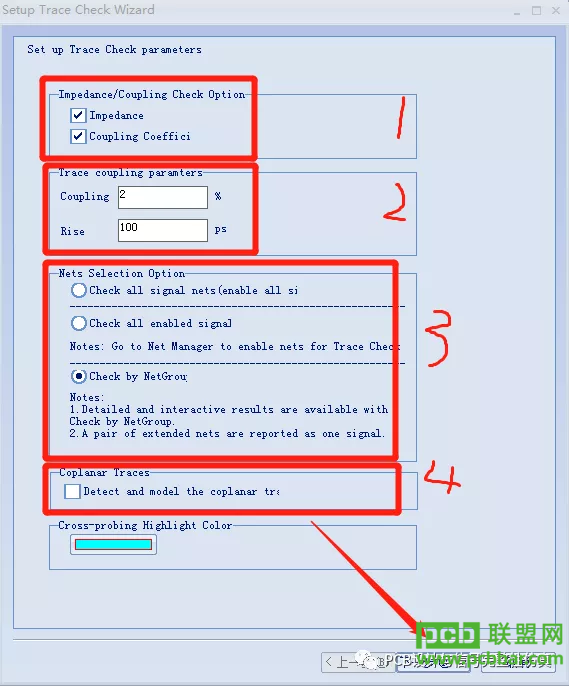

需要设置的是仿真的约束条件,点击Setup Trace Check Parameters进入设置菜单,第一步需要设置检查项,这里选择阻抗与耦合都进行检查。第二步设置耦合参数,在这个参数之下的耦合量都会被系统忽略。第三步设置需要仿真的网络,这里选择我们刚刚设置的分组。第四步,如果有共面阻抗之类的,可以勾选 Colanar Traces的选项。

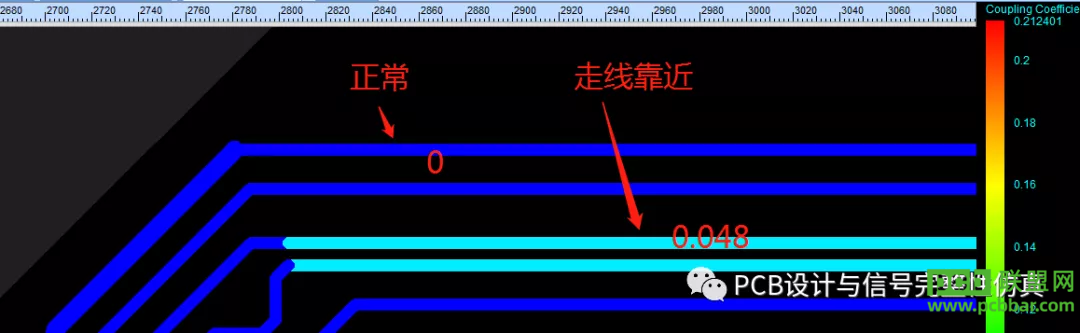

鼠标移动到走线上会显示具体的阻抗,从上面可以明显看到我们加宽线宽的走线以及挖掉最近参考层的走线和正常走线相比有明显的偏差。 查看耦合度可以通过Coupling Layout Overlay显示,这里也可以看见将走线间距改小之后耦合度增加。 有两点需要注意:第一个是这个功能计算出来的阻抗和SI9000会有一点偏差。第二个是其耦合度检查只能检查同层之间的耦合,对于不同层之间的耦合还无法进行检查。不过在绝大多数的设计中,现有的这个功能已经够用了,通过这个方式可以非常快速的对整版或是重点关注的信号进行阻抗及耦合的检查,找到设计的薄弱环节进行整改。

来源:公众号:pcb设计与信号完整性 作者:十四

---------------------------------------------------------------

每天学习一个技巧,日积月累你也是专家!

使用前请您先阅读以下条款:

1、转载本站提供的资源请勿删除本说明文件。

2、分享技术文档源自凡亿教育技术验总结分享!

3、表述观点仅代表我方建议,不对直接引用造成损失负责!

--------------------------------------------------------------

更多技术干货文章推送,请关注 凡亿PCB 公众微信号!

|