Tcl脚本简介

Tcl——Tool Command Language(读作tickle),诞生于80年代的加州大学伯克利分校,作为一种简单高效可移植性好的脚本语言,目前已经广泛应用在几乎所有的EDA工具中。在Xilinx最新的FPGA设计工具Vivado中,Tcl成为唯一支持的脚本。

使用Tcl脚本的优势如下:

- 能快速生成Vivado工程及编译工程,生成工程所需要的PL端bit文件;生成工程之后,根据自己的需要,可手动创建Block Design,或者在脚本添加IP、实现自动连接等功能。总而言之,Tcl的引入,使得Vivado设计过程也变得可编程控制,设计流程变得更加灵活多变。

- 在开发的过程中,直接打开Vivado软件,可视化地进行Block Design设计、配置IP和连线等。但是这样手动添加IP或者连线需要花一定的时间,且编译步骤重复累赘,因为打开了Vivado这个占用电脑资源比较大的软件,导致生成需要的bitstream文件需要花费大量时间。使用脚本可以快速的在Vivado 2017.4 Tcl Shell(Vivado自带的shell终端窗口)执行Tcl脚本命令,无需要打开Vivado软件就进行编译生成bit文件,花费的时间极大的缩短了。

- 如需修改工程的Block Design文件,可以打开Vivado进行修改或者直接修改Block Design Tcl脚本,所有的Block Design设计,Vivado都会自动保存成Tcl脚本文件。​​​​​​​

基于TcL脚本生成Vivado工程

- Windows 7/10 64bit;

- Xilinx Vivado 2017.4。

表 1

由创龙提供的FPGA开发例程位于光盘Demo目录下,本文以创龙TLK7-EVM开发板为实验平台,以tl-led-flash例程为例,演示使用Tcl脚本生成Vivado工程及编译的开发步骤。 将Demo目录下的tl-led-flash例程复制到Windows非中文路径下,例如复制到C盘根目录。Vivado工程目录结构及文件说明见下表,表格中的xxx代表具体的例程,例如 tl-led-flash例程。Vivado工程的bin文件夹下存放适用于创龙各开发平台运行的可执行文件,src文件夹下包含constraints、hdl和scripts目录。 注意:Windows路径有长度限制,路径太长会导致出错。 表 2 | | | | | | | | | | | | | | clean.sh

clear_project.tcl | |

使用TcL终端打开Tcl脚本

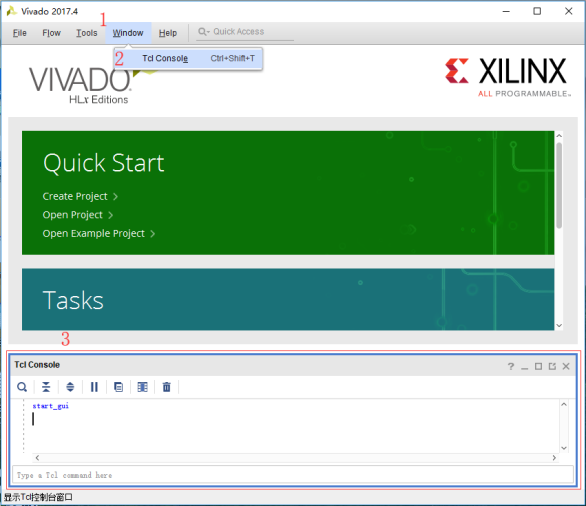

打开Vivado软件,点击菜单栏"Window->Tcl Consonle"打开Tcl控制台窗口。 ​​​​​​​

在Tcl控制台窗口执行如下指令(注意指令中"/"符号的方向),进入需要执行的Tcl脚本所在路径,该脚本文件用于生成tl-led-flash例程的Vivado工程。 Vivado% cd C:/tl-led-flash/src/scripts ​​​​​​​生成Vivado工程

进入xxx_project.tcl脚本所在路径,执行Tcl脚本生成对应平台的Vivado工程。本次操作中生成创龙TLK7-EVM开发板的Vivado工程——tl_led_flash,指令参数解释如下: Vivado%vivado -mode batch -source tl_led_flash_project.tcl -tclargs tlk7-evm xc7k325tffg676-2 - vivado -mode batch:使用vivado的batch模式;

- -source axi_gpio_project.tcl:选中要执行的Vivado工程xxx_project.tcl脚本文件;

-tclargs tlk7-evm xc7k325tffg676-2:修改"-tclargs"参数,即可生成对应开发平台和芯片型号的工程。这里生成了TLK7-EVM开发板,FPGA型号为XC7K325TFFG676-2的Vivado工程。如需要生成TLZ7x-EasyEVM开发板,SoC芯片型号为XC7Z010CLG400-2的工程,则将指令修改为:-tclargs tlz7x-easyevm xc7z010clg400-2。 表 3 | | | | | tlz7x-easyevm xc7z010clg400-2 | | tlz7x-easyevm xc7z020clg400-2 | | | tlz7xh-evm xc7z100ffg900-2 | | | tl5728f-evm xc7a100tfgg484-2 | | | tla7-evm xc7a100tfgg484-2 | | | tlk7-evm xc7k325tffg676-2 | | | tl665xf-easyevm xc7a100tfgg484-2 | | | tl6678f-easyevm xc7k325tffg676-2 |

Tcl脚本执行完成后,Tcl控制台窗口打印信息如下图所示,同时在工程源码"\src\runs"目录下生成对应开发平台的Vivado工程。本次生成了配套于创龙TLK7-EVM开发板的tl_led_flash工程。 ​​​​​​​Vivado工程编译

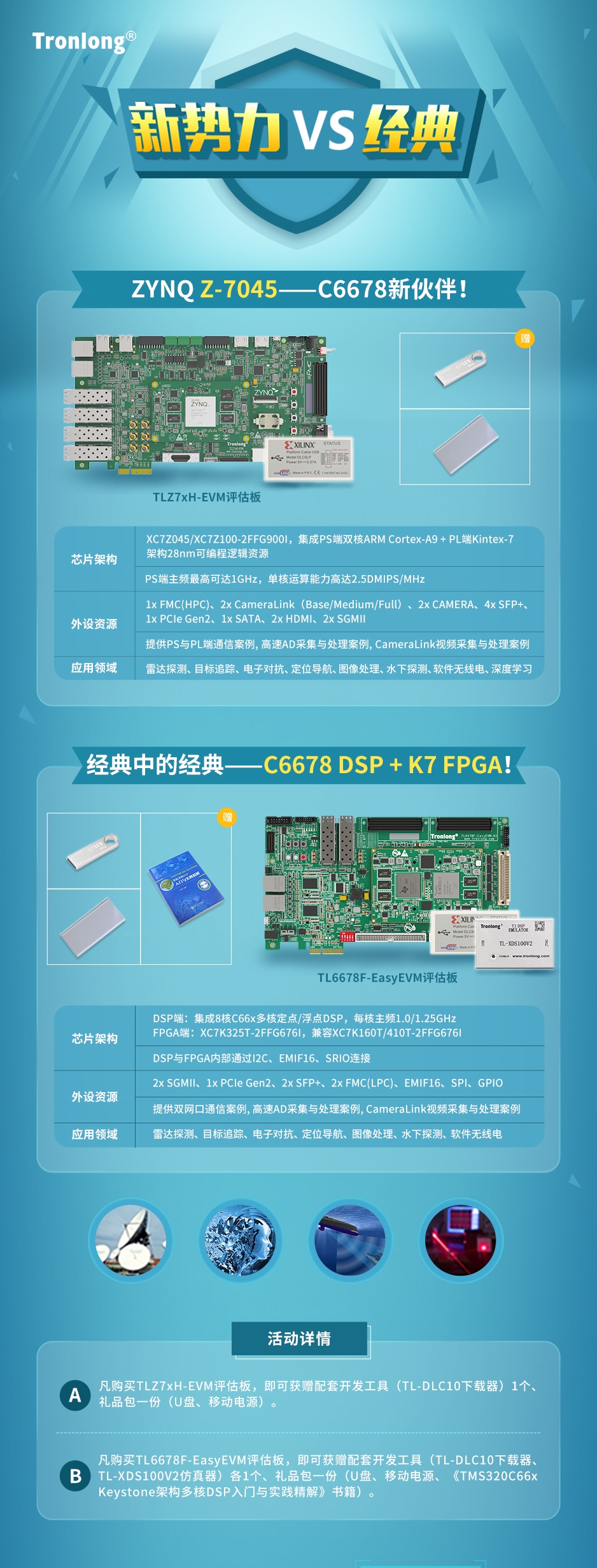

双击Vivado工程"src\runs\tl_led_flash.xpr"文件  ,打开新生成的Vivado工程如下图所示。 点击左边栏PROGRAM AND DEBUG下的Generate Bitsteam选项,弹出对话框中选择Yes选项,如下图所示: 在弹出的Launch Runs对话框中,点击OK开始编译Vivado工程,如下图所示: 用时约6min后,Vivado工程编译完成,实际编译时间跟FPGA工程和PC性能相关。在弹出以下对话框中,点击Cancel完成编译步骤。 编译完后会在Vivado工程"src\runs\xxx.runs\impl_1"目录下生成可执行文件xxx.bit和xxx.bin,如下图所示。其中xxx.bit文件内包含head information,可以通过下载器解析后加载到FPGA核,xxx.bin文件为可执行文件。 为便于测试,我司提供由Vivado工程编译生成的可行文件放于bin目录下,该目录下包含了适用于创龙全部开发平台的可执行文件,将其下载到开发板即可运行测试。 创龙TLZ7xH-EVM是一款基于Xilinx Zynq-7000系列XC7Z035/XC7Z045/XC7Z100高性能SoC处理器设计的高端评估板,处理器集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源,由核心板与底板组成。 ZYNQ Z-7045-C6678新伙伴 TLZ7xH-EVM评估板 芯片架构:XC7Z045/XC7Z100-2FFG900I,集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源。PS端主频最高可达1GHz,单核运算能力高达2.5DMIPS/MHz。

外设资源:1x FMC(HPC)、2x CameraLink(Base/Medium/Full)、2x CAMERA、4x SFP+、1x PCIe Gen2、1x SATA、2x HDMI、2x SGMII 支持PS、PL端通信、高速AD采集与处理、CameraLink视频采集与处理

应用领域:雷达探测 目标追踪 电子对抗 定位导航 图像处理 水下探测 光电探测 深度学习 更多详情请查阅:

①官方网站

②官方TB:广州创龙电子科技有限公司

|