|

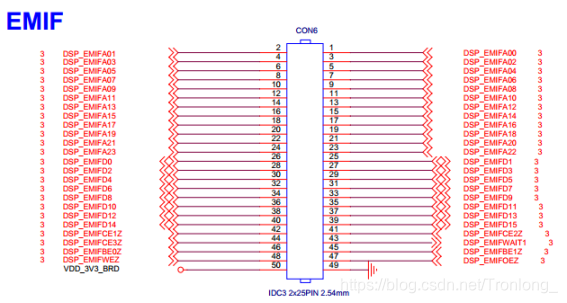

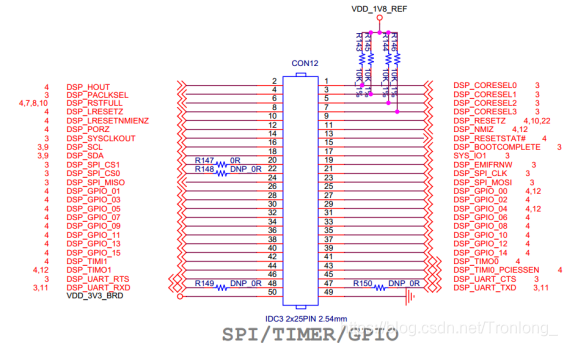

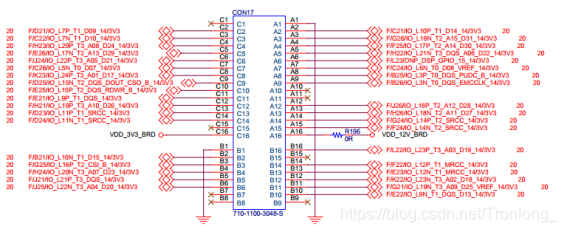

创龙TL6678F-EasyEVM是广州创龙基于SOM-TL6678F核心板而研发的一款多核高性能DSP+FPGA开发板。 广州创龙SOM-TL6678F核心板基于TI KeyStone C66x多核定点/浮点TMS3206678 + Xilinx Kintex-7 FPGA设计的高性能DSP+FPGA高速大数据采集处理器,采用沉金无铅工艺的14层板设计,尺寸为112mm*75mm,经过专业的PCB layout保证信号的完整性,和经过严格的质量管控,满足多种环境应用。 开发板引出3个拓展信号接口(CON6、CON12、CON17)。DSP端2个(CON6、CON12),50pin IDC3简易牛角座,间距2.54mm,含EMIF16、SPI、TIMER、GPIO拓展信号;FPGA端1个(CON17),48pin欧式连接器,GPIO拓展接口。硬件及引脚定义如下图:   ​

图 1 DSP拓展接口   ​

图 2 FPGA拓展接口   ​

图 3 CON6原理图   ​

图 4 CON12原理图   ​

图 5 CON17原理图

|