|

前 言 TL-S6Box是广州创龙基于Xilinx Spartan-6 FPGA设计的高速数据采集处理开发板,采用核心板+底板的设计方式,尺寸为18cm*13cm,它主要帮助开发者快速评估核心板的性能。 核心板采用高密度6层板沉金无铅设计工艺,尺寸为56mm*35mm,引出FPGA全部资源信号引脚,降低了开发难度和周期,以便开发者进行快捷的二次开发使用。 底板采用2层无铅沉金电路板设计,为了方便用户学习开发参考使用,下面引出了各种常见的硬件说明。

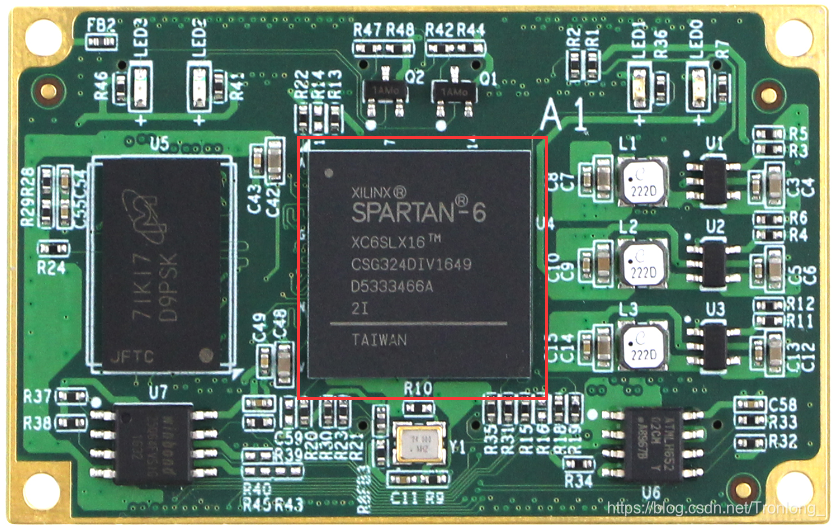

1.CPUXilinx Spartan-6 FPGA

​ 图 1

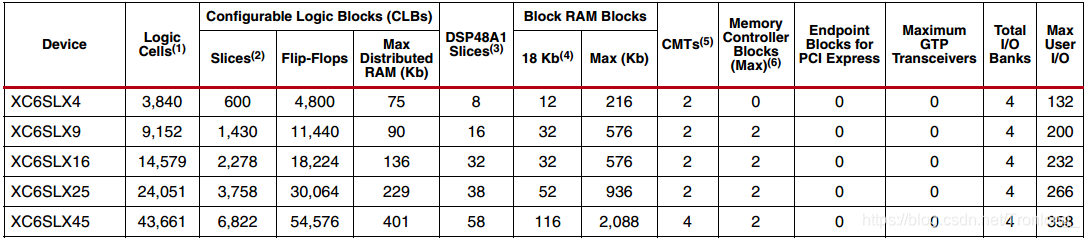

FPGA兼容Xilinx Spartan-6 XC6SLX9/16/25/45,平台升级能力强,以下为Xilinx Spartan-6 FPGA特性参数:   ​

图 2 2.FLASH

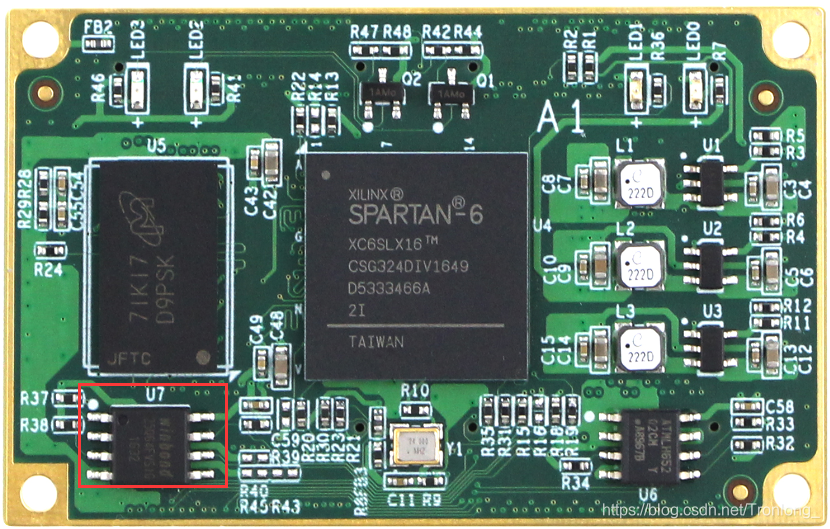

核心板FPGA端采用工业级SPI FLASH,如下图:

​ 图 3

3.RAM核心板FPGA端RAM采用工业级DDR3,如下图:

​ 图4

4.I2C EEPROM核心板的U6是1个I2C总线接口的EEPROM,型号为AT24C02C,容量是256Bytes,如下图:

​ 图 5

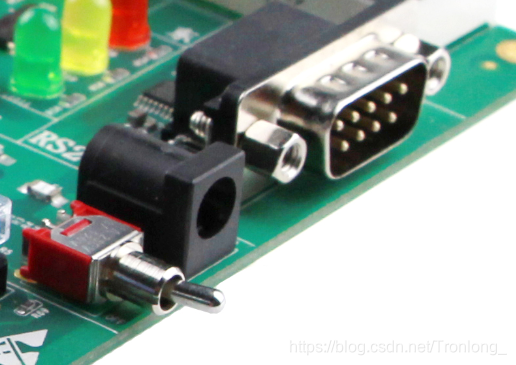

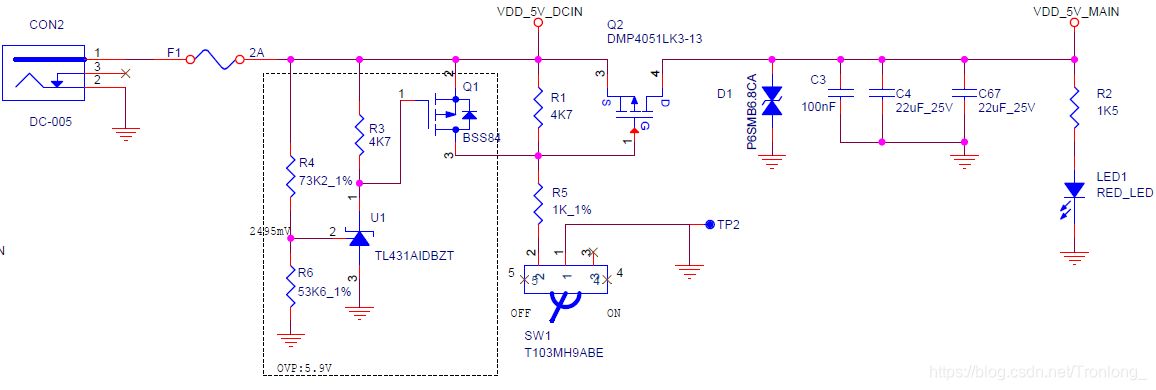

5.电源接口和拨码开关采用5V2A直流电源供电,CON2是电源接口,SW1是电源拨码开关。

​ 图6

​ 图7

6.拓展电源接口开发板底板的J9、J10是扩展电源接口,使用2pin白色端子座,支持3.3V和5V电压输入,引脚定义如下:

​ 图 8

​ 图 9

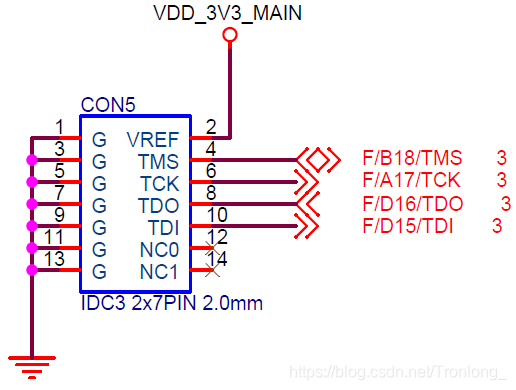

7.Xilinx FPGA下载器接口Xilinx FPGA下载器接口共14pin,2.0mm间距,各引脚定义如下图:

​ 图 10   ​ 图11

|