|

|

1、FPGA与ARM基于I2C通信测试表 1

开发板型号

| 是否支持本实验

| TL437x-EVM

| 不支持

| TL437x-EasyEVM

| 不支持

| TL437x-IDK

| 不支持

| TL437xF-EVM

| 支持

|

本测试程序将FPGA模拟成I2C设备,设备地址为0x2A,ARM使用I2C0总线对此I2C设备进行读写。

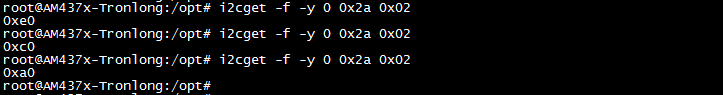

进入开发板文件系统的”/opt”目录,执行如下命令初始化FPGA程序加载功能的管脚。

Target#./set_flash_fpga_pin.sh

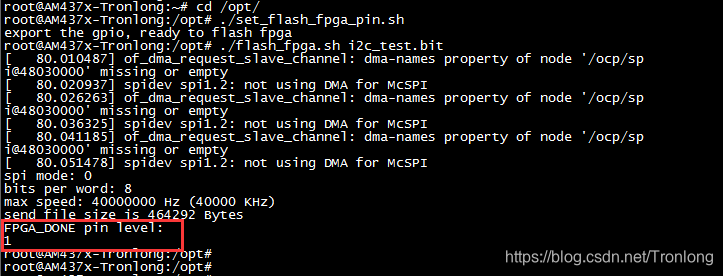

执行如下命令启动FPGA程序加载功能,由ARM通过SPI总线加载.bit文件到FPGA中运行。打印信息中,如果FPGA_DONE的值为1,则表示.bit文件加载成功。

Target#./flash_fpga.sh i2c_test.bit

​

此.bit文件主要实现FPGA和ARM的I2C通信功能,.bit文件、.mcs文件和源码位于FPGA光盘”Demo\app\IIC\”目录下。

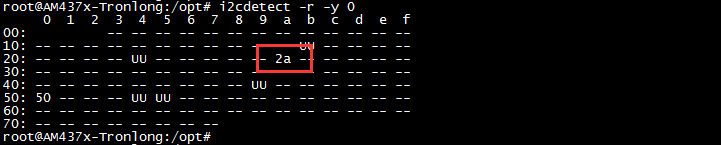

执行如下命令查看挂载到I2C0总线的I2C设备地址,此处查询到的地址为0x2A。

Target#i2cdetect -r -y 0

​

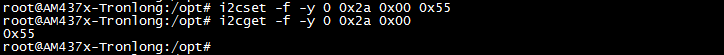

执行如下命令对I2C设备0x00地址写0x55:

Target#i2cset -f -y 0 0x2a 0x00 0x55

执行如下命令读取I2C设备0x00地址的值:

Target#i2cget -f -y 0 0x2a 0x00

​

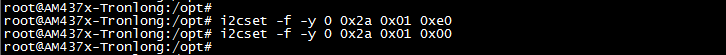

执行如下命令对I2C设备0x01地址写0xe0,开发板底板FPGA端LED5、LED6、LED7会被点亮。

Target#i2cset -f -y 0 0x2a 0x01 0xe0

执行如下命令对I2C设备0x01地址写0x00,开发板底板FPGA端LED5、LED6、LED7会被熄灭。

Target#i2cset -f -y 0 0x2a 0x01 0x00

​

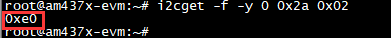

FPGA端按键状态会保存在I2C设备0x02地址中。执行如下命令读取I2C设备0x02地址的值:

Target#i2cget -f -y 0 0x2a 0x02

​

分别长按开发板FPGA端按键KEY6、KEY7,并读取I2C设备0x02地址的值,分别为0xC0、0xA0。

​

2、FPGA与ARM基于GPMC通信测试表 2

开发板型号

| 是否支持本实验

| TL437x-EVM

| 不支持

| TL437x-EasyEVM

| 不支持

| TL437x-IDK

| 不支持

| TL437xF-EVM

| 支持

|

本测试程序将FPGA模拟成GPMC内存设备,对 Linux系统而言,等效于外接内存。使用GMPC总线进行读写操作时,只需通过 mmap函数将物理地址映射为用户空间地址,就可以像对内存一样进行读写操作。

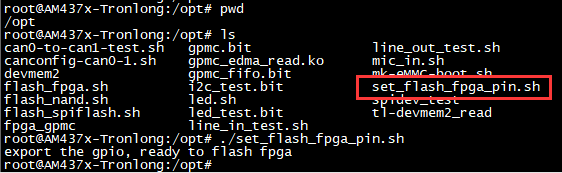

进入开发板文件系统的”/opt”目录,执行如下命令初始化FPGA程序加载功能的管脚。

Target#./set_flash_fpga_pin.sh

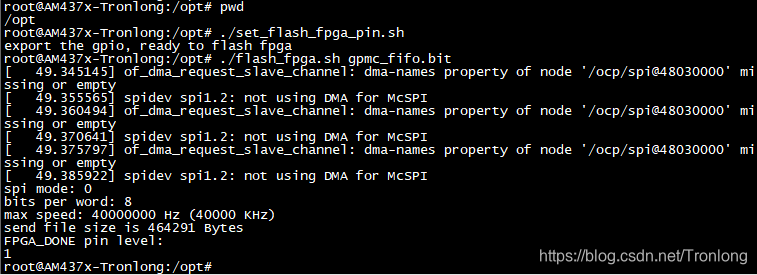

执行如下命令启动FPGA程序加载功能,由ARM通过SPI总线加载.bit文件到FPGA中运行。打印信息中,如果FPGA_DONE的值为1,则表示.bit文件加载成功。

Target#./flash_fpga.sh gpmc.bit

​

此.bit文件主要实现FPGA和ARM的GPMC通信功能,.bit文件、.mcs文件和源码位于FPGA光盘”Demo\app\GPMC\”目录下。

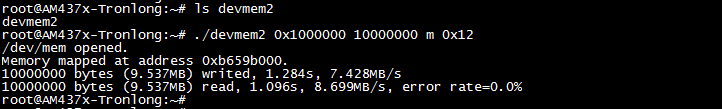

将ARM光盘"Demo\app\devmem2\bin"目录的内存读写工具可执行镜像文件devmem2拷贝到开发板文件系统任意路径。devmem2使用mmap将物理地址映射为进程的虚拟地址,然后对这个虚拟地址进行读写操作。

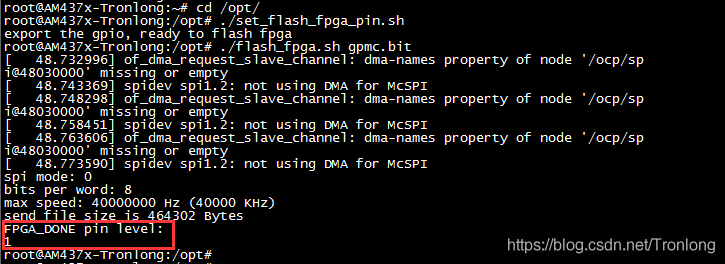

在devmem2文件所在路径,执行如下命令进行读写。

Target#./devmem2 0x1000000 10000000 m 0x12

​

以上命令的作用是:向物理地址0x01000000中,写入长度为10000000字节数据0x12,然后将其读取出来,从而获得读写速度以及错误率。读写时,使用"memset/memcpy"函数。

FPGA连接到ARM的GPMC总线CS1的起始地址为0x1000000,GPMC数据线位宽为16bit,数据线地址线复用,已设置最大访问范围是16MB。

"error rate=0.0%"表示读取回来的数据与写入的数据一致,即GPMC通信正常。

- devmem2工具测试内存读写速率以及错误率,命令格式为:devmem2 phy_addr length type data,含义是向地址phy_addr中写入length字节的data,然后将其读取出来,从而获得读写的速度以及错误率。

- 每次读写的宽度根据type来确定,phy_addr表示物理地址,length表示读写的长度(以字节为单位),type可选b、h、w、m 或 d。

b:每次读写8位。

h:每次读写16位。

w:每次读写32位。

m:每次读写8位。调用memset进行写,调用memcpy进行读。

d:每次读写32位。

当type参数为b、h、w、m时,输出读写数据的大小、读写速度以及错误率。当type 参数为d时,输出写到指定内存和从中读取出来的值。

data表示将要写进内存的内容,为32位无符号整型数。但是在写时会根据每次读写的宽度进行截取。当type参数为b或者m时,将data截取前8位。当type参数为h时,将data截取前16位。当type参数为w时,不截取。

对同一个物理地址,根据不同的参数,读取的结果会有差异。经过测试,使用m选项进行读写时,可以获得较高的读写速率。另外,读写数据的长度length越大,测得的读写速度越准确。

3、AD8568数据采集显示综合例程表 3

开发板型号

| 是否支持本实验

| TL437x-EVM

| 不支持

| TL437x-EasyEVM

| 不支持

| TL437x-IDK

| 不支持

| TL437xF-EVM

| 支持

|

本例程使用TL8568P/TL8568-B的AD采集模块进行测试。此模块基于TI公司的ADS8568芯片,8通道、双极性、16位、510KSPS,用于并行采集多路AD数据。

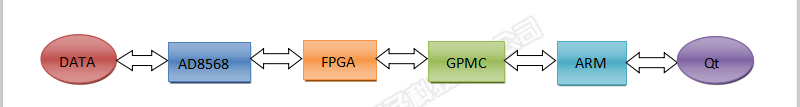

例程实现的功能是:FPGA控制AD8568进行数据采集,再将采集到的数据通过GPMC总线送到ARM端,ARM端使用运行Qt显示采集到的信号波形。整个过程的流程示意图大致如下:

​

NAND FLASH版本TL437xF-EVM开发板:am437x-gp-evm-fpga-nandflash.dts

eMMC版本TL437xF-EVM开发板:am437x-gp-evm-fpga-emmc.dts

在如下对应位置添加以下代码,注册按键事件来接收FPGA采集完成的中断,如下图所示:

button@2 {

label = "user-gpio5_7";

linux,code = <240>;

gpios = <&gpio5 7 GPIO_ACTIVE_LOW>;

gpio-key,wakeup;

debounce-interval=<0>;

};

​

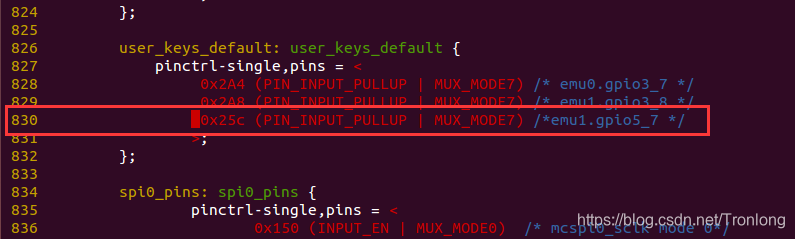

在如下对应位置添加以下代码,设置中断管脚为输入模式,如下图所示:

0x25c (PIN_INPUT_PULLUP | MUX_MODE7) /*emu1.gpio5_7 */

​

修改完成后,重新编译设备树,使用“arch/arm/boot/dts”目录下新生成的.dtb设备树文件启动开发板文件系统。ARM光盘”Demo\qt\AD8568_GPMC\bin”目录下的am437x-gp-evm.dtb为验证通过的设备树文件。

ARM光盘”Demo\qt\AD8568_GPMC\bin”目录下的AD_Test为Qt程序可执行镜像。ARM光盘”Demo\qt\AD8568_GPMC\src\AD_Test”目录为工程源码。如果需要重新编译工程,请修改工程源码目录下的AD_Test.pro文件中的QWT组件的安装路径参数为实际安装路径。

将Qt程序可执行镜像AD_Test拷贝开发板文件系统任意路径下。将ARM光盘”Demo\qt\AD8568_GPMC\bin\lib”目录下的所有相关库文件拷贝到开发板文件系统“/usr/lib”目录下。

将FPGA光盘“Demo\app\AD8568_GPMC\bin”目录下的.bit文件ad8568_gpmc-0.bit/ad8568_gpmc-1.bit拷贝到开发板文件系统”/opt”目录。FPGA光盘“Demo\app\AD8568_GPMC\src”为FPGA工程源码。

开发板连接7寸LCD显示屏,将AD模块插入到开发板的FPGA ExPORT0/ExPORT1接口,并将模块对应通道连接信号源发生器的输入端,然后将模块AGND连接信号源发生器的地。模块量程为±10V。

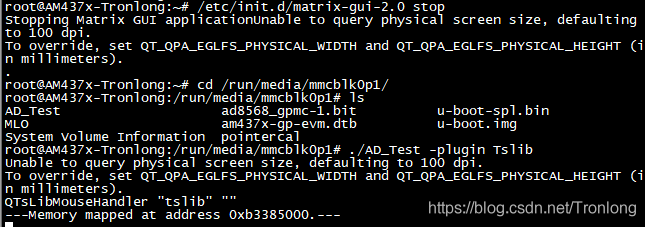

执行如下命令终止Matrix程序:

Target# /etc/init.d/matrix-gui-2.0 stop

进入开发板文件系统的”/opt”目录,执行如下命令初始化FPGA程序加载功能的管脚。

Target#./set_flash_fpga_pin.sh

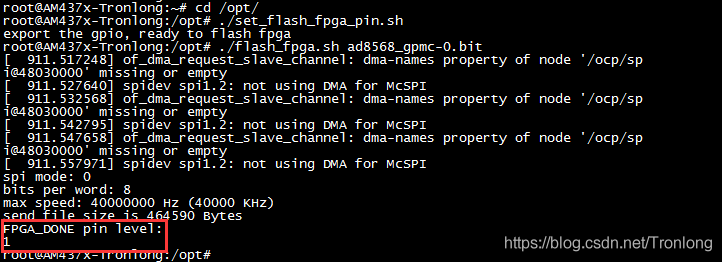

执行如下命令启动FPGA程序加载功能,由ARM通过SPI总线加载.bit文件到FPGA中运行。打印信息中,如果FPGA_DONE的值为1,则表示.bit文件加载成功。

Target#./flash_fpga.sh ad8568_gpmc-0.bit

​

此.bit文件主要实现FPGA端采集AD数据,并通过GPMC总线把数据送往ARM端。

在AD_Test所在路径下,执行如下命令运行Qt程序,显示AD数据波形。

Target# ./AD_Test -plugin Tslib

​

点击屏幕上的pause按钮后,波形暂停在某个状态,再点击start按钮,屏幕又开始显示动态的波形,点击Exit退出显示。

4、基于TL37xF-EVM的GPMC数据读取表 4

开发板型号

| 是否支持本实验

| TL437x-EVM

| 不支持

| TL437x-EasyEVM

| 不支持

| TL437x-IDK

| 不支持

| TL437xF-EVM

| 支持

|

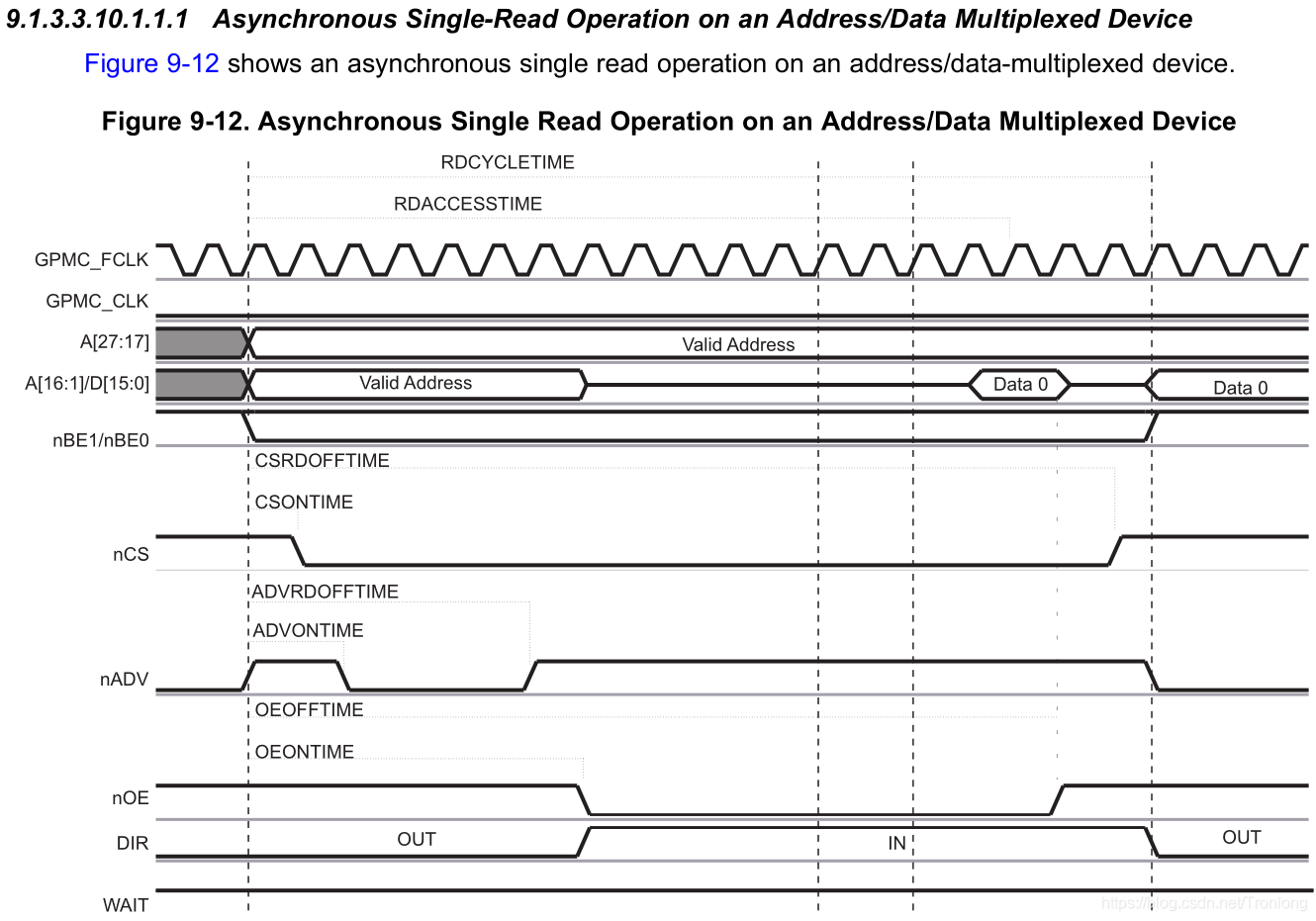

本实验使用TL437xF-EVM开发板,SOM-TL437xF核心板硬件链接上,AM437x已通过GPMC总线连接FPGA芯片,并配置为异步、地址数据线复用的通信模式。实际连接中只用16位数据线,不使用地址线。

本实验实现功能:ARM端通过GPMC读取FPGA端的数据,FPGA端实现每个nOE信号下降沿来的时候,把16bit的数据送到GPMC_DATA端口,并自加一次。

​

4.1设备树源码修改及编译本实验需要按照如下方法配置设备树文件下的GPMC时序。为便于客户测试,我司提供经验证的dtb文件位于“光盘\Demo\app\gpmc_edma_read\bin”目录下。直接将其拷贝到开发板文件系统“/boot”目录即可。

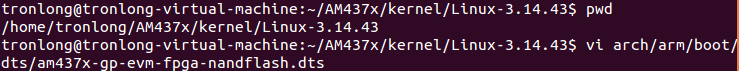

打开Ubuntu,进入Linux内核源码顶层目录执行如下指令,打开TL437xF-EVM开发板对应的设备树源文件:

Host#vi arch/arm/boot/dts/am437x-gp-evm-fpga-nandflash.dts

​

按照下图方法,在打开的设备树源文件“nor@1,0”节点中配置GPMC的时序:

gpmc,mux-add-data = <0>; /* 1: address-address-data multiplexing mode, 2: address-data multiplexing mode. 配置为模式0表示不使用地址*/

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <28>;

gpmc,cs-wr-off-ns = <5>;

gpmc,adv-on-ns = <0>;

gpmc,adv-rd-off-ns = <0>;

gpmc,adv-wr-off-ns = <0>;

gpmc,oe-on-ns = <10>;

gpmc,oe-off-ns = <10>;

gpmc,we-on-ns = <5>;

gpmc,we-off-ns = <5>;

gpmc,rd-cycle-ns = <28>;

gpmc,wr-cycle-ns = <10>;

gpmc,access-ns = <20>;

gpmc,page-burst-access-ns = <0>;

gpmc,wr-data-mux-bus-ns = <0>;

gpmc,wr-access-ns = <0>;

​

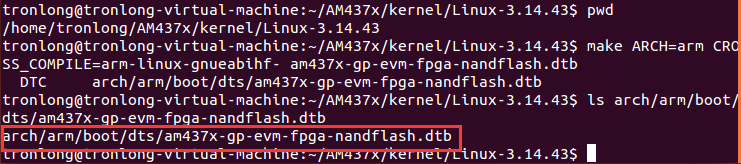

配置完成后保存退出,在内核源码顶层目录下执行如下指令编译生成“arch/arm/boot/dts/am437x-gp-evm-fpga-nandflash.dts”设备树文件。

Host#make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- am437x-gp-evm-fpga-nandflash.dtb

​

将编译生成的“am437x-gp-evm-fpga-nandflash.dtb”文件重命名为am437x-gp-evm.dtb,并替换掉SD系统启动卡rootfs分区“/boot”目录下原来的am437x-gp-evm.dtb文件。

4.2EDMA连续读取数据测试将光盘“Demo\app\gpmc_edma_read\bin”目录下gpmc_edma_read.ko和gpmc_fifo.bit文件拷贝到开发板文件系统“/opt”目录下。

开发板上电启动,进入文件系统的“/opt”目录,执行如下命令初始化FPGA程序加载功能的管脚。

Target# ./set_flash_fpga_pin.sh

​

执行如下命令烧写FPGA端的gpmc_fifo.bit文件,打印信息中,如果FPGA_DONE的值为1,则表示.bit文件加载成功。

Target# ./flash_fpga.sh gpmc_fifo.bit

​

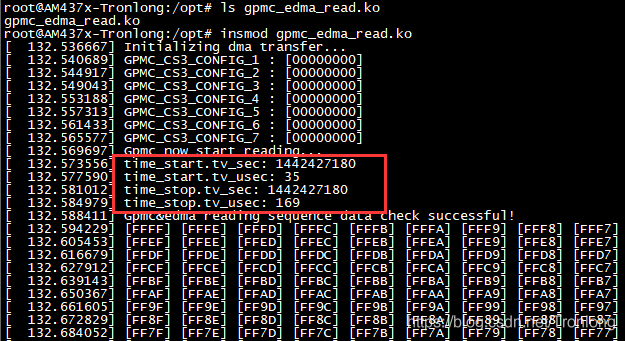

执行如下指令加载gpmc_edma_read.ko驱动模块,由下图可见使用EDMA连续读取到的数据从FFFF递减1到F000:

Target# insmod gpmc_edma_read.ko

​

本次传输数据大小为8 Kbytes,传输时间为169-35=134us,可以算出使用EDMA数据传输数率大小约为60MB/s。

4.3不使用EDMA连续读取数据测试将光盘“Demo\app\gpmc_edma_read\bin”目录下的tl-devmem2_read文件拷贝到开发板文件系统“/opt”目录下。

开发板上电进入文件系统的“/opt”目录,依次执行如下命令初始化FPGA程序加载功能的管脚,并烧写FPGA端的gpmc_fifo.bit文件:

Target# ./set_flash_fpga_pin.sh

Target# ./flash_fpga.sh gpmc_fifo.bit

​

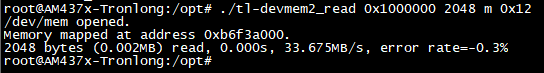

执行如下指令,不使用EDMA,在CPU控制下连续读取FPGA端的数据:

Target# ./tl-devmem2_read 0x1000000 2048 m 0x12

​

由上图可见,在这种模式下,数据传输速率为33.675MB/s,并且CPU的占用率会比较高。

|

|