|

基于AM4376/79 ARM+FPGA的GPMC通信案例讲解 本案例主要基于创龙科技的AM4376/AM4379 ARM Cortex-A9 + XilinxSpartan-6 FPGA处理器设计的异构多核工业级核心板进行讲解:

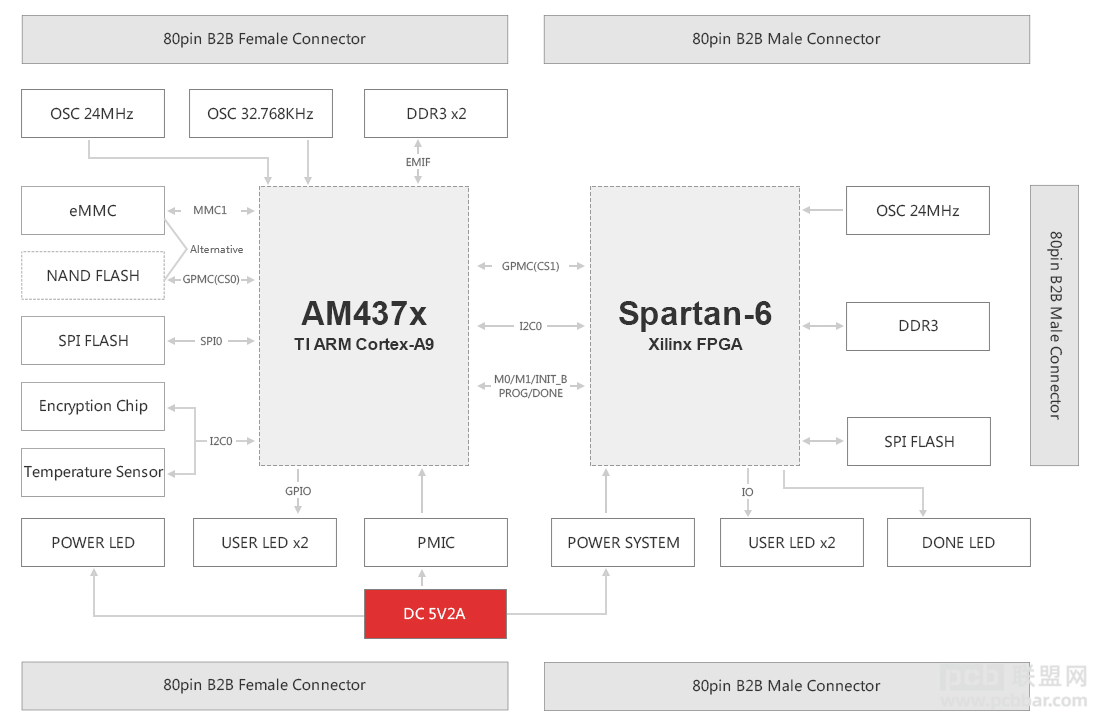

图 1 SOM-TL437xF是一款基于TI Sitara系列AM4376/AM4379 ARM Cortex-A9 + Xilinx Spartan-6 FPGA处理器设计的异构多核工业级核心板。核心板内部AM437x与Spartan-6通过GPMC、I2C通信总线连接。通过工业级B2B连接器引出LCD、CAMERA、GPMC、CAN等接口。核心板经过专业的PCB layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。 1.1 AM437x ARM+FPGA的GPMC通信案例功能案例功能:将FPGA内部的BRAM资源通过并口转换时序在核心板内部与ARM端的GPMC(GeneralPurpose Memory Controller)并口总线连接,实现ARM端对FPGA端BRAM资源的读写。本案例GPMC接口采用16bit地址线与数据线复用的异步读写模式,片选使用CS1。 本案例BRAM的地址位宽为10bit,数据位宽为16bit,内存空间为2KByte(1024x 16bit),使用STARTUP原语提供的CFGMCLK(50MHz)参考时钟,经过PLL的5倍频产生250MHz的BRAM工作时钟。 Spartan-6BRAM的最大工作时钟频率如下图所示。

图 2 1.2 AM437x ARM+FPGA的GPMC通信操作说明将产品资料“4-软件资料\Demo\FPGA\bram_gpmc\bin\bram_gpmc_6slx16.bit”可执行程序加载至FPGA端。进入评估板文件系统后,执行如下命令对FPGA端2KByte BRAM资源进行读写,并显示读写速度。 Target# /opt/product-test/test-programs/mmap-rw/tl_devmem_rw_AM437x-t -a 0x01000000 -s 2048 -o halfword

图 3 1.3 AM437x ARM+FPGA的GPMC通信管脚约束FPGA端管脚约束请查看产品资料“4-软件资料\Demo\FPGA\bram_gpmc\project\bram_gpmc_6slx16\constraints\bram_gpmc.ucf”文件。 1.4 AM437x ARM+FPGA的GPMC通信FPGA端关键代码使用STARTUP原语提供的CFGMCLK(50MHz)作为参考时钟,经过PLL的5倍频产生250MHz的BRAM工作时钟。按照用户手册操作步骤进行程序的加载, RTL原理图如下所示:

图 4 1.5 AM437x ARM+FPGA的GPMC通信技术服务(2) 协助解决按照用户手册操作出现的异常问题; (3) 协助产品故障判定; (4) 协助正确编译与运行所提供的源代码; (5) 协助进行产品二次开发; (6) 提供长期的售后服务。 1.6 开发资料(1) 提供核心板引脚定义、可编辑底板原理图*、可编辑底板PCB*、芯片Datasheet,缩短硬件设计周期; (2) 提供系统烧写镜像*、内核驱动源码*、文件系统源码*,以及丰富的Demo程序; (3) 提供完整的平台开发包、入门教程,节省软件整理时间,上手容易; (4) 提供详细的ARM+FPGA架构通信教程,完美解决异构多核开发瓶颈。 开发案例主要包括: Ø 基于ARM的裸机开发案例 Ø 基于ARM的Linux开发案例 Ø 基于ARM的Linux-RT开发案例 Ø 基于ARM的Qt开发案例 Ø 基于FPGA的开发案例 Ø 基于GPMC的ARM与FPGA通信开发案例 Ø 基于ARM+FPGA的AD采集综合案例 备注:*标资料为购买后提供。 可点击下方链接或扫码二维码获取产品资料。

|