|

|

前言

2 d$ \! C0 R8 @2 h U2 s! ?+ [0 j, Q8 K' P! {

" {% B4 H3 `: X) e5 d

4 M6 y: u- G/ j8 ]& gSDI接口,全称是“数字分量串行接口(Serial Digital Interface)”。按速率可分为标准清新度SD-SDI、高清标准HD-SDI和3G-SDI,其对应速率分别是270Mb/s、1.485Gb/s和2.97Gb/s。目前在航空航天、军事、医疗、交通等领域,SDI的应用广泛度仅次于CameraLink接口。( b a0 Y$ [' a6 a# g" Q/ U3 M$ ^

+ s* T: {& U5 h3 m

​+ L$ o. }; a+ r9 p# [+ x9 \" g' B ​+ L$ o. }; a+ r9 p# [+ x9 \" g' B

w3 M) a) h3 j3 R. _

. E! P) l+ S" N# X i" |

4 O# I% s5 I d. o5 G

$ n( O; ?% F# LSDI接口优势:& ^; I# y- O5 Y* m! B5 V

(1) 消耗GTX更少,消耗IO更少

& T, [+ }2 l; \$ f. m# L如果使用GTX总线,仅需1对GTX,而HDMI则需要3对GTX。CameraLink接口由于走LVDS信号,Base模式下需要11对LVDS信号,Full模式下需要22对LVDS信号,消耗IO数量比GTX SDI多了很多。( @! y2 W4 t% `! C7 j, F3 I0 D# R

(2) 传输更稳定" p* a; Y- |1 M: ~! p

相较于HDMI接口,SDI接口的自锁扣设计更加稳定可靠,不易脱落,不会因人为因素造成信号中断。

' Z: j& u$ ]# N9 K+ m(3) 传输距离更长

- }& U0 d7 k+ H. y% x: r串行接口是指逐位数据的顺序传输。它的特点是通讯线简单。只要一对传输线可以实现双向通信,特别适合于长距离通信。从理论上讲,SDI的传输距离可以达到100m。, c9 L, b/ a6 j) j

(4) 成本更低

9 f! N$ A) R+ E. o; g3 F" b8 CSDI接口平均每米价格约为4元,相较于HDMI接口的平均每米价格约为10元,SDI接口成本更低。* ^5 Z3 h& c0 ^! S5 y5 m

' M {, \9 B" ]; `; F8 r; p. m2 q4 u" x

创龙科技(Tronlong)的Kintex-7、Zynq-7045/7100等FPGA板卡通过FMC视频模块已实现两种SDI视频输入/视频输出方案:GTX +外接芯片。本文将为您分享基于Kintex-7 FPGA评估板、TL2971A/2972F视频模块的3G-SDI视频输入/输出开发案例,使用外接芯片方式。TL2971A/2972F视频模块模块亦可支持GTX方式。 A0 |2 b2 b" }8 q

9 L2 g8 V4 b2 L+ Y& G9 R) e% o$ D5 \- `1 v6 i

' ~; l' x6 V1 e# C2 W) ?* h2 s+ Q! Q

●硬件平台/ t4 l& K4 P* j0 C6 E+ U3 J

: W/ {0 q# Z4 B! j" Y4 S

2 E, v$ W6 X; v5 K B

6 m$ S( z" H' j- ^& F1 TLK7-EVM评估板( G3 ?- R! n: G* c5 S

+ \0 c2 J' L) k% | k8 h+ x本文基于创龙科技TLK7-EVM评估板、TL2971A/2972F视频模块进行演示。

9 e8 ?( A6 R1 ^ t! K) O" l- RTLK7-EVM是一款基于Xilinx Kintex-7系列FPGA设计的高端评估板,由核心板和评估底板组成。核心板经过专业的PCB layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。+ w" j+ ~: S4 r8 k

评估板接口资源丰富,引出FMC、SFP+、PCIe、SATA、HDMI等接口,方便用户快速进行产品方案评估与技术预研。

2 l$ _! A; |9 T- L- E% X可申请TLK7-EVM评估板进行快速评估,点tronlong.com/Product/show/93.html,免费哦!

5 z9 s! z3 A! ~( Z  ​/ D' L* @6 L1 b9 P ​/ D' L* @6 L1 b9 P

3 R1 U' P! K- x' q% \! \' v' g4 i1 d. n2 v' V( \: \

TLK7-EVM评估板& m4 k/ ^! z1 o1 P- f

3 r/ m7 ?! }! e2 [5 ?' b2 ~+ U/ Z. j1 K4 N+ l

( v2 n1 [9 {2 C3 ? F8 a( K( C2 TL2971A/2972F视频模块

( {, C8 D N$ t0 a" r7 Q/ r" }" K6 Y" G; m8 j8 s3 U5 t4 w

TL2971A/2972F是一款基于FMC LPC标准设计的3G-SDI视频输入/输出模块,与创龙科技Zynq-7000/Kintex-7/Artix-7等评估板配套使用。以下为此模块特点:4 d# r' c4 I( v8 o. ~2 B

(1)通过GTX高速串行总线引出1路SDI视频输入接口,最高支持2.97Gb/s(1080P60)。/ ~0 M5 J: L8 ^- m( q

(2)通过GTX高速串行总线引出1路SDI视频输出接口,最高支持2.97Gb/s(1080P60)。9 Y' r& f" S! q

(3)通过GS2971A芯片引出1路SDI视频输入接口,最高支持2.97Gb/s(1080P60)。

( p" }# n( h' N" H0 n5 d(4)通过GS2972芯片引出1路SDI视频输出接口,最高支持2.97Gb/s(1080P60)。4 y% j- z$ x: P, N

(5)采用标准BNC连接器,支持视频设备热插拔。

0 G* \* E# W; o8 `: q8 f  ​ ​

+ j0 o6 `- b& U8 |

! Q c1 N/ y. z$ e+ S: S, |' I7 q2 s8 j! j

TL2971A/2972F视频模块5 Z; u: J: W. v, b. [6 b

( {! D0 D. o2 k; @, {' y

9 n( \$ ]) d, l' y: }- _4 a: M. q6 M0 G+ D; f/ Y, ]% H+ m

: n/ G1 x% s6 o% B

$ b: w) O, g: b9 m" K7 S" i( k9 J; b- m

●案例功能1 f. B0 G6 D4 |+ I6 Y

, t/ ~# X6 F5 ^8 {$ _1 U u' z6 Z5 ?" h: h2 k5 H

; A0 t K8 R$ r, E( A

本案例为通过GS2971A、GS2972芯片引出SDI视频输入、输出案例。通过GTX高速串行总线引出的SDI视频输入、输出案例即将发布,敬请期待。7 j3 c! l6 j6 @9 C6 ?* l' @4 w

案例功能:评估板通过FMC视频模块TL2971A/2972F的SDI IN接口进行1080P60视频采集,并通过TL2971A/2972F模块的SDI OUT接口将采集到的视频进行输出。案例源码、产品资料(用户手册、核心板硬件资料、产品规格书)可点:site.tronlong.com/pfdownload获取。

% w! F- g3 l' Z* h' O- {( ^+ B/ p; `& ^1 o3 O. i5 s

& X. T1 \# @8 D: _3 _

开发案例主要包括:5 h* p8 D3 g$ m8 ]2 X2 n- z7 E8 C

l CameraLink、SDI、HDMI、PAL视频输入/输出案例( j3 U& P; J2 N

l 高速AD(AD9613)采集+高速DA(AD9706)输出案例

( c4 C2 p% i3 W# L6 o# C7 yl AD9361软件无线电案例

$ v( j1 J( L& _* u+ a, Wl UDP(10G)光口通信案例

& b4 _( \' i. u" }l UDP(1G)光口通信案例

9 j( j" Q+ V, y$ El Aurora光口通信案例

S0 ?; e8 L/ ~$ N& ]* |& kl PCIe通信案例

8 L% \( P* n+ g6 Y

) L2 L& V6 D/ ]! \8 X

! P3 l1 x/ D+ ^: Q5 g n

}3 p1 n c- I/ X1 O0 z●案例演示$ g( d9 g1 y$ I7 V

+ ^: j! e$ n( m* c将创龙科技的TL2971A/2972F模块连接至评估板FMC1接口,评估板J1跳线帽选择3.3V档位,以配置FMC IO的BANK电压为3.3V。

, e& n# `& V2 g, ?- e+ d9 T4 E准备一台拥有HDMI OUT接口的PC机(例如笔记本),通过HDMI数据线将PC机HDMI OUT接口连接至HDMI转SDI模块(厂家:玩视,型号:3G HDMI TO SDI Audio)INPUT接口,PC机HDMI OUT接口用作图像输出。通过SDI数据线将TL2971A/2972F模块的SDI IN接口连接至HDMI转SDI模块的OUTPUT接口。

: `- F7 `3 m9 b; n( g- H1 y; m: Z9 q" ]. |5 n* X

`3 H( i9 S3 A

通过SDI数据线将TL2971A/2972F模块的SDI OUT接口连接至SDI转HDMI模块(厂家:玩视,型号:3G SDI TO HDMI Audio)的INPUT接口,再通过HDMI数据线将一台HDMI显示屏连接至SDI转HDMI模块的OUTPUT接口,HDMI显示屏用作图像显示。3 e& j' e; N7 W7 y% C$ s5 r/ h

5 u; y( v+ V9 W' E. `% [/ }( g! v/ N- K9 Q. u8 U' X: f- Z _7 [/ R

2 X$ v$ o `) L; b8 h; r0 y. C! v% M# ~/ m- W* Q3 W

​ ​

! Z( A" `6 q& |0 M" s( S0 Q

1 L0 m! h9 |* M4 B& `, ~/ q' g$ n4 z% \6 T( O& o8 G7 }& m* S

​ ​

# g4 Y" T. N; d) x; x4 i

, u. {; V( t. Q$ H& e1 T1 x- t) `& d: H9 Q; H! b& v

! w1 L# {" O- Q& B% I+ y: L

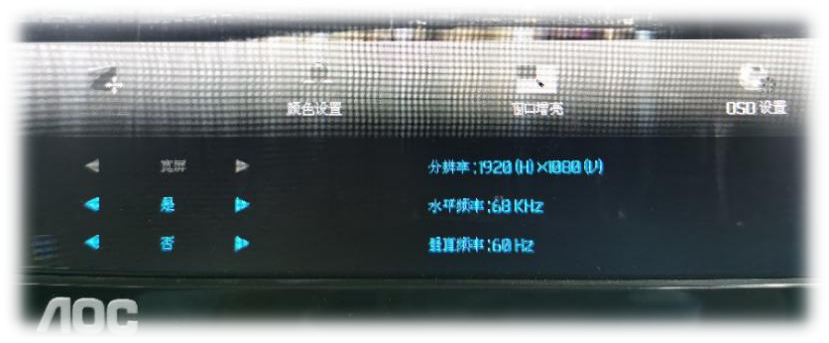

0 u: x0 S6 {: i$ V$ `运行程序,即可看到串口调试终端打印如下信息,然后在PC机的显卡设置(或图形属性)中,按照下图设置HDMI分辨率为1920x1080、刷新率为60pHz。

; q' E% V0 P& B/ |. o+ c% G/ r* T3 n' h/ Y$ ~ O

v7 n1 ^& F" y, H0 t# s' T

​ ​

* |1 k; f5 Y1 }+ Q' v3 y

7 p1 J- R% U7 j; M- k5 p7 G8 Q6 m( j; m2 y( ?% A

8 q, s% ?9 |/ W/ ?' j5 m

! x6 p C+ K0 t: r4 N3 p5 K

​( l+ l+ r, ?# L0 l ​( l+ l+ r, ?# L0 l

# W( W* G" d k/ O- V% ^6 U) O4 a N+ N. }! F n/ W: B3 h/ w) m

此时,HDMI显示屏将显示PC机HDMI OUT接口输出的图像。

$ p( d5 [/ Y3 m4 [0 I+ f  ​ ​

( \4 d! E$ w. m" z: c/ P, k

3 Z2 y, l8 M! b. {+ U$ M6 U7 z* O6 |+ T

​ ​

( ~% ]; ~6 m$ y+ K4 j' H' |4 ^

$ r3 V/ c3 _* i! P; A2 M$ n. h' a/ `/ k" ^

●关键代码(MicroBlaze)

# y7 K0 V+ V% E' Y, u9 w) F. A: y% z5 @( W! |0 O6 L& l

MicroBlaze裸机源码为"sw\baremetal_demo\project\sdi_capture_display\src\",关键代码说明如下。

0 ?0 H: y$ S. w( `

) e% b8 F% t3 w6 k( S! b# [, z/ L% a/ @" j c: r) J

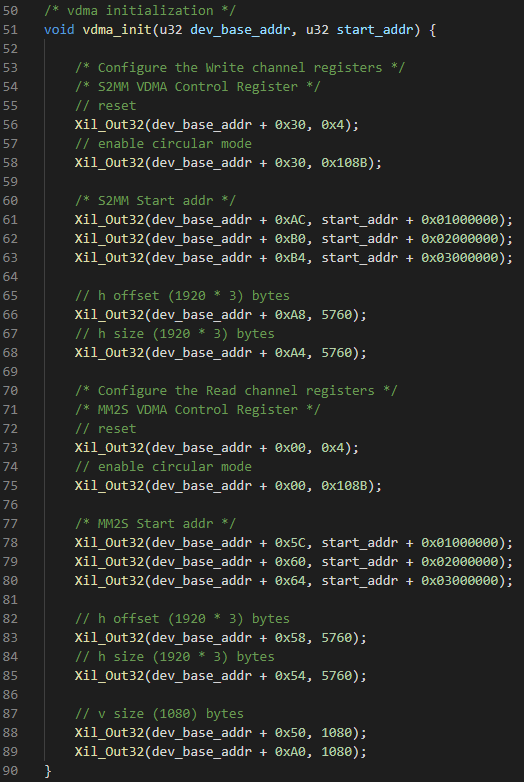

(1) 初始化VDMA,将采集到的视频数据缓存至DDR,并将视频数据搬运至AXI4-Stream to Video Out IP核,再进行SDI视频输出。; A& b; w! V0 S

​ ​

# O/ h! [) h @7 ~● IP核配置* w' X1 Y$ b2 v8 W

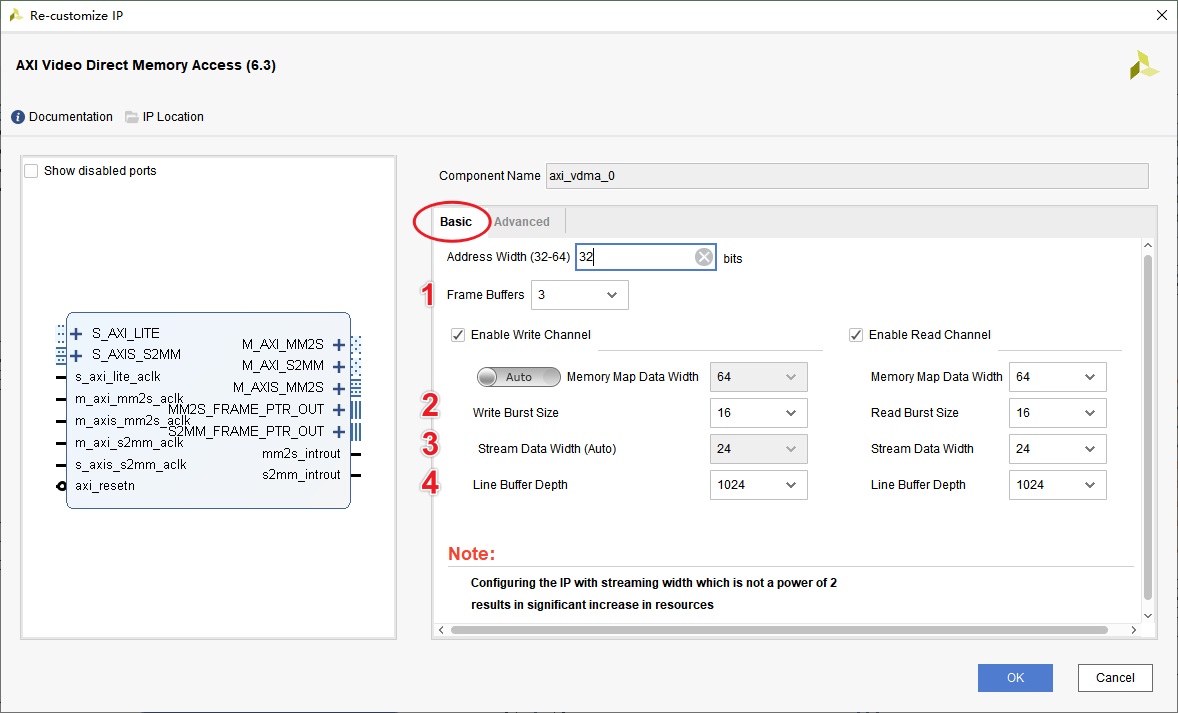

4 p: `" g J, g/ R& V6 I3 L, O1 VDMA IP核, h9 m! G' L. K2 y" ]# k- s

1 o: k" L8 J+ @: H4 T# M2 Y5 N$ k本案例使用VDMA IP核进行视频数据缓存。

& ^7 m& y, c" y* V+ pVDMA(AXI Video Direct Memory Access) IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的pg020_axi_vdma.pdf,具体配置说明如下。

5 V6 V x, X8 h(1) Frame Buffer配置为3个。

^& Q/ n& e8 l# |0 S# P; }' m(2) Write Burst Size、Read Burst Size均配置为16。 h0 s! ^2 X5 [# Z$ }

(3) 读通道的Stream Date Width配置为24。$ z$ M' O' b' u- n# E& Z7 M

(4) 读/写通道的Line Buffer Depth均配置为1024。

: @( B6 r! t9 k- M  ​) Q5 P7 l; J" x# o" a! r* h ​) Q5 P7 l; J" x# o" a! r* h

$ A6 l0 |& ^& b7 [* ?# R1 U

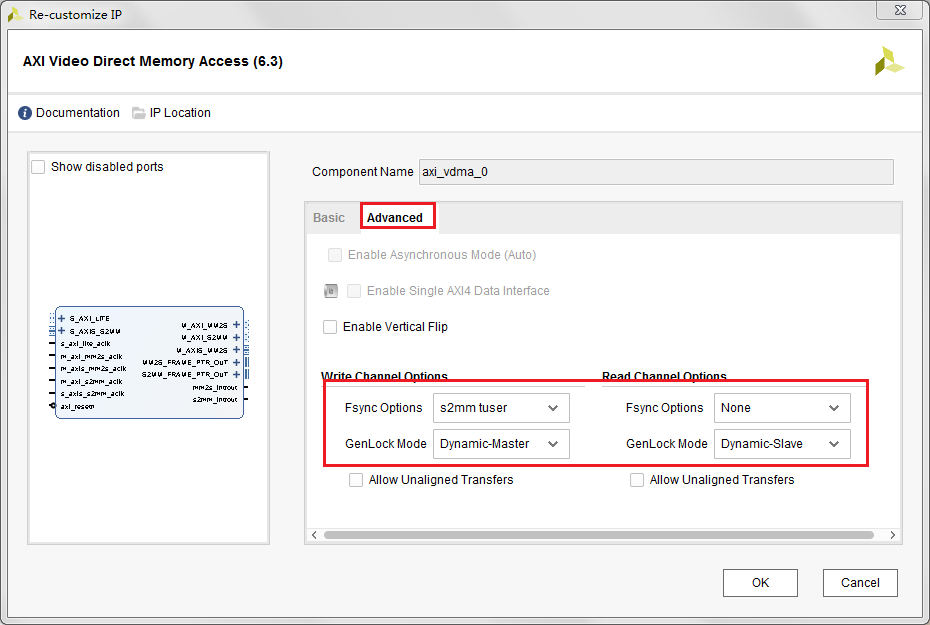

% {+ \. h a) g(5) 点击Advanced,保持默认配置,即可避免VDMA同时读写同一个Buffer,造成视频数据传输乱码。

$ h: u' J% q7 @- W) g

) _4 g9 m1 Q: M4 S, n* @2 M) Y/ |. m0 w' c; O

​, S" U$ C2 j; t( f+ \# V, `8 p$ G ​, S" U$ C2 j; t( f+ \# V, `8 p$ G

/ e: k! d& ^- e: I7 x8 S4 X6 d

5 U* t% v; I! A6 y5 T/ [

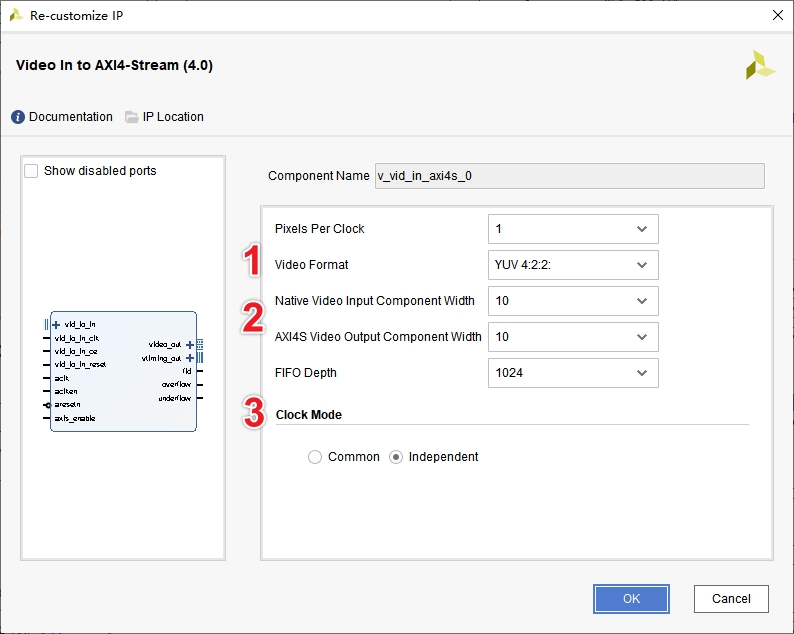

2 Video In to AXI4-Stream IP核

2 R; K/ a0 t6 m% o8 A: F" S

6 M6 F- @' T7 T/ w, f) H本案例使用Video In to AXI4-Stream IP核将并行视频信号转换为AXI4-Stream视频流。0 |/ M) x2 O2 _/ F$ d

( _, X0 @% W7 G6 V' k

9 }9 x6 I. g _. R' g

Video In to AXI4-Stream IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg043_v_vid_in_axi4s.pdf》,具体配置说明如下。

4 d: X' K* `- z. g% k4 ^+ L& e7 U

u+ n% }) k6 L8 Z: N6 P% n- M" Q

1 _! c5 c* w' _% O(1) 视频格式配置为YUV 4:2:2。0 O& w: |: m, r r g) l8 m

(2) 数据位宽配置为10bit。

: m$ ], p- l; u0 E. N! P/ |(3) Clock Mode配置为Independent(独立时钟)。

$ `' | ~- {& u+ {1 W, x6 ]  ​ ​

0 S, v6 z& y2 ^; i0 Q$ c5 _/ r- f) i" |# M7 {) b, V- x$ O) P6 {0 n$ o

9 l4 a% M. }2 k! t0 a! P

+ w/ a" _. X% k3 n" l7 k9 V* T% i8 r8 {# S9 V) j- ^

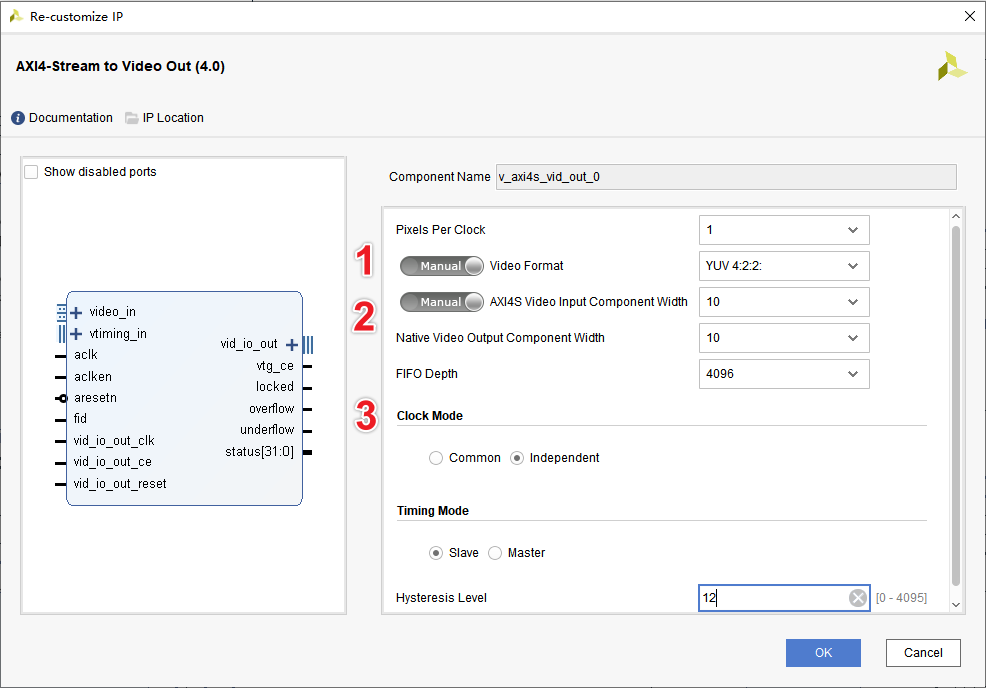

3 AXI4-Stream to Video Out IP核) ?( M) w: P8 {- |0 Z1 X) I, {

% o. P! S; q6 y

本案例使用AXI4-Stream to Video Out IP核将AXI4-Stream视频流转化为并行视频信号。+ A% Q2 {) c# C* W/ G" r; i( D

AXI4-Stream to Video Out IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg044_v_axis_vid_out.pdf》,具体配置说明如下。

+ H. g: f: V$ `% Z1 M" n(1) 视频格式配置为YUV 4:2:2。& O h) ~6 s1 W: o$ Y, C" D

(2) 数据位宽配置为10bit。7 T+ X3 h# K5 M( ]: e2 C! U) @

(3) Clock Mode配置为Independent(独立时钟)。

, ?" }8 E+ _& o( ]: c  ​$ O0 D7 G* E( Y ​$ O0 D7 G* E( Y

" `! X) W1 Z/ v$ C- P/ X

" ]* C i% w1 c5 z% t* Z8 M$ [

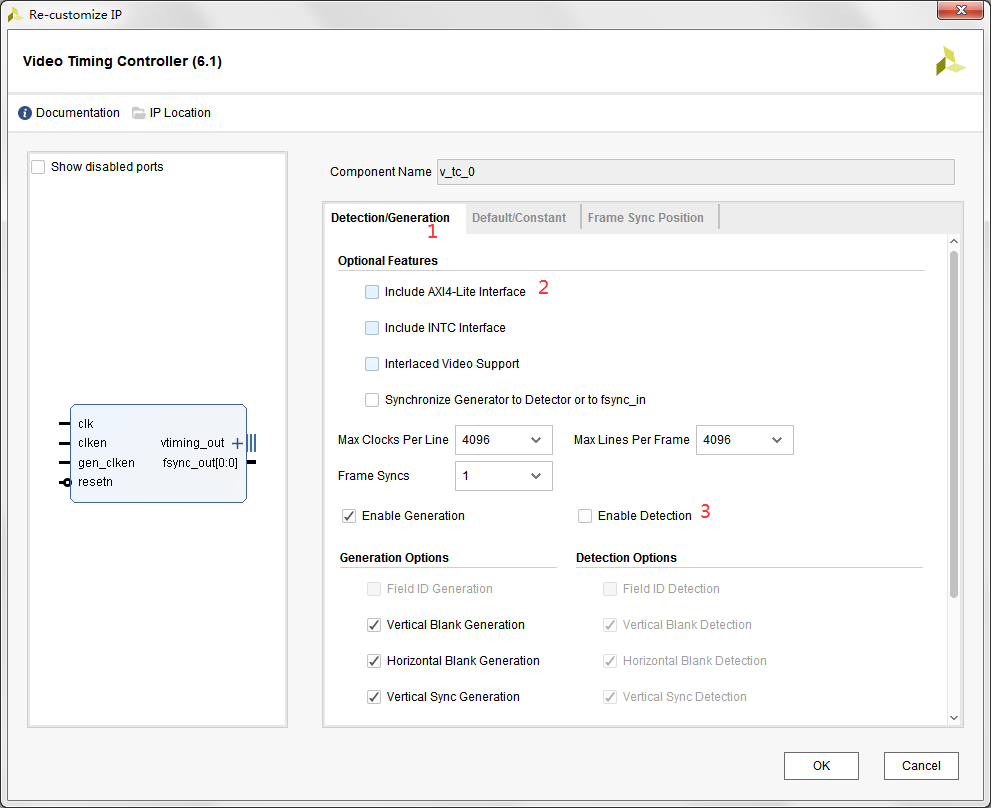

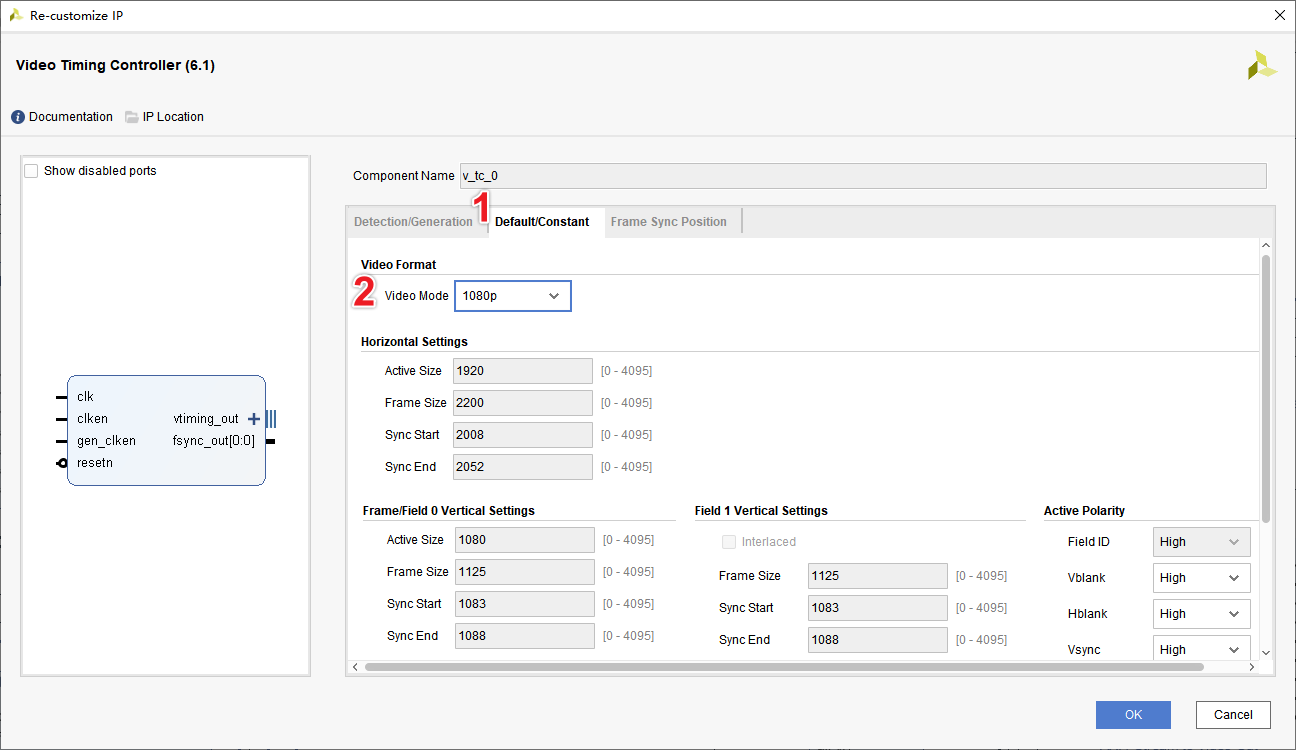

4 VTC IP核

& y o9 [) \8 Q- u. f4 v: k6 i- g0 Y* a( n5 E2 v2 C

本案例使用VTC IP核产生用于视频输出的时序。

* o. i% F! D; i" Q2 f8 aVTC(Video Timing Controller) IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg016_v_tc.pdf》,具体配置说明如下。% {( Y* e( Q# Y A0 u) g

(1) 点击Detection/Generation,确保不勾选"Include AXI4-Lite Interface"及"Enable Detection"。3 U4 o( j! L, l+ a2 c8 _7 o. R3 w

* W, z, Y) b+ ]$ L6 d. p3 Z9 ]8 R' p$ `/ h( Z$ ^

​ ​

/ F+ ^; b) n2 X6 {

' S& Z" C" m5 p: a1 ?" C, z8 i. Z. P- \! J6 L" ^

(2) 点击Default/Constant,Video Mode设为1080p,其余配置保持默认。

2 ]: i9 \- W @% t& t  ​4 ~1 X+ Z/ p3 \) D. D2 c ​4 ~1 X+ Z/ p3 \) D. D2 c

" u7 j; ^9 p7 h; g8 C6 ~ y) ?# q9 r4 E& ^& b& H0 s; D l$ f

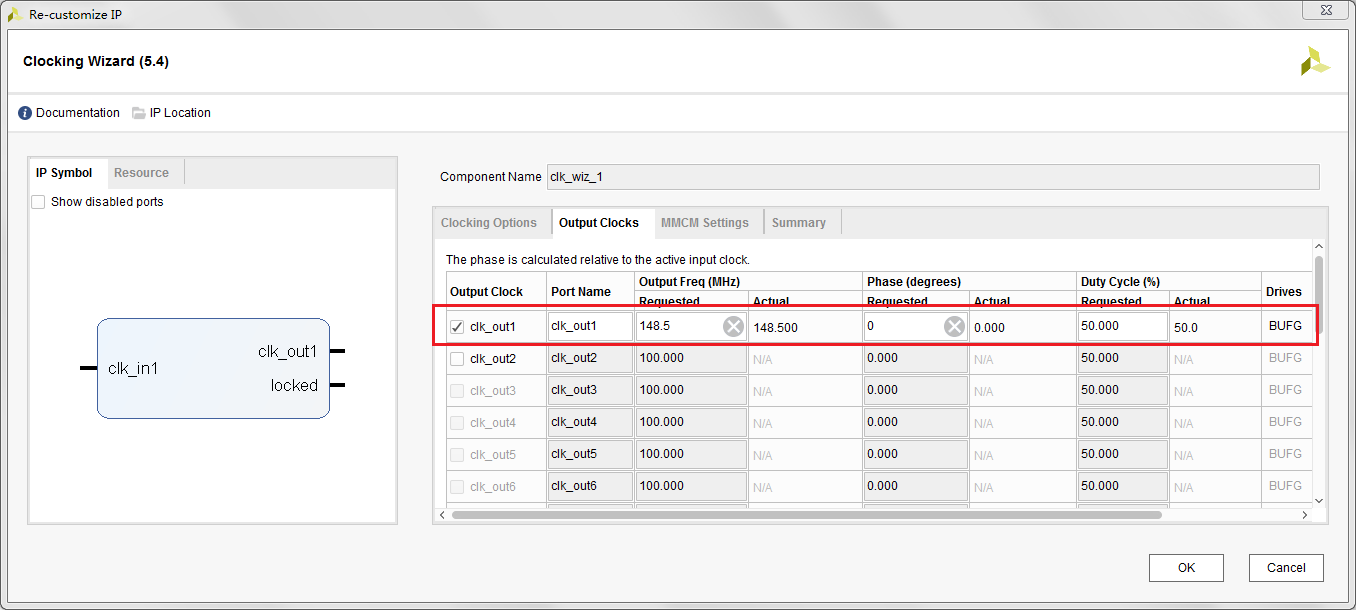

5 Clocking Wizard IP核. W) o. D) t% t

! L1 j+ P4 Z" d& b本案例使用Clocking Wizard IP核产生用于视频输出的像素时钟(148.5MHz,对应1080P60)。) ^3 F6 @, x6 P: U! N* b& G

Clocking Wizard IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg065-clk-wiz.pdf》,具体配置如下。

0 h4 }7 y& j, N  ​" u( f5 _" t$ ? ​" u( f5 _" t$ ?

2 i$ w* I b" D: T! C x1 W

! {5 B" B0 A+ s+ U# X" Y' s9 ]9 _2 T ?% h0 a) N7 {

( l4 O3 X# e. L$ z) W9 z

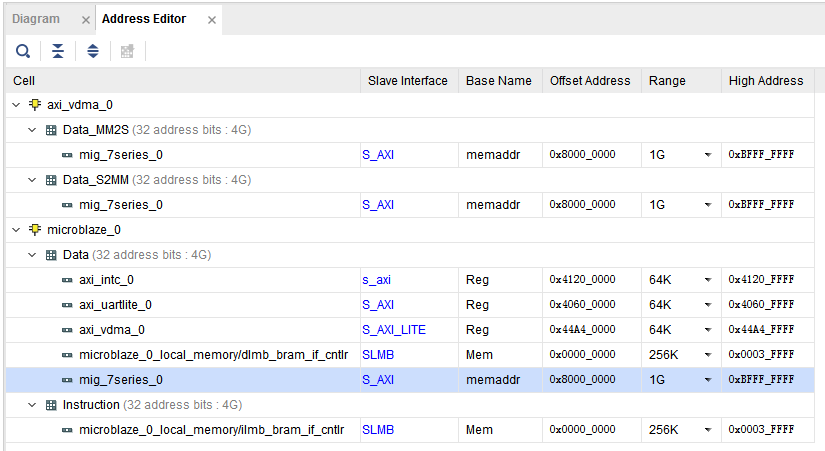

●Vivado工程说明6 F! L9 c6 G# E6 {

2 I9 l. }. E3 [; y7 v/ Z4 T点击BLOCK DESIGN开发界面下的"Address Editor"选项,可查看IP核分配的地址,MicroBlaze可通过对应地址对IP核进行控制。

8 a3 G# t. k, w( M; J5 f# v  ​" o# t+ ^" C% b$ b w8 B- O3 [& P& K ​" o# t+ ^" C% b$ b w8 B- O3 [& P& K

4 D$ B/ U8 g7 K

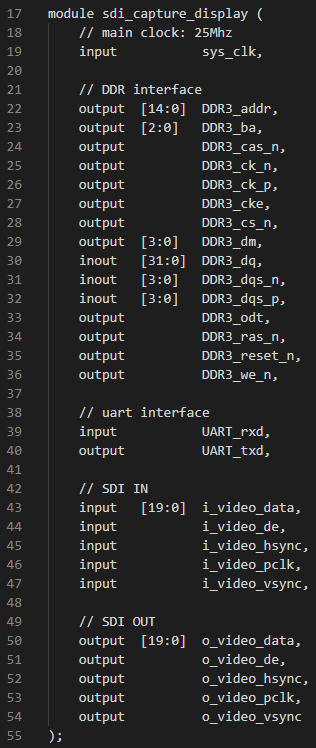

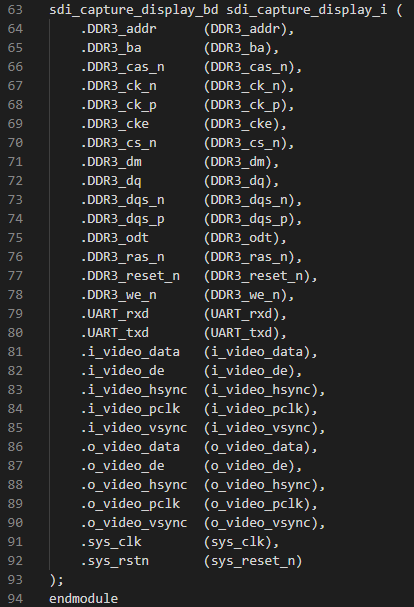

+ l$ C$ E& N4 W5 C3 YVivado工程顶层文件为"hw\project\sdi_capture_display.srcs\sources_1\imports\hdl\sdi_capture_display.v",关键代码说明如下。

2 R! [3 i [2 b0 o0 Q$ h+ O* y& ?5 [2 E

' D, t5 z$ u4 D! ]" D$ p

(1) 定义模块接口。

( D0 D$ C T( k% D) g5 x  ​ ​

) I, P3 n2 T) Q) h3 ~: F; s# @. j. J! M$ O- H! [+ x7 f

: J& {+ x$ @% {+ r' _" ]+ `. b

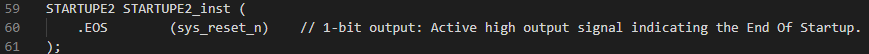

(2) 使用STARTUPE2原语输出复位信号。- f% H3 s; l% h! K8 X9 _7 J

​ ​

. K2 v- F/ N( N% S3 C, D \7 J3 D# X2 c0 I N! b/ A7 b

3 R. F- f/ m2 Q9 p0 Y. _5 q% u

* q4 |* j& V/ ~' Y$ q: h% _

3 P# u5 q7 B& y(3) 调用Block Design。- c8 D$ m# Z a

​9 L1 W0 e8 W2 ^& Y ​9 L1 W0 e8 W2 ^& Y

" W: z! d3 v7 i3 l

& f, |9 f/ T) Z) i4 g  ​% Y8 e F2 |$ C% ?! _1 D! o; ^! h ​% Y8 e F2 |$ C% ?! _1 D! o; ^! h

( o% b# K8 A7 d; e

7 a6 Q& _1 h9 A

|

|