|

|

相比mentor和cadence,AD高速领域似乎还有待加强。但是不可否认的是,在中国AD的使用者占了绝大多数。最初我使用的是orcad9.2,做过51和ARM7的板子,之后发现用protel的人占大多数,就改用protel。# V% g, @( B2 ~" a# f7 M# |

最后很自然的就习惯了AD,并使用至今。但接触到高速电路后,发现PCB文件全是用pads画的。这让我对AD有点失望,打算随波逐流似的也用pads。随着时间的推移,更多的时候都是在调试,尤其是有超高速AD的硬件电路。0 d4 K: G' N. C, J; y8 G* ?# v

没有那么多12层、10层的电路让你画,不是时间太紧就是有现成的硬件,学习新软件的打算就次搁置了。现在再回过头仔细想想,其实大家都明白选择pcb设计软件和选择软件语言是一个道理。

$ s" c9 D' M, x; _9 e5 F 一通百通的道理对PCB设计软件一样行的通。现在我觉得产生这样矛盾心理的人都是自己跟自己过不去,非得选名气大的,功能全的,说出去够厉害的。就事论事,撑着在学校的这一年时间里再花点时间和精力把AD研究透些,留下文字的足迹再说。

6 C# o0 V" S! x* u1 d/ Q如果有和我之前一样矛盾的朋友,我想下面几点能让坚定的一路走下去:' k" _. K4 C. {; C6 e) l

1.PCB设计软件毕竟只是一个工具,能玩转AD或者任何一款都足以应付大部分电路设计了。4 W* Q/ O* N% N7 X7 ^

2.调试的时候,pads或者中意软件设计的文件看多了,感觉上手也不需要花多久时间。* E) Y# N! F# E: z2 q

3.硬件设计重在经验,工具再好,经验不足等于零。

" s4 x2 \9 D! x v& ]% D) }2 v 4.PCB制图并非立足之本,高层次的系统理论结合工程实践经验才是王道,所以留住有限的精力去学习别的把,拓宽自己的知识面。

* w; u4 T& z7 k! P( Y8 | 为了给自己一个深刻的印象,我将花一部分精力总结一下AD里面常用的功能。(注:我只是为我自己而写,有些容易操作但是讲解繁琐的就一笔带过)# q8 q* q/ w$ f* K8 }

9 Z$ Z Y. F" N4 x原理图部分

. K O9 P) X- h! X3 F" _0 J1>自顶向下的设计风格- d: u4 }) |3 J

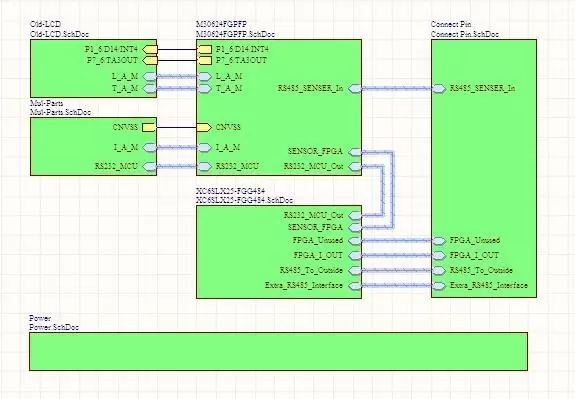

, l7 n+ x% ?: C# X/ w(顶层)模块连接图

2 d5 W- a b% i+ M1 V) A4 H9 b, I3 [4 M9 Y5 g: \$ Q; X! B4 `

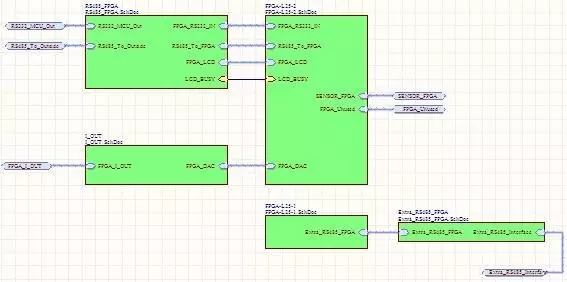

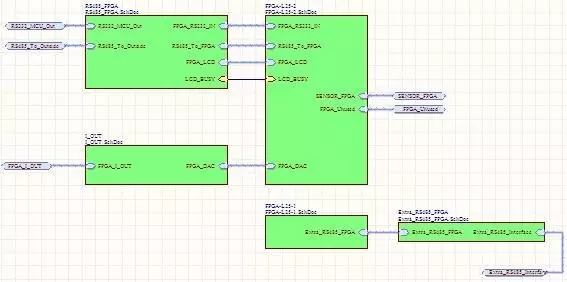

. n. x7 C; J) h" x(顶层)->(XC6SLX25-FGG484)模块连接图: q: q }' s! D9 c

h( u; V* W* h 2 N* A, @ L( \$ i" v8 l( y 2 N* A, @ L( \$ i" v8 l( y

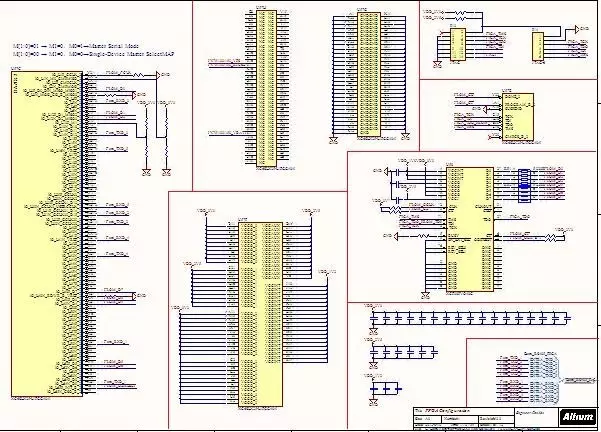

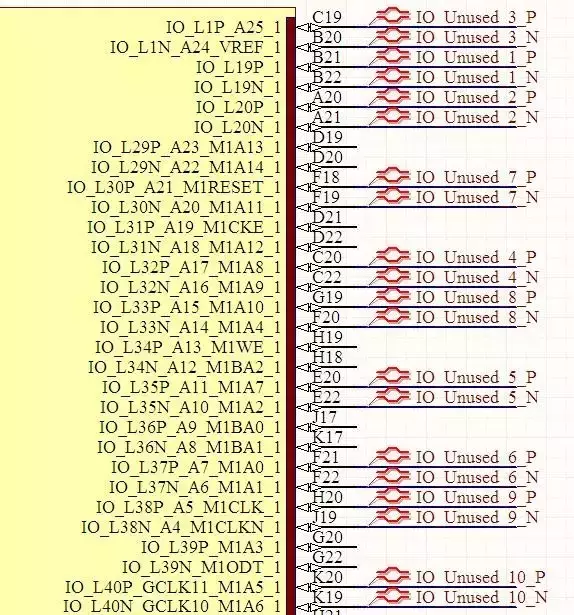

(顶层)->(XC6SLX25-FGG484)->(FPGA-L25-1)模块电路图1 `; j( @8 ~7 k" u& G

0 |$ C& G- U% C: k, b( }/ d1 m工程设置Project > Project Options > Options > Net Identifier Scope > Hierarchical。这就保证了本地原理图内的网络标号与其他原理图没有电气连接关系,各原理图之间通过Harness用Signal Harness导线连接。这就便于电路的修改和调整。

; e9 D! b; x! _0 I8 R/ k3 ~! G: h) v# P

2>差分类的定义

4 v, | k& a4 U9 `7 A" z2 p : `% E# T7 C; I" q) }. d( m" w, y, e : `% E# T7 C; I" q) }. d( m" w, y, e

在成对的差分线上放置差分对标识符(位置:Place > Directives > Differential Pair)。同时它们的网络标号必须用P和N结尾。 在PCB窗口中就可以查看到设定的差分类了,如下图。9 \1 d: ~$ b5 F- c0 r4 h

原理图其他的常用功能还包括:Sch List和Sch Inspector的批处理功能、右键Find Similar Objects的分类查找功能、Cross Probe(注:按住ctrl键便可不返回,原理图与PCB元件选中同步需要事先将Tools>Cross Select Mode勾上才行)、Annotate Schematics(注:对于分块的元件,在刷新标号时一定要事先锁定标号,避免块标号错乱)、Make Schematics/PCB library将元件与封装一一对应(注:封装库画完后,生成当前项目的原理图和PCB封装库,并剔除其他库,方便查找和修改封装)等。

# o: I+ Z4 B$ R4 @) |0 [9 _3 }! z5 F4 u3 m D2 h( [

PCB部分

3 g' C1 \3 W1 e6 o 除开官方资料,我认为比较有用的资料有,class应用、蛇形走线以及差分蛇形线等(注:差分蛇形只能使用调整的方式):" J" j5 j4 Z! e0 I$ m

或者(见原文地址)

2 T3 z2 t4 I7 W9 {( t: C差分信号的设置与布线.pdf/ G! y6 P9 U) w. N6 m

Altium_Designer高级技巧总结20111018.pdf4 h4 _2 @4 |) J0 S: J

Altium_Designer提高教程.pdf, a4 H4 m% F- o/ t ]

这部分最好是自己去体会,每个人的理解不见得一样。

3 _0 ]7 V5 {2 i: ~: I9 Y

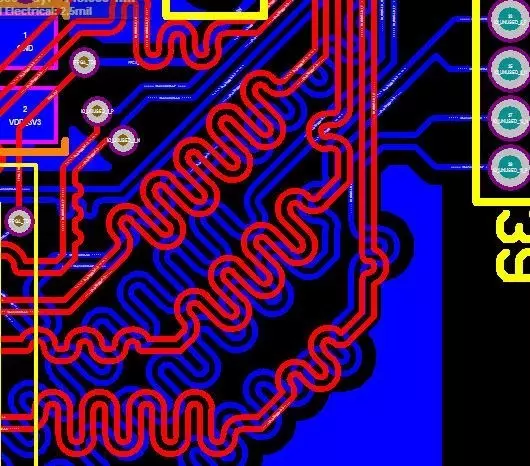

( ~! [$ R- V- t- B5 I+ u蛇形线实物图:

" m x( l9 Z9 t6 w3 x( Z

- R% G" \0 t# I ~ \% w蛇型

% F; |3 z; l* Q8 q) X9 L% H8 i U6 X; j3 N) K2 k, }% _

, b @/ a8 o% t9 ?, d6 |! {/ l5 f , b @/ a8 o% t9 ?, d6 |! {/ l5 f

) o' W) \- _! c" D$ ]3 H差分蛇型(注:最好不要换层)& j; q1 Z. p( `" \

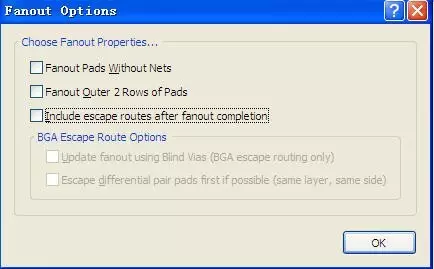

9 m9 S# V m$ a9 fBGA自动散出功能:在BGA器件上点右键 > Component Actions > Fanout Component 弹出下图。

* @' [4 n ?) S9 l5 ]7 I

% K" s8 c5 _: ] 1 (有网络的焊盘)/ (所有焊盘)

# G7 s4 G0 v3 I3 @" j2 W$ M( j; \5 N2 ^1 H

2 (除开最外两圈的焊盘)/ (包括最外两圈的焊盘)6 ^9 g. ^8 [2 o1 _8 l: R( U

" x: `/ J$ u& w& q1 N7 U

3 (反之,不连线) / (所有焊盘散出完成并连线至BGA边沿) * a% d+ @! e- a ^; d

# F4 L) P; w2 r 3.1 (反之,不使用)/ (使用埋空走线,注:只针对BGA)

8 l* L1 ` h1 B3 {1 y- u; t

2 `7 @( i' [' U) q3 u2 r& J 3.2 (反之,不优先)/ (优先走差分对,注:同层、同边的差分对)

. u5 R/ X) [; L& ]& q) N! i- @9 e( a0 l+ j! m" s5 n; q& O& c. |4 c

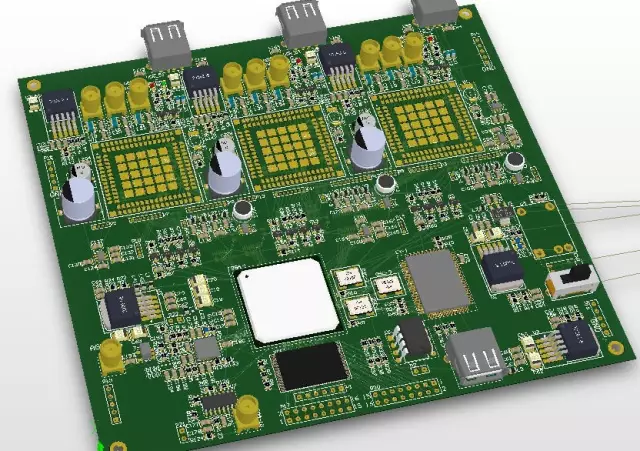

最后主要说说让我对AD念念不舍的一项功能——3D模型功能。7 T! ~' g/ w( \% j+ Z. p9 B$ H" q

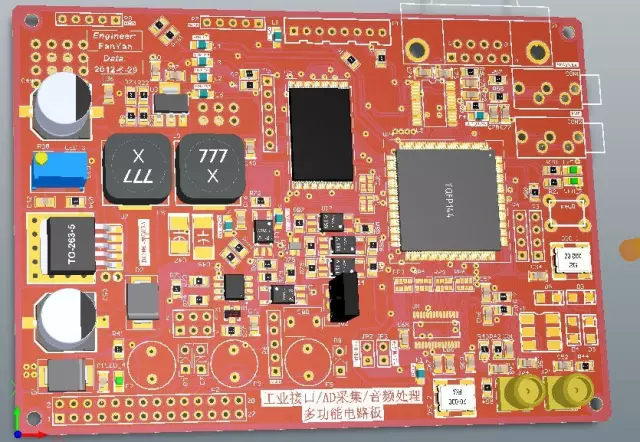

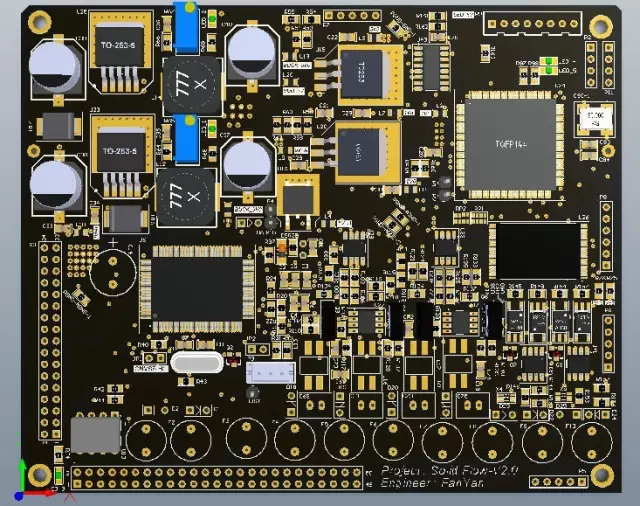

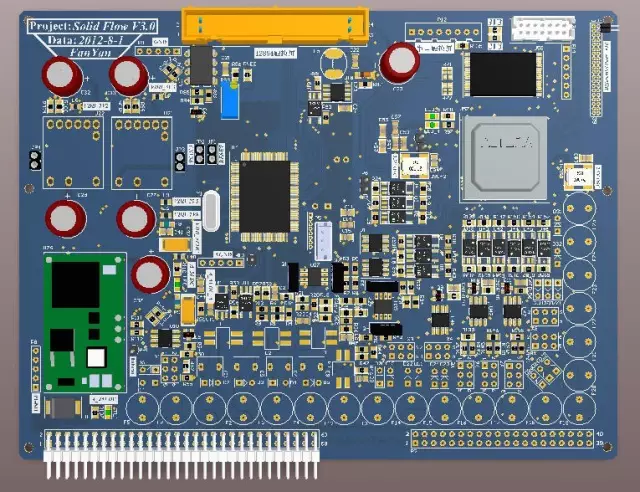

9 U' D: R6 ~7 y2 {3 k' L( D现在还不好说3D功能在PCB设计领域能否流行起来,至少现在没有。但是我认为这个功能的实用性大可搁置不谈,因为这毕竟只是一体化设计概念的一部分而已。不过3D视图倒是给布局连线这种枯燥乏味的工作带来了美感,完美主义者应该会比较喜欢,比如我。下面贴出一些我做过的板子并加了3D模型的图片,之后再提供下载源以及3D模型的一方用武之地。% P# @: W; Y# U% P7 p

$ Q' d' ~' B9 H5 c

( g9 a* L0 ?2 Z" e# g' |

8 u' u3 L7 ?9 g& g% n2 W2 ]

, b* @5 \$ z1 g+ X 9 O9 H* z( [! B3 F 9 O9 H* z( [! B3 F

( [& a3 z ?4 a$ h AD支持的3D文件时STEP格式的,很多元器件厂商都提供的有该文件格式的3D模型,尺寸直接对应到他们的产品。当然网上也有很多人上传了他们收藏或者自己画的3D模型文件,同时我推荐专门下载3D模型的网站。有兴趣的朋友可以搜搜自己想要的模型。

, x4 k0 h. j) m( p! Z3 o! ?+ {- T4 e. r1 J) ~" g: r

除了美感,3D模型能够在一定程度上降低封装错误风险,尤其是在没有实物或者datasheet不全或者封装太多容易看错的时候(我就碰到过),而3D模型是别人按照实物尺寸用三维软件画的,有些模型做的之规范,可靠性并不低,而且能从立体角度观察元件,这对丝印和板子布局,甚至是安装孔的位置都有一定的参考价值。* d% @/ ]$ a+ J! z* f# h

(PS:很多3D模型基本上全是老外做的,而且大部分模型都是国外知名品牌的元器件。比如德国WIMA电容,TDK基础元件等,还有一些合集都标有国际认证标准的符号。当然如果有时间你也可以用SolidWork等自己制作3D模型,机械和模具制图可比PCB制图有赚头。有兴趣的可以研究一下,分享资源和经验)8 G9 Y3 I4 t7 s3 v) q* I* C

' i! A( g8 Q/ F) f8 o

转载:网络/QQ空间 搜集整理:PCB联盟网(www.pcbbar.com) |

|