|

|

​3 ]. h- P4 A6 r6 r/ e; Q ​3 ]. h- P4 A6 r6 r/ e; Q

创龙科技(Tronlong)基于ADI AD9361模块AD-FMCOMMS3-EBZ搭建的AD9361 RF(Radio Frequency)收发测试平台案例,已在如下评估板的AD9361光盘中正式发布,实现了QPSK(Quadrature Phase Shift Keying)数字调制功能。$ Q/ m, t5 J }6 a

" R& E2 [' I$ U: ^

6 @1 `6 ?3 F% D4 A. a4 ](1) TLZ7xH-EVM(Zynq-7045/7100)5 R' U7 X5 r2 D3 o9 n8 _/ q

(2) TL6678F-EasyEVM(C6678 + Kintex-7)

! o( w8 k: g0 G(3) TLK7-EVM(Kintex-7)

( S& q) Q$ Z* C% A, n+ Y2 s% ?

! k o2 |4 e1 R( |# y9 n8 H, L1 I5 J5 d6 \& y/ m4 l

: C* R9 y! S* i, O3 X6 _

) N- d) e; ?( f5 r+ G7 P r" V8 F, ~/ _3 u* r' H0 \$ X

适配TL6678ZH-EVM(C6678 + Zynq-7045/7100)评估板的AD9361光盘也将在近期发布,敬请留意。欢迎各位嵌入式工程师获取产品资料:site.tronlong.com/pfdownload( N3 l& T# U* N# [3 X/ ?

: `4 |* D6 j9 L7 @( f

备注:如需购买评估板+AD9361模块,请与我司联系。案例源码需购买评估板+AD9361模块方提供。2 [* J% X5 b9 A: w, V

& k; V* k! u1 B- }7 h, G# t1 T6 ?: w! o, ]0 ?3 i

AD9361软件无线电模块  ​ ​

' I3 B6 F" s- b! M- C3 s0 bAD9361软件无线电模块(AD-FMCOMMS3-EBZ)

' ~! G0 p) ?5 f, q* f0 M; C/ a6 K3 {4 m% ~: r+ k- @

5 S, T7 j, B) b2 g5 nAD-FMCOMMS3-EBZ是一款高速模拟模块,设计用于展示AD9361—一款高性能、高度集成的RF收发器,适合3G和4G基站以及测试设备、软件定义无线电等RF应用领域。该器件的可编程性和宽带能力使其成为多种收发器应用的理想选择。该器件集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器或FPGA提供可配置数字接口,从而简化设计导入。( y @; ^# t j) n! k

' c! y( O, x) I: G0 Z) Z& E& ?" M. z0 {& j1 p9 l% L

t3 ^/ j5 x- D+ @: w

AD9361芯片工作频率范围为70 MHz至6 GHz,涵盖大部分特许执照和免执照频段,通过对AD9361自身可编程改变采样速率、数字滤波器和抽取参数,使该芯片支持的通道带宽范围为低于200 kHz到56 MHz。

& [- g( W4 ~ K+ n$ ]! \+ Q w* W# I- Z/ X; L# I. u+ G

" ?; p3 n- `: K* Z+ \

# O8 y2 `' k6 \3 j9 A o. V" C9 |& k b6 [0 V, h( x

; m/ U4 O7 F0 F3 O5 i% P* S4 u" Z

( c0 V5 B, W6 B

$ V2 x5 O; Z) s+ y7 s) K

9 f- j3 R' K3 J6 i! u9 V+ n9 l( d. h. O& G

' ?2 M6 Q& k% q3 G$ z$ tTLZ7xH-EVM(Zynq-7045/7100)评估板

/ m5 X+ s$ E$ ^' f0 K; x0 j, ], P! g

# N! L C0 r1 F2 H

$ ]$ X( I5 i/ A! y* S* z8 a4 t4 a, a# d) y

​( |+ ~' y( }8 M. r. s9 M ​( |+ ~' y( }8 M. r. s9 M

l 基于Xilinx Zynq-7000系列XC7Z045/XC7Z100高性能处理器设计的高端异构多核SoC评估板,处理器集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源,评估板由核心板与底板组成。9 R5 K4 A% E/ r$ k( B7 v, W$ H2 C

% l7 o) D, U0 W2 a) q

6 `+ g. u/ H- j( p- z1 N @" t* }l 引出双路千兆网口、四路SFP+光口、CameraLink、HDMI、FMC HPC、GTX、PCIe、USB、Micro SD等接口。

+ M4 h, x c- N/ i4 E: d: u) E

; v% a7 j" A" i% A/ c! r# j

! ^' A8 {9 m" s) [& k2 |7 O# f$ \) U( a2 p, v; R3 O3 c( _

# ^- i4 h, ^5 p* @( p

! k8 A& m0 ?' `' W) ]+ T8 T

' ]. \" A' F! g6 Q! {) PTL6678F-EasyEVM(C6678 + Kintex-7)评估板4 P9 U' f4 ^7 D; A- g' {2 }

1 \' F6 n! u1 s% a

?! z2 m* t5 [# }- h( M* r b% c# y( c8 R1 K

​ ​

* d X- t! U6 \" q+ vl 基于TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP与Xilinx Kintex-7 FPGA处理器设计的高端异构多核评估板,由核心板与底板组成。

, \: T9 k7 F4 W3 v4 @9 a7 _: J, k# i+ g( i& D

2 ]% _: {6 K; H

l 核心板内部DSP与FPGA通过SRIO、EMIF16、I2C通信总线连接。5 r( S; S3 M+ w: u( S0 S! r

: p; ]% e% X" B' V9 y4 G( n7 S8 u4 _8 ?5 l9 P1 s) O

l 引出双路FMC、双路SFP+光口、双路千兆网口、PCIe等高速通信接口。* i& o- e9 {7 }

! g" N3 K7 A. z( ^! ]

' k& C1 a$ H& Z, q1 v1 ^, G

# \: d# Y* F' ?( m, e

! f) E& {/ |* w, R% O

" O" K& L; Q) ?7 C8 n* s+ s" x$ M% ^; C; \$ [5 L) N D

TLK7-EVM(Kintex-7)评估板  ​ ​

# I# r/ L- k: q, [1 M" S

" j# o# Z7 M8 o

4 `) w, b" M4 |9 F: J# U$ fl 基于Xilinx Kintex-7系列FPGA设计的高端评估板,由核心板和评估底板组成。

& t! Z4 n( _. _) `; m4 N) q0 R' l4 V. T

1 {: ~' T+ z. n. [4 j2 v8 l; c

l 引出FMC、SFP+、PCIe、SATA、HDMI等接口。- W9 X) H5 t1 u N

$ w. W2 E1 X+ p @; x( g9 F3 ] g

. v% ]7 s6 H6 j# b4 M( _, o- P6 E0 K! l! H. _; T

8 w4 J8 v5 W) h( Y6 l& U8 |

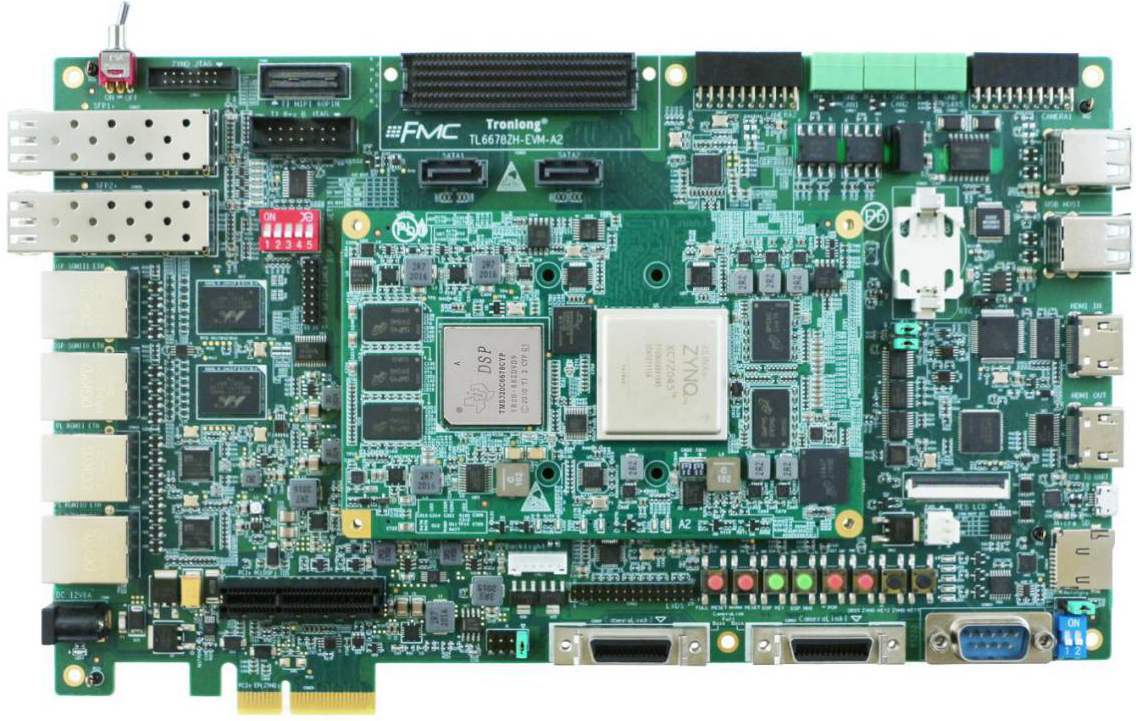

7 |: D) E+ b# T9 s" oTL6678ZH-EVM(C6678 + Zynq-7045/7100)评估板  ​4 U9 J; ~1 j& E. J% y( S1 p ​4 U9 J; ~1 j& E. J% y( S1 p

l 基于TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP,以及Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC处理器设计的高端异构多核评估板。

9 a" }6 S" W h# H. J/ N: N: D! W3 S* g; C/ a

) `. H ]: a) l. |1 m% L! z2 e

l TMS320C6678每核心主频可高达1.25GHz,XC7Z045/XC7Z100集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源。

- P8 Z- U0 a+ r. k% s5 S/ b; I4 r* n& } S/ Z# I5 A# M# C t

4 P: i4 c, l" f1 V _l 引出双路CameraLink、双路SFP+光口、四路千兆网口、双路SATA、双路PCIe、四路USB、双路CAN、双路CAMERA、HDMI IN/OUT、 j5 a. J. a) e! l( z4 t2 C! |# y

LVDS、LCD、RS485、RS232、Micro SD、HPC FMC等接口。

e; t) N0 T; i8 D' G& U e8 E# o; A

$ |+ s) d1 E4 D/ F* s5 ~

6 j! Z- U7 [# N/ O7 a% _* B' X5 h0 m& I0 Z5 g

2 W! \0 T+ E" h# ~. e2 p2 H' _更多推荐1 C4 h4 K8 V1 k( F1 t+ g2 j

# W3 `! {* [# {3 S1 K7 m

AD9361+ ZYNQ软件无线电平台搭建实例

$ Q! C% r& s/ c; N5 w  ​ ​

! N" L4 |6 y" v# q/ p4 f e, F

- R& f' p8 g; p4 s/ }& S+ H: N |

|