|

|

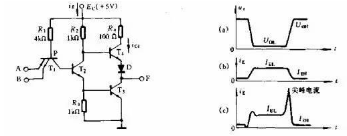

尖峰电流的形成:( F" Z/ o( b3 F- T) Y

( k! c, \. E- l0 K' o( w

数字电路输出高电平时从电源拉出的电流 Ioh 和低电平输出时灌入的电流 Iol 的大小一般是不同的,即:Iol>Ioh。以下图的 TTL 与非门为例说明尖峰电流的形成:3 |7 H/ e& H- w0 ^

+ H, }2 N/ h/ R# X' T$ J# |- g3 ~ ! |1 t" P+ i, d" g( Q ! |1 t" P+ i, d" g( Q

0 \9 r3 Y) T: {

输出电压如右图(a)所示,理论上电源电流的波形如右图(b),而实际的电源电流保险如右图(c)。由图(c)可以看出在输出由低电平转换到高电平时电源电流有一个短暂而幅度很大的尖峰。尖峰电源电流的波形随所用器件的类型和输出端所接的电容负载而异。

* a% V' M7 [8 n c }* ]' F2 ^/ x- _6 T& R1 {5 M' O

产生尖峰电流的主要原因是:, {! ~0 R! z% v+ l- p3 |

: Z4 H+ @$ F2 u5 Y输出级的 T3、T4 管短设计内同时导通。在与非门由输出低电平转向高电平的过程中,输入电压的负跳变在 T2 和 T3 的基极回路内产生很大的反向驱动电流,由于 T3 的饱和深度设计得比 T2 大,反向驱动电流将使 T2 首先脱离饱和而截止。T2 截止后,其集电极电位上升,使 T4 导通。可是此时 T3 还未脱离饱和,因此在极短得设计内 T3 和 T4 将同时导通,从而产生很大的 ic4,使电源电流形成尖峰电流。图中的 R4 正是为了限制此尖峰电流而设计。

* y1 T0 O' f9 u( F2 ?

7 E& ?) N% X/ Q- ]( I低功耗型 TTL 门电路中的 R4 较大,因此其尖峰电流较小。当输入电压由低电平变为高电平时,与非门输出电平由高变低,这时 T3、T4 也可能同时导通。但当 T3 开始进入导通时,T4 处于放大状态,两管的集-射间电压较大,故所产生的尖峰电流较小,对电源电流产生的影响相对较小。

9 O8 ?$ r: X3 b. g

1 v6 Z/ B, a/ U; I# I3 i" d产生尖峰电流的另一个原因是负载电容的影响。与非门输出端实际上存在负载电容 CL,当门的输出由低转换到高时,电源电压由 T4 对电容 CL 充电,因此形成尖峰电流。4 |+ ]5 C0 s) B& X6 Y

. C& M# R$ x$ B2 G; t当与非门的输出由高电平转换到低电平时,电容 CL 通过 T3 放电。此时放电电流不通过电源,故 CL 的放电电流对电源电流无影响。

R0 J5 l7 O% I+ A- i6 p/ b7 J+ h9 L" t: g6 f0 L$ K

尖峰电流的抑制方法:' K# P1 a, i! v3 r' o! @" N5 ?6 t

: u. ]) P2 Q4 u4 G* }. h

1、在电路板布线上采取措施,使信号线的杂散电容降到最小;

4 G- N4 j v5 ^, t O

% u3 i7 b5 A% j5 f5 Y2、 另一种方法是设法降低供电电源的内阻,使尖峰电流不至于引起过大的电源电压波动;

5 L! n* R) X8 T

1 H! \* J# d, R* E, R- @9 A3、 通常的作法是使用去耦电容来滤波,一般是在电路板的电源入口处放一个 1uF~10uF 的去耦电容,滤除低频噪声;在电路板内的每一个有源器件的电源和地之间放置一个 0.01uF~0.1uF 的去耦电容(高频滤波电容),用于滤除高频噪声。滤波的目的是要滤除叠加在电源上的交流干扰,但并不是使用的电容容量越大越好,因为实际的电容并不是理想电容,不具备理想电容的所有特性。

9 {! m8 e' K0 i! X2 p" h% e5 e6 N1 Z9 D0 t9 H

去耦电容的选取可按 C=1/F 计算,其中 F 为电路频率,即 10MHz 取 0.1uF,100MHz 取 0.01uF。一般取 0.1~0.01uF 均可。) u, [+ P6 L3 ~- G

! j9 }3 U6 D0 ?' b3 V放置在有源器件傍的高频滤波电容的作用有两个,其一是滤除沿电源传导过来的高频干扰,其二是及时补充器件高速工作时所需的尖峰电流。所以电容的放置位置是需要考虑的。

* Z- w; i8 l5 O' v2 v! y' V7 Y, d+ G1 m* J1 h3 r f2 P2 W ~

实际的电容由于存在寄生参数,可等效为串联在电容上的电阻和电感,将其称为等效串联电阻(ESR)和等效串联电感(ESL)。这样,实际的电容就是一个串联谐振电路,其谐振频率为:

3 K, U$ B3 z7 w2 [1 d7 N2 G

. G: q6 ~/ m) i& a" L4 J

* Y+ `/ m$ V" z+ |5 B

3 s- ~1 }2 Q! E! P5 R实际的电容在低于 Fr 的频率呈现容性,而在高于 Fr 的频率上则呈现感性,所以电容更象是一个带阻滤波器。; ?, L7 L8 d9 J; l4 Y

' ~' _# V! d: H) |) n* ^' x1 B' [10uF 的电解电容由于其 ESL 较大,Fr 小于 1MHz,对于 50Hz 这样的低频噪声有较好的滤波效果,对上百兆的高频开关噪声则没有什么作用。0 R y1 M7 j, D

) X* a9 S. s1 k0 ?5 J Y, H电容的 ESR 和 ESL 是由电容的结构和所用的介质决定的,而不是电容量。通过使用更大容量的电容并不能提高抑制高频干扰的能力,同类型的电容,在低于 Fr 的频率下,大容量的比小容量的阻抗小,但如果频率高于 Fr,ESL 决定了两者的阻抗不会有什么区别。0 u% M6 H% A$ w! u2 T

3 g) b$ `5 M+ ?& g2 q9 Y! H

电路板上使用过多的大容量电容对于滤除高频干扰并没有什么帮助,特别是使用高频开关电源供电时。另一个问题是,大容量电容过多,增加了上电及热插拔电路板时对电源的冲击,容易引起如电源电压下跌、电路板接插件打火、电路板内电压上升慢等问题。

5 S: K$ q0 i S. s' z' K+ ?& g

! R: z1 N5 r3 o/ K3 s4 \6 cPCB 布局时去耦电容摆放

% d; e7 T: z# G6 e! K2 B对于电容的安装,首先要提到的就是安装距离。容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置。容值稍大些的可以距离稍远,最外层放置容值最大的。但是,所有对该芯片去耦的电容都尽量靠近芯片。

! s2 {4 X9 k8 e+ [1 }/ ^0 h1 e g/ r. h E0 I! G

下面的图 1 就是一个摆放位置的例子。本例中的电容等级大致遵循 10 倍等级关系。

6 t. E5 \5 y( @% J3 A* ~8 P$ [2 d$ ]" ~+ R; \( Q0 |0 W

1 L9 g. L7 O1 a/ O! V* n 1 L9 g. L7 O1 a/ O! V* n

8 H" [) R9 g+ y- _: K

还有一点要注意,在放置时,最好均匀分布在芯片的四周,对每一个容值等级都要这样。通常芯片在设计的时候就考虑到了电源和地引脚的排列位置,一般都是均匀分布在芯片的四个边上的。因此,电压扰动在芯片的四周都存在,去耦也必须对整个芯片所在区域均匀去耦。如果把上图中的 680pF 电容都放在芯片的上部,由于存在去耦半径问题,那么就不能对芯片下部的电压扰动很好的去耦。

. h$ y# W( t+ j, p' ]! n/ } q2 I: ]; q& U0 V* K; o

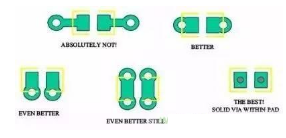

电容的安装

7 [' _8 \4 ^5 E% R8 a3 B在安装电容时,要从焊盘拉出一小段引出线,然后通过过孔和电源平面连接,接地端也是同样。这样流经电容的电流回路为:电源平面 ->过孔 ->引出线 ->焊盘 ->电容 ->焊盘 ->引出线 ->过孔 ->地平面,图 2 直观的显示了电流的回流路径。

7 Q8 c5 g3 n' Z* S4 @6 _) i9 m1 j8 [4 P

7 E8 Q6 K9 k7 S% g5 M* r/ g. L. A9 ^; c, F; f% W$ y. r8 O0 v

第一种方法从焊盘引出很长的引出线然后连接过孔,这会引入很大的寄生电感,一定要避免这样做,这是最糟糕的安装方式。

3 C! b7 q# o& a2 }- Q! }1 m8 s" _" K- _. h/ C

第二种方法在焊盘的两个端点紧邻焊盘打孔,比第一种方法路面积小得多,寄生电感也较小,可以接受。 V5 z3 X" f3 b8 {( m% F" g

0 o4 |! C8 A3 x

第三种在焊盘侧面打孔,进一步减小了回路面积,寄生电感比第二种更小,是比较好的方法。

* [* I3 O8 t) z# h+ X" n

/ ?! l! d' _9 n: _9 t' {! S第四种在焊盘两侧都打孔,和第三种方法相比,相当于电容每一端都是通过过孔的并联接入电源平面和地平面,比第三种寄生电感更小,只要空间允许,尽量用这种方法。最后一种方法在焊盘上直接打孔,寄生电感最小,但是焊接是可能会出现问题,是否使用要看加工能力和方式。8 [# p7 ~4 q, c# _! U& |

$ I2 `* W% u: y! h/ }+ b

需要强调一点:有些工程师为了节省空间,有时让多个电容使用公共过孔,任何情况下都不要这样做。最好想办法优化电容组合的设计,减少电容数量。& E1 m8 z& A5 G

. A2 h, @6 T/ n0 S7 R i由于印制线越宽,电感越小,从焊盘到过孔的引出线尽量加宽,如果可能,尽量和焊盘宽度相同。这样即使是 0402 封装的电容,你也可以使用 20mil 宽的引出线。引出线和过孔安装如图 4 所示,注意图中的各种尺寸。

6 F6 T# g: P- r* h$ l% Y/ {/ W- B* R! A: g5 i2 g- C% [

. p, W4 E" C4 ~2 Q: I . p, W4 E" C4 ~2 Q: I

|

|