|

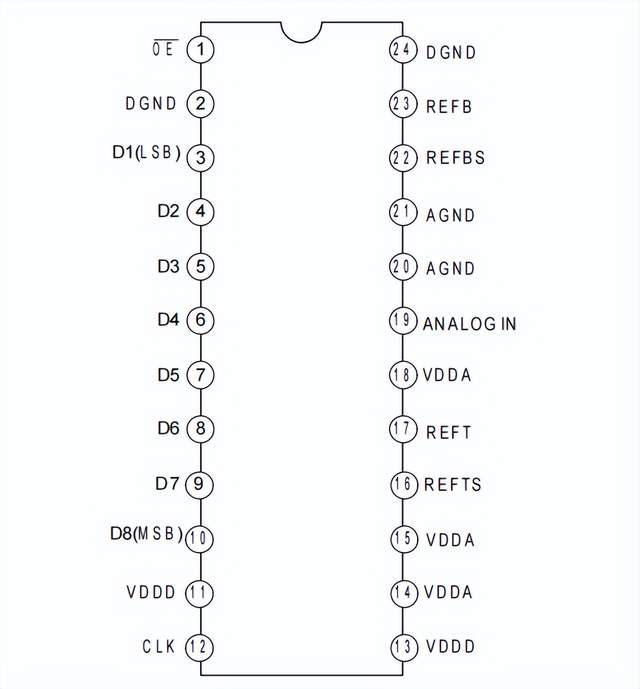

描述 MS5510 是 8 比特,20MSPS 模数转换器(ADCs),同时使用一个半闪速结构。MS5510在 5V 的电源电压下工作,其典型功耗只有 130mW,包括一个内部的采样保持电路,具有高阻抗方式的并行输出口以及内部基准电阻。 与闪速转换器(flash converters)相比,半闪速结构减少了功耗和晶片尺寸。通过在 2步过程(2-step process)中实现转换,可以大大减少比较器的数目。转换数据等待时间为 2.5个时钟。 MS5510 有两种工作模式。模式一使用 3 个内部基准电阻连接 VDDA 可产生标准的 2V 满度转换范围。为了实现此选项仅需外部跳线器。模式二通过内部电阻区产生标准的 4V 满度转换范围。这减少了对外部基准或电阻器的需求。差分线性度在 25℃温度下为 0.5LSB,在整个工作温度范围内的最大值是 0.75LSB。用差分增益 1%和差分相位为 0.7%可以规定动态特性范围。 MS5510 的工作温度-45℃至 85℃。 特点 模拟信号输入范围: -模式一…2V MAX -模式二…4V MAX 8 比特分辨率 积分线性误差 ±0.75 LSB(25℃) ±1 LSB(-20℃-75℃) 微分线性误差 ±0.5 LSB(25°C) ±0.75 LSB(-20℃-75℃) 最快转换频率 20MSPS 5V 单电源工作 低功耗 模式一…127.5mW 模式二…150mW 应用 数字电视 多媒体图像处理 视频会议 高速数据转换 正交调制解调器 MS5510完美替代TLC5510 管脚图

9 g+ E* y/ V) l# D, o' d+ q5 c2 S7 s6 j \

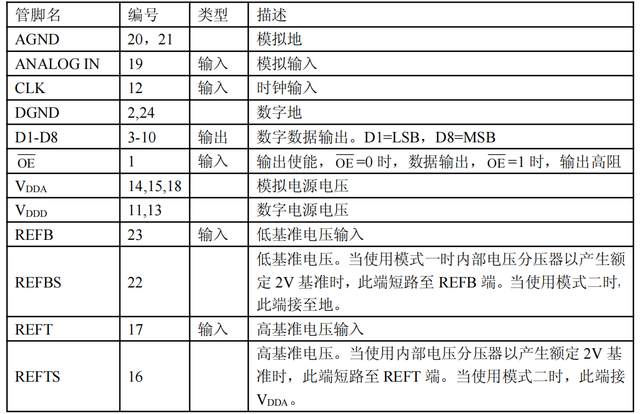

管脚说明图

j" G# U5 L2 [

! v% f: f' q/ O' _* ]) [

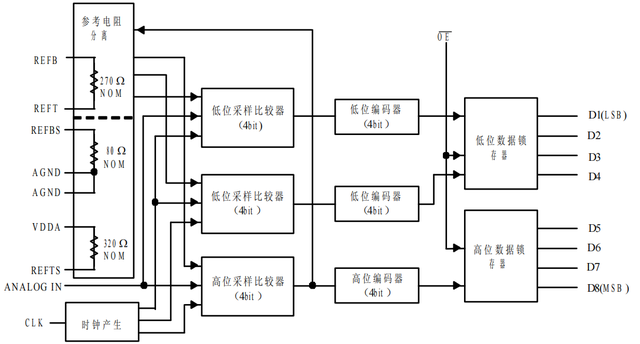

% v2 _7 f- r, [4 Y8 }6 Y结构框图

+ ?" J8 z, m: a( g% M+ c! V% k7 Y! h# Y9 u. V0 x* `! s7 a- c

) n+ k& P6 l. {- G

3 D L/ V; e/ N9 d5 I

1 f2 y. y9 ~3 X. K/ H' m# K, o9 d8 `0 O# E" D5 C. z' u9 \

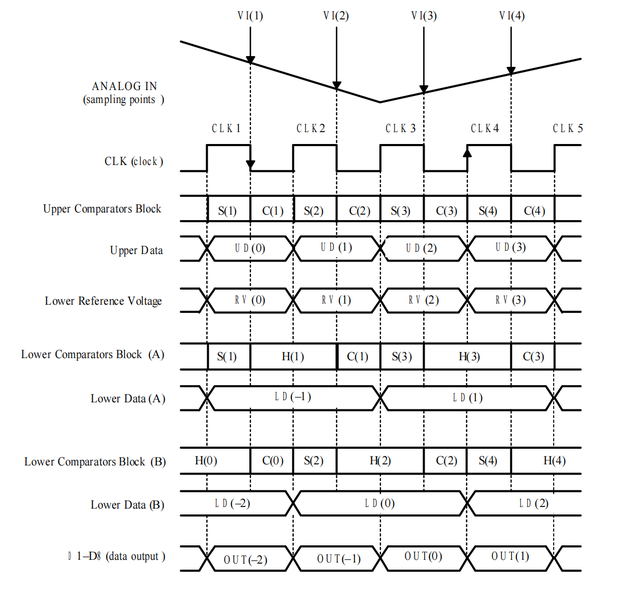

工作原理 MS5510 是具有两个低位比较器块的半闪速(semiflash)ADC(每四位一个比较器)。如图 3 所示,输入电压 VI(1)在 CLK1 的下降沿采样入高位比较器块和低位比较器块(A),S(I)。高位比较器块在 CLK2 上升沿确定高位数据 UD(1),同时,低基准电压(lower referencevoltage)产生与高位数据相对应的电压 RV(1)。低位比较器块(A)在 CLK3 上升沿确定低位数据 LD(1)。VD(1)和 LD(1)在 CLK4 的上升沿组合在一起并输出为 OUT(1)。根据上面所述的内部操作,输出数据滞后模拟输入电压采样点 2.5 个时钟。输入电压 VI(2)在 CLK2 下降沿被采样,UD(2)在 CLK3 的上升沿最后确定,LD(2)在 CLK4 的上升沿被低位比较器块(B)最后确定。OUT(2)在 CLK5 上升沿输出。  8 C' \3 t: m V! V9 q6 c" R 8 C' \3 t: m V! V9 q6 c" R

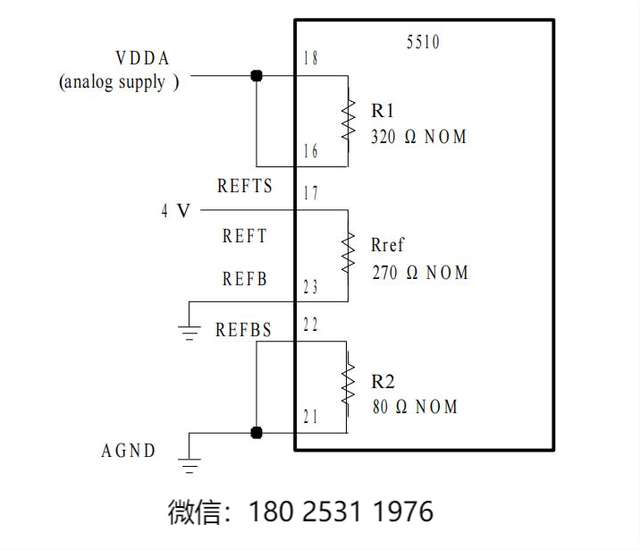

; _' t8 `) o9 N" Y- V. V; e1 l2 k; U内部基准 工作模式一 MS5510 具有三个内部电阻以便能产生内部基准电压。这些电阻连接到 VDDA,REFTS,REFT,REFB,REFBS 以及 AGND。要使用内部产生的基准电压,应当如图 4 所示那样进行连接。这种连接提供用于额定数字输出的标准视频 2V 基准。 工作模式二 模拟输入电压范围为 4V,REFT 接 4V 电压,REFB 接地,其它端口如图所示连接。这种连接通过输入一个 0 到 4V 的 ANALOG IN 信号来提供数字输出。, }% u' W2 `" k: C% L

+ O( } k& W x. }/ i+ W1 ]: c2 i2 x + O( } k& W x. }/ i+ W1 ]: c2 i2 x

8 G+ y5 W6 Q( E2 p( ~

& @+ y, g6 T2 ?% }

应用资料 以下注记是应当与 MS5510 一起使用的设计推荐项。 � 为了减少系统噪声,外部模拟和数字电路应当实际上分离开来并尽可能屏蔽。 � 在整个评估和生产过程中应当使用射频 (RF)试验板或印制电路板 (PCB)技术。 用于测试评估(bench evaluation)的试验板应当镀铜。 � 因为 AGND 和 DGND 在内部未连接,所以这些引脚需要在外部连接。采用试验板时,这些地线应当通过具有良好电源旁路的单独引线连接。为了使拾取的噪声为最小,最好把隔开的双铰线电缆(separate twisted-pair cabels)用于电源线。在印制电路板布局上应用使用模拟和数字地平面。 � VDD 至 AGND 和 VDDD 至 DGND 应当分别用 1μF 电容器去耦,去耦电容应当尽可能靠近它所影响的器件引脚处。对 0.01μF 电容,推荐使用陶瓷芯片电容器。对模拟和数字地,为了确保无固态噪声(solid noise-free)的接地连接,试验时应当小心。 � VDD,AGND 以及 ANALOG IN 引脚应当与高频引脚 CLK 和 D0-D7 隔离开来。当可能时,在印制电路板上 AGND 走线应当放在 ANALOG IN 走线的两侧以供屏蔽之用。 � 在测试与使用器件时,在感兴趣的频率范围内连接到模拟输入端的驱动源电阻应当是10Ω或更小的数值。

, n( f$ |/ T6 c1 l" Z |