|

fpxnh2ftbsv64011393804.gif

9 x( ?* t# B) P( X9 z5 |

9 x( ?* t# B) P( X9 z5 |

点击上方名片关注了解更多6 a$ l2 R/ ?- K `3 c0 H! A

5 H2 `4 [3 a' H: r( j5 z# ?0 x2 s2 h( E% Z* m: x3 m8 F

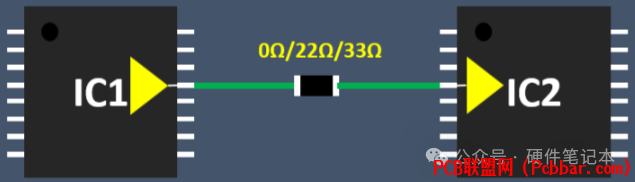

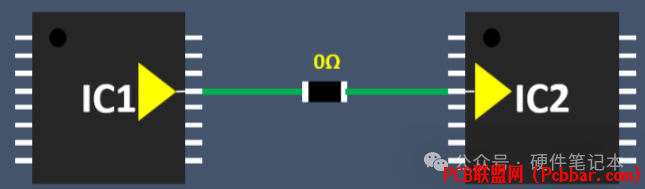

在设计电路的时候,常常会在两个芯片的信号线上串联一个电阻,这个电阻常常是0欧,22欧,33欧或更大阻值的电阻。位置的话有放在信号发射端也有放在接收端的。8 z. m, I$ n) U9 U2 a1 j) U

z11r2rhh50z64011393905.png

! c7 o5 Q2 O! a5 `/ f4 W7 q

! c7 o5 Q2 O! a5 `/ f4 W7 q

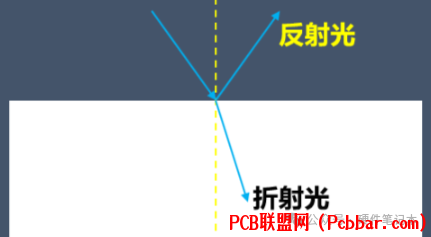

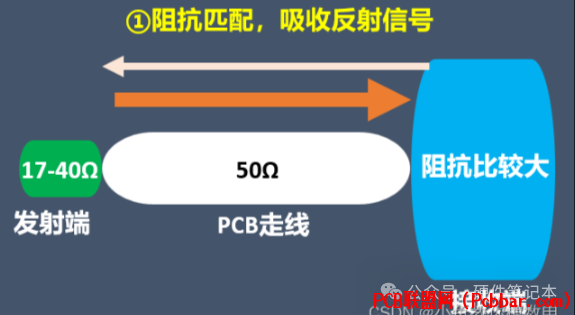

今天就来和大家分享下,信号线上串接电阻的作用。1、阻抗匹配,吸收反射信号当信号频率比较高,上升沿比较陡时我们就需要考虑信号的阻抗连续问题了。首先来看下光从空气照射到玻璃时,除了折射还会发生发射。$ m, R$ R2 k8 F q

zaplt3omdlh64011394005.png

9 n5 {8 Z* y L0 h* Y0 y当信号频率比较高,上升沿比较陡时,电子信号经过阻抗不同的地方时也会产设反射。PCB的单线阻抗一般会设计成50Ω,发射端阻抗一般是17到40,而接收端一般是MOS管的输入,阻抗是比较大的,所以信号在接受端会产生反射,反射的信号又与源信号叠加,这样就会在接收端反复反射,直到趋于稳定。

1 c% x) y& e9 |& P

wdoyu2zqtyq64011394105.png

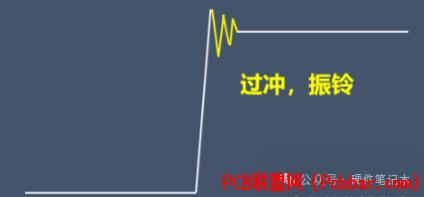

, Q: X+ ~( |0 Q: X信号反射,在实际电路中波形会表现为,实际在电路中的表现就是信号会出现过冲,下冲或者振铃。过冲和振铃很容易产生emc问题或者在接收端产生误码。

" }0 M5 Q O( J5 j/ V- i- z" O- U. E

erjuxcd2ah464011394205.png

$ d" S# F1 o: @9 G9 U% q! T1 C

$ d" S# F1 o: @9 G9 U% q! T1 C

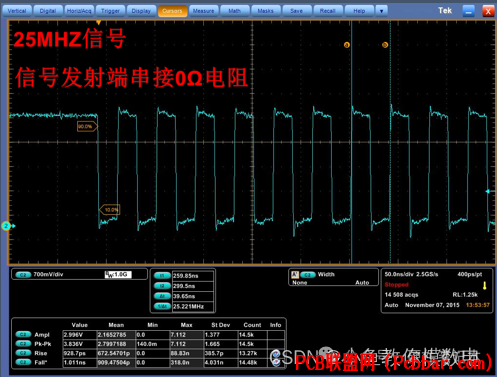

比如这是之前测试的一个25MHZ的一个信号,当加的串接电阻是0欧姆时,可以看到信号的过冲非常明显,% N- q0 p5 G% `; b9 |) P

3czw0eanihy64011394305.png

5 w" P! ^) C0 ~+ f- N

5 w" P! ^) C0 ~+ f- N

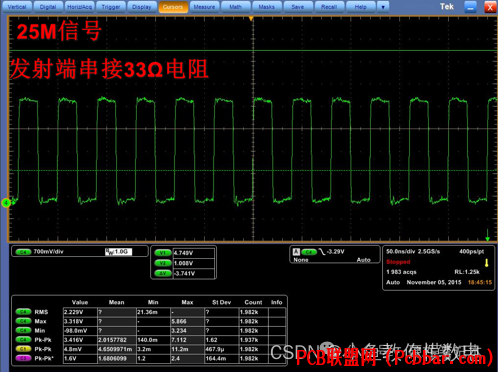

当我串接的电阻为33欧时,信号的过冲有了很好的改善。

: j7 V! b) `" u+ r4 @+ @

ihg3pyox0au64011394405.png

' W- h# J9 X2 s- n$ z& d

' W- h# J9 X2 s- n$ z& d

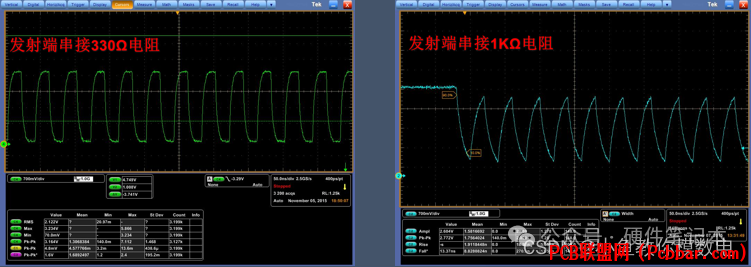

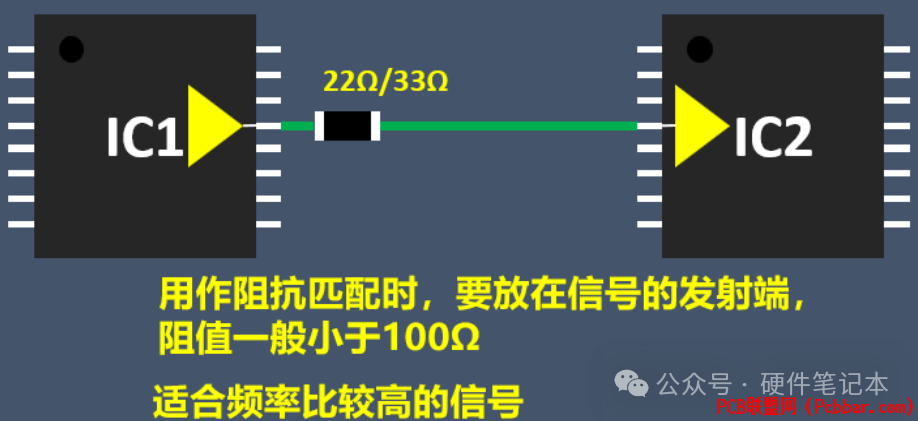

需要注意的是,串接电阻用作阻抗匹配是一般是接到信号的发射端,不能接到信号的接收端,阻值的话一般100欧以内,阻值大了信号会畸变,可能有时序问题。

5 X/ y& z" b9 ]/ t

besxivz0bd364011394505.png

1 B& p- H) z0 k; T, _* [; `

0roerjbbpb264011394605.png

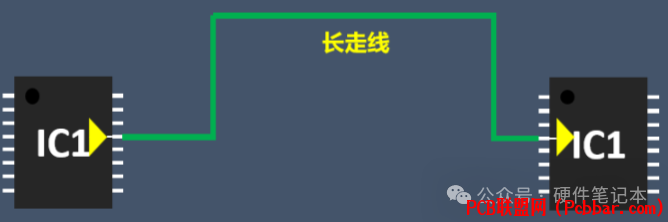

5 O4 u$ v* G# j# G2.吸收干扰脉冲如果两个芯片间的信号线比较长,

1 @, v7 I% V) ^; S

aqc05avrued64011394705.png

" B7 X6 q8 P2 T9 o# m

" B7 X6 q8 P2 T9 o# m

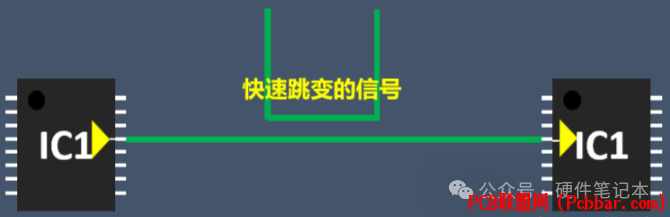

或者走线的时候和一些时钟信号等快速跳变的信号靠的比较近的时候,1 m* z8 {$ u8 `0 f8 Z0 ~

4dla0wyoedv64011394805.png

4 _) ^0 ~2 h0 L( Y' ]这个信号线很容易受到干扰或者信号线上会耦合到一些毛刺或窄脉冲。如果接收端是边沿触发有效,那么信号收到干扰后,必定会有误操作或者脉冲计数变多。* Y* ~3 r. x1 X8 u7 P0 {# @$ {

k25bhbyidhv64011394905.png

5 i+ K' B& |( }7 L0 P$ F9 w- C& ?

5 i+ K' B& |( }7 L0 P$ F9 w- C& ?

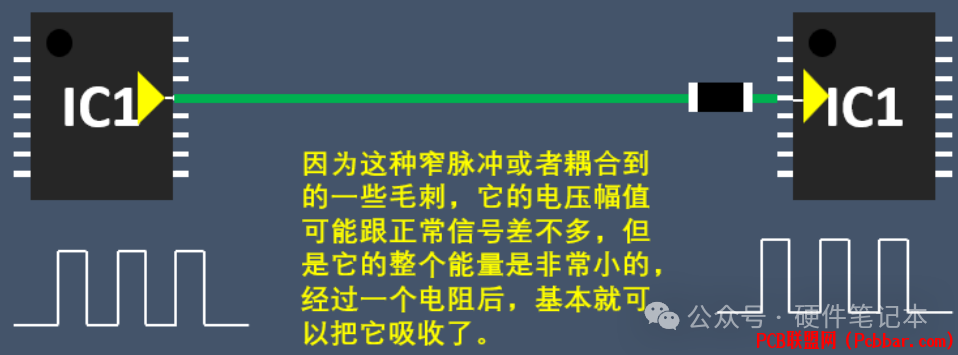

就好比之前做过一个项目,电极输出的脉冲信号经过光耦接到我们的FPGA,FPGA在接受到下降沿了之后进行数据处理。在调试的时候发现,一个周期内,本来之应该有6144个中断信号,但实际FPGA的脉冲信号有时会多余6144,经过查看PCB发现,我们这个线走线比较长,并且中间有一段和一个时钟线隔的比较近,后来在靠近FPGA的这边串接了一个1K的电阻后,脉冲数就正常了。因为这种干扰或者耦合到的一些毛刺,它的电压幅值可能跟正常信号查不到,但是它的整个能量是非常小的,经过一个电阻后,基本就可以把它吸收了。/ q9 T# h- u0 ~2 d! s6 z

ehewtpjvmtx64011395005.png

" j* ?1 ?* [5 F$ }0 Q

" j* ?1 ?* [5 F$ }0 Q

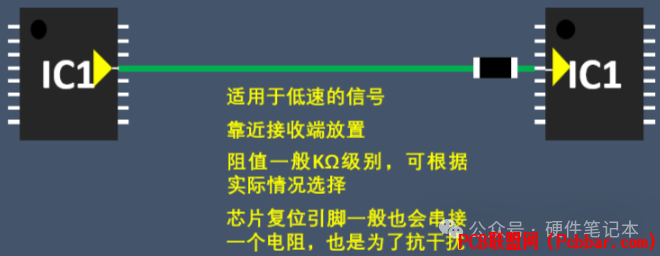

然后复位信号上串联电阻也是这个道理,可以吸收干扰信号或者静电干扰;需要注意的是这个电阻一般推荐放在接收端,并且信号的频率不应太高,阻值的话根据实际情况可以适当选择。3.便于调试测试

, X) _; A) {% a

crxbddttrme64011395105.png

9 `$ y F9 K% E' K) _, h; [- e

9 `$ y F9 K% E' K) _, h; [- e

如果信号两端的芯片都是BGA的芯片或者一些引脚比较密的地方,有时候需要测试这个信号的波形或电平,不串接电阻的话我们将很难测试这个信号的波形,或者电平,这会给我们调试测试带来很多困难。所以对于这种我们常常在信号线上串联一个0欧姆电阻,作为预留,方便PCBA的调试和测试。8 t5 @# D% }* z

l4np0xyc1hg64011395205.png

% Y) M, E2 ?; Z5 q$ v版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。' V4 _+ u c) [/ R: u# X: y

原文链接:https://blog.csdn.net/weixin_42693097/article/details/1277583213 k3 p. x* O, D( a! ]$ ^& `

ipc55ox1thx64011395305.jpg

- ~5 v! d' \5 {' \" X; {# t' u

ctj0grg22fq64011395405.jpg

6 L r+ I3 K9 b声明:

' b0 I/ I1 G$ m. F' p# y声明:文章来源CSDN小鱼教你模数电。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。投稿/招聘/推广/宣传 请加微信:woniu26a推荐阅读▼

, K) o7 w5 Z; y5 U6 J# b电路设计-电路分析' S) |7 o) y, m, q+ v

EMC相关文章

0 r$ @/ p! U0 v; |/ _9 \0 R5 J" F5 r电子元器件

( W) J& `# t0 w0 X- j: F后台回复“加群”,管理员拉你加入同行技术交流群。 |