|

|

引言人工智能、5G/6G网络和高性能计算的快速发展推动了对更复杂半导体封装解决方案的需求。Chiplet设计和异构集成成为满足这些需求的关键方法,与传统的单片系统芯片(SoC)设计相比,提供了更高的性能、更低的成本和更大的灵活性。Chiplet架构的一个关键方面是Chiplet之间的通信,这通常由各种桥接技术实现。本文将探讨Chiplet的概念、不同的桥接技术及其在先进封装解决方案中的应用[1]。0 K d h* h, [2 o; S

* y4 u" p- i& D+ D5 v. I* VChiplet和异构集成简介8 ~4 f% h( y3 i u s- x$ _3 _

Chiplet是可以在单个封装中组合以创建更复杂系统的小型专用裸片。这种方法允许对不同组件使用优化的制造工艺,并可在单个封装中混合各种技术。异构集成指的是用于将这些不同Chiplet组合成一个统一系统的封装技术。; p+ H$ H" v( L) n

qdpuboisyib640876409.png

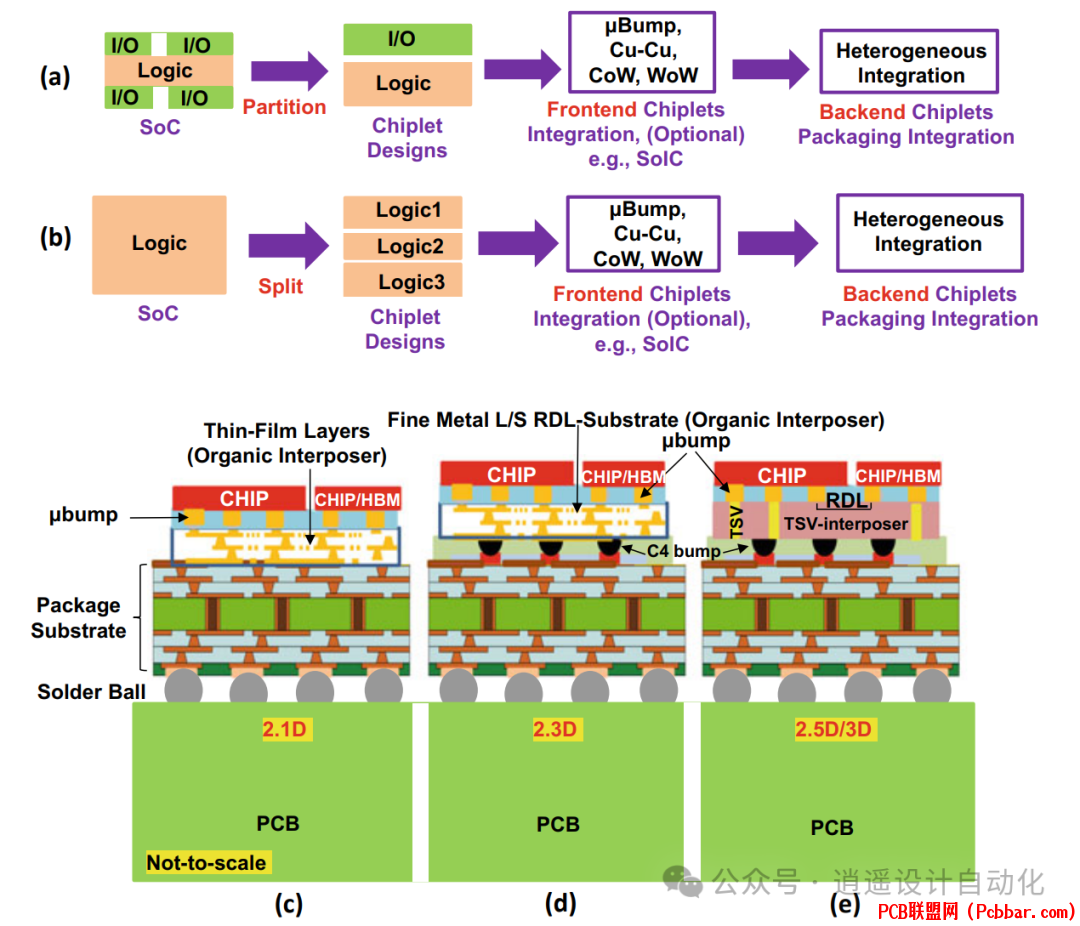

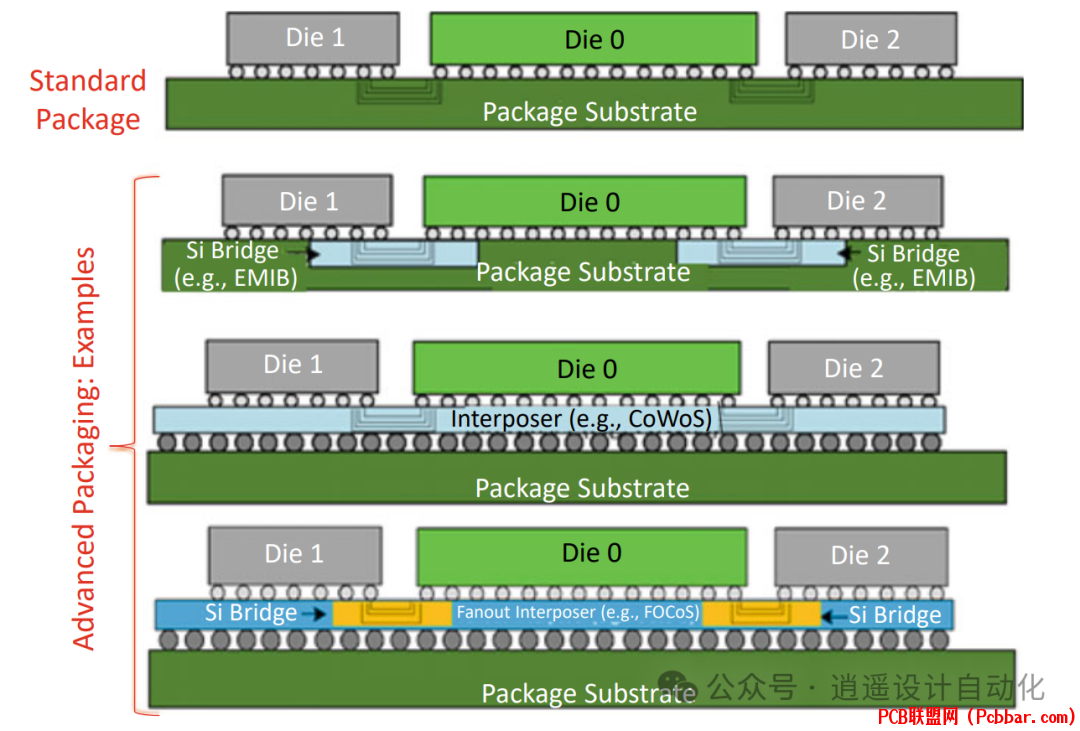

! T7 E" a0 o3 _图1说明了各种Chiplet设计和异构集成封装方法,包括芯片分区、芯片分割以及使用不同中介层技术的多系统集成。( H V: _- Y. M1 |$ o2 T" G

该图展示了五种不同的Chiplet设计和异构集成方法:芯片分区和异构集成芯片分割和异构集成使用薄膜层的多系统集成使用无TSV中介层的多系统集成使用TSV中介层的多系统集成[/ol]& w$ _ ], ~0 y, {- j& F$ x

每种方法在成本优化、制造良率、形状因子和性能方面都提供独特的优势。

, s% P8 |, {& |Chiplet通信的桥接技术为了实现Chiplet之间的高效通信,开发了各种桥接技术。这些桥接作为Chiplet之间的互连,促进高速数据传输和信号完整性。让我们探讨一些目前使用的主要桥接技术。

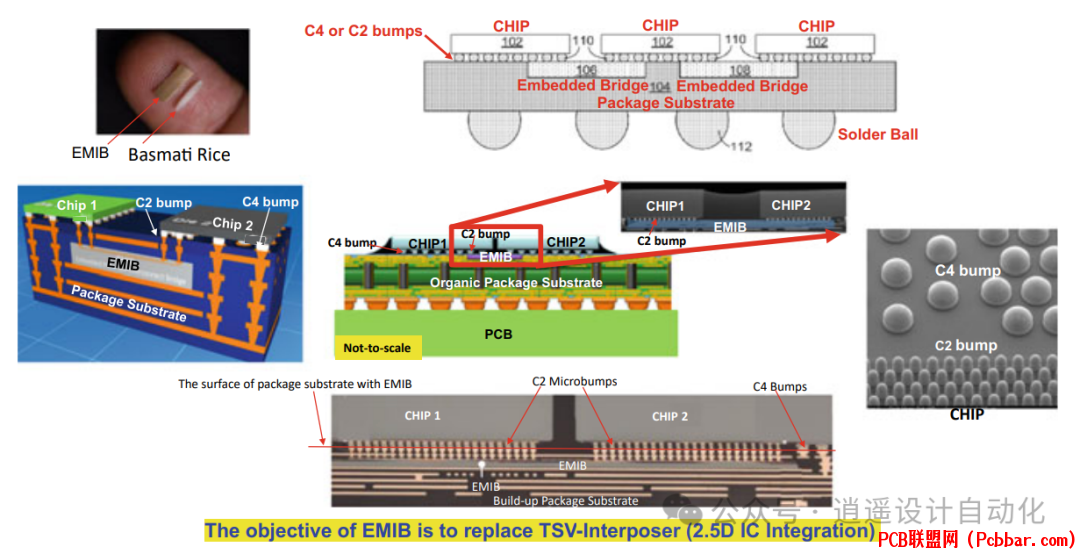

# x0 R2 C* A& Z, I英特尔的嵌入式多裸片互连桥(EMIB)[/ol]英特尔的EMIB技术是Chiplet通信的先驱桥接解决方案之一。EMIB涉及将小型硅桥嵌入到构建封装基板的腔体中。! N" \0 u8 E4 Q; ~ }! R2 h+ ^/ |; E

gvwmmvd4arz640876509.png

6 Y( T& Q O9 t3 h7 a, {

6 Y( T& Q O9 t3 h7 a, {

图2展示了英特尔的嵌入式多裸片互连桥(EMIB)技术,说明了硅桥如何嵌入到封装基板中以连接Chiplet。

: U- R) B* K- ]; J2 [) G" T3 Y7 N6 F- |

EMIB技术提供以下几个优势:消除了对大型昂贵硅中介层的需求实现Chiplet之间的高密度互连允许混合搭配各种Chiplet技术7 x8 ?0 }" ~8 ? e* A; F5 u8 J

英特尔已成功在Kaby Lake处理器和Agilex FPGA等产品中实施EMIB,展示了其多功能性和性能优势。

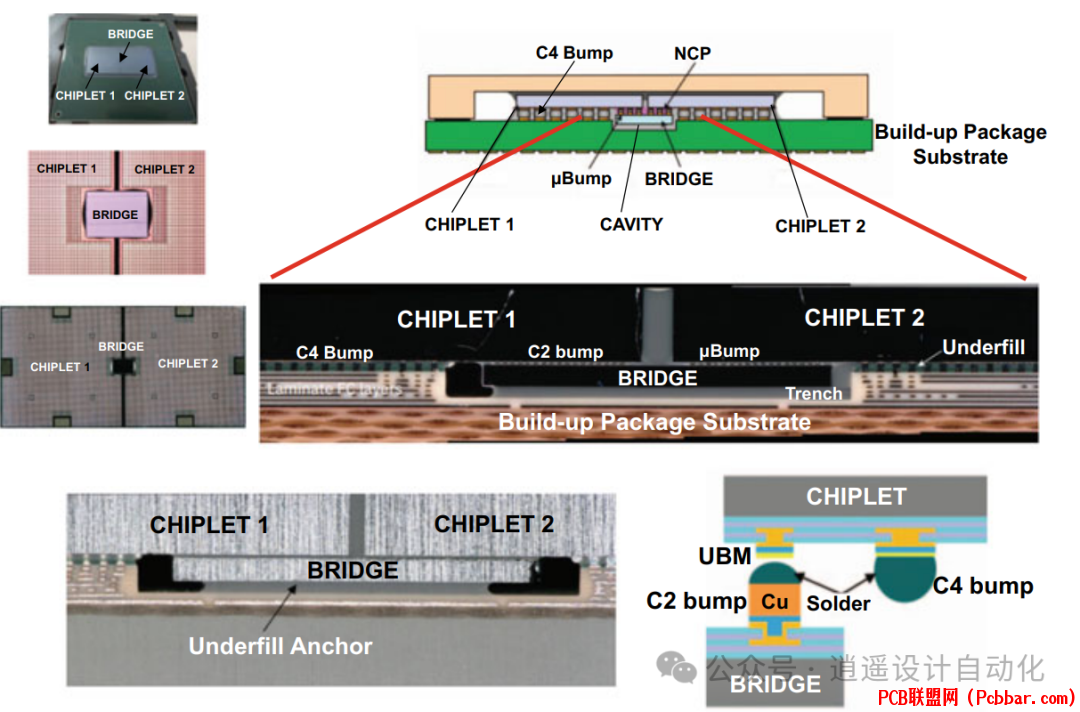

i8 l5 l4 t, d; G6 E: |2. IBM的直接键合异构集成(DBHi)IBM的DBHi技术代表了使用硅桥进行Chiplet互连的另一种方法。与EMIB不同,DBHi不需要将桥接嵌入基板内的腔体中。( F* X6 C, x1 f7 y

wmemxs1yoaw640876610.png

7 v! L# t' [3 f

7 v! L# t' [3 f

图3说明了IBM的直接键合异构集成(DBHi)方法,展示了如何使用标准封装基板上的硅桥连接Chiplet。

- s. Q( g3 s8 Y9 {8 ]9 r4 d. {$ mDBHi的主要特点包括:在Chiplet上使用C4凸点,在桥接上使用C2凸点与EMIB相比,封装基板设计更简单可能降低制造成本( q5 d& Y! d& H/ @: i v

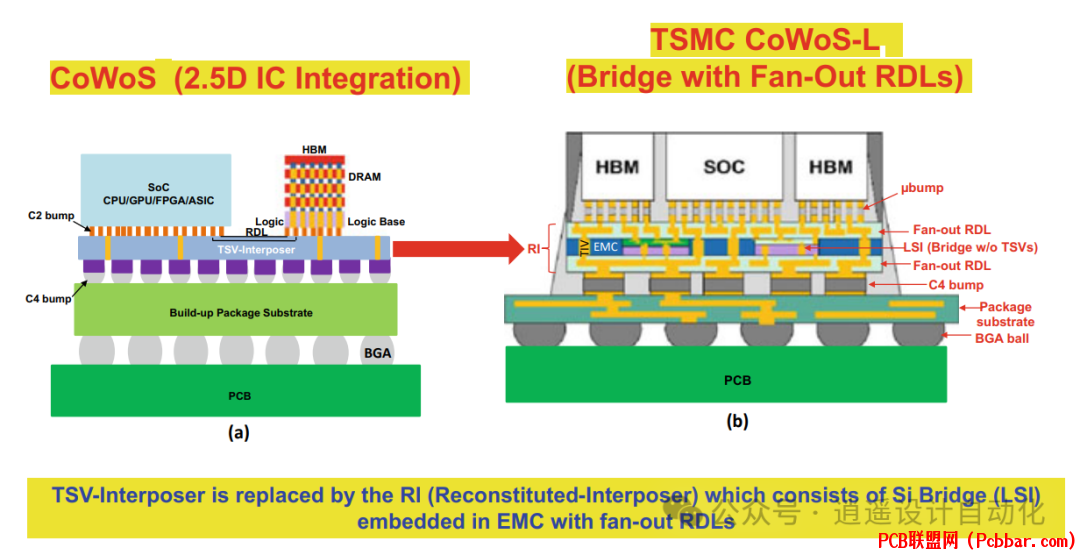

3. 台积电的带局部硅互连的晶圆级芯片堆叠(CoWoS-L)台积电开发了CoWoS-L作为其CoWoS(晶圆级芯片堆叠)技术的演进。CoWoS-L用较小的局部硅互连(LSI)或嵌入环氧模塑料(emc)中的桥接替代大型硅中介层,并配有重分布层(RDL)。

! X; f4 V9 Y+ b( i* J) [5 x

holb354igru640876710.png

; @, z* a2 k5 J7 @) `( N3 o

; @, z* a2 k5 J7 @) `( N3 o

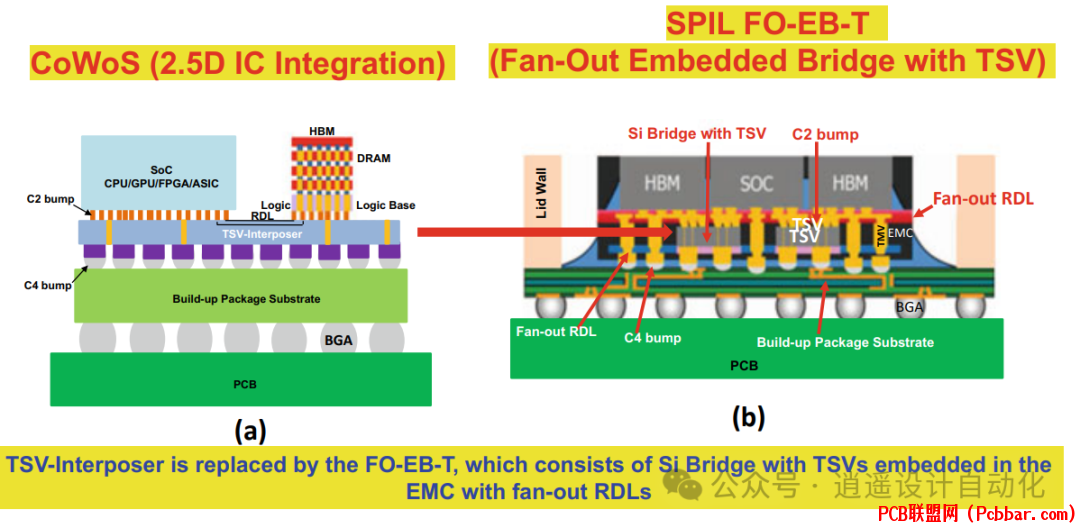

图4比较了台积电传统的使用TSV中介层的CoWoS技术(a)与使用嵌入EMC中的LSI桥接和扇出型RDL的新CoWoS-L方法(b)。

3 t9 G8 ~0 Q3 ?

6 q. B* Q! O7 e& `CoWoS-L提供以下几个优点:由于硅桥尺寸较小,降低了制造成本与大型中介层相比,良率提高保持亚微米铜RDL的高性能互连

b5 d4 J. e& i4. 矽品精密的带TSV的扇出型嵌入式桥接(FO-EB-T)与台积电的方法类似,矽品精密开发了FO-EB-T,用嵌入EMC中的硅桥和扇出型RDL替代传统的TSV中介层。

0 h' H2 R+ f& q

sn3zopwn3wp640876810.png

|1 f" J8 ~ p2 C1 F9 b图5展示了矽品精密的FO-EB-T技术(b)与传统CoWoS(a)的比较,突出显示了用嵌入EMC中的桥接和扇出型RDL替代TSV中介层。

: g* P% N! B/ x2 a( s) HFO-EB-T技术提供:改善了更大封装尺寸的可扩展性通过使用较小的硅桥降低成本将TSV集成到桥接中以增强连接性

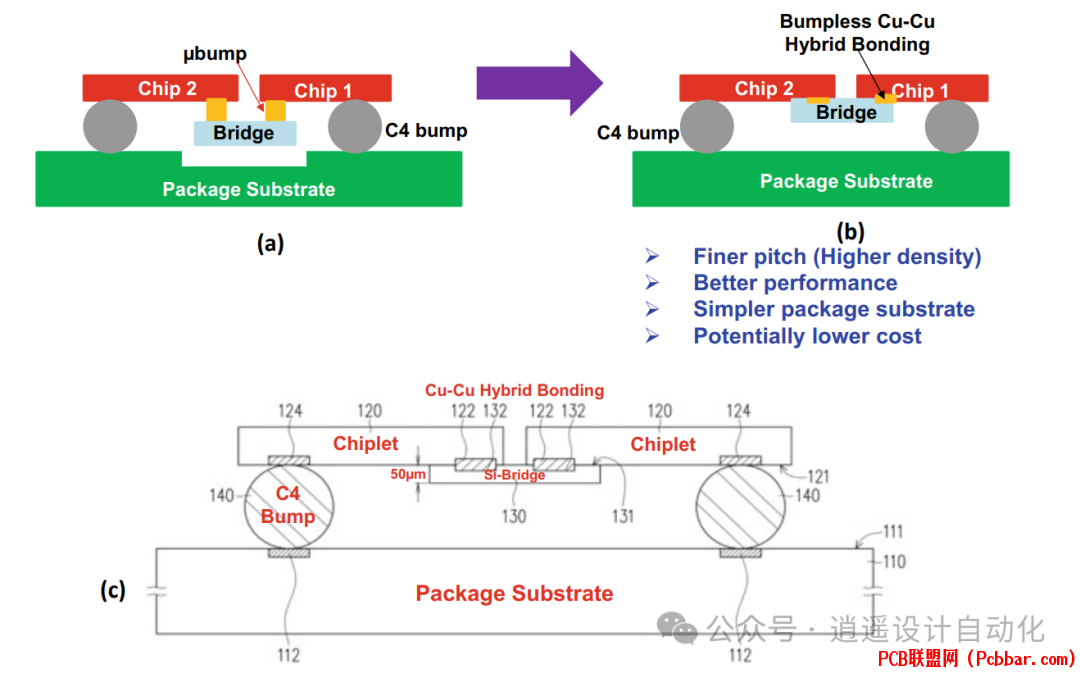

; }; U% P8 U p$ d) K& _混合键合桥接技术桥接技术中有前途的进展是使用混合键合来连接Chiplet和桥接。与传统的基于凸点的互连相比,这种方法提供更高的密度和性能。

. s4 l) d) s. B

0jqzs3bzvea640876910.png

7 P! B3 h* e7 B. R# w图6说明了用于连接Chiplet和硅桥的混合键合概念,展示了与传统凸点互连相比,可能实现更高的密度和更好的性能。

5 e4 c: F& d% G4 e/ K' Q混合键合桥接提供:更精细间距的互连改善电气和热性能进一步缩小封装尺寸的潜力' G0 K4 ?6 `$ y7 n, P8 c

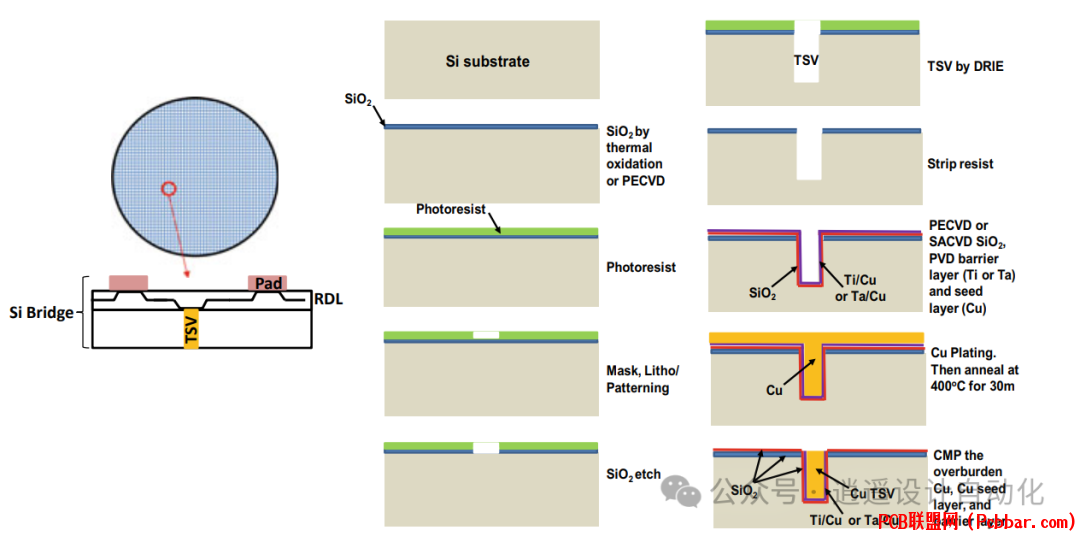

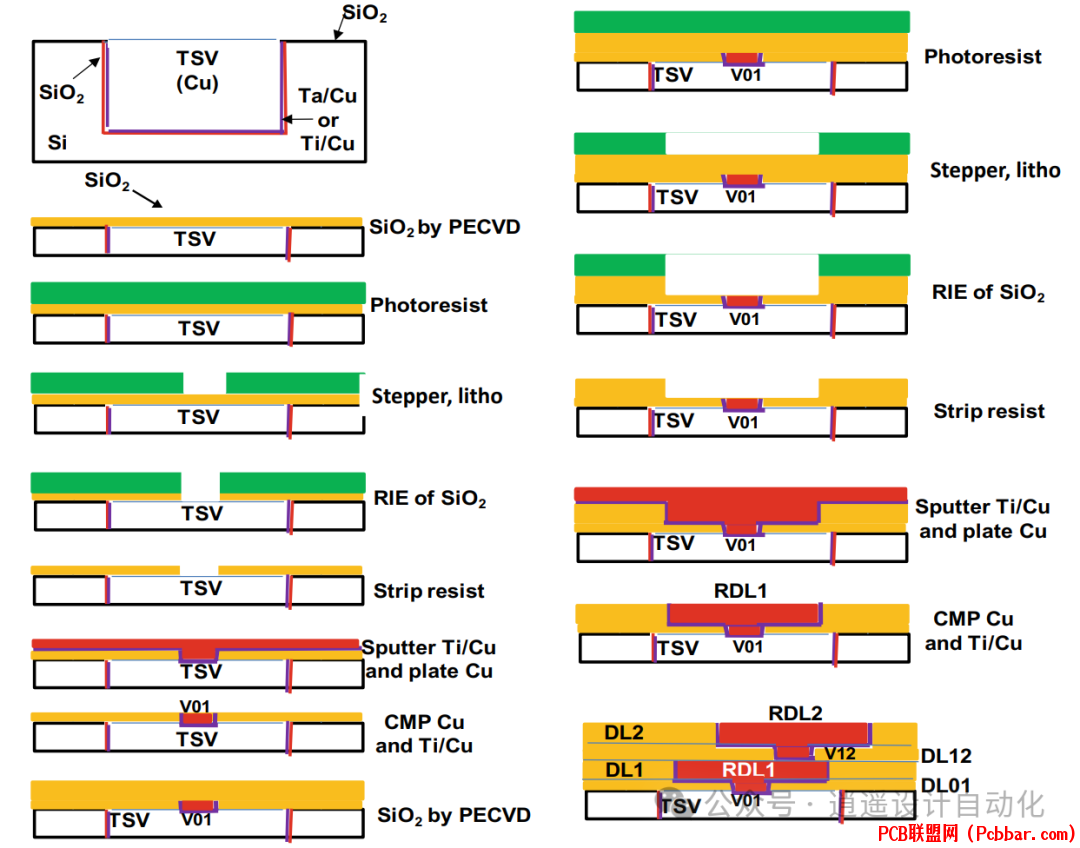

硅桥的制造工艺硅桥的制造涉及几个关键步骤,包括创建硅通孔(TSV)和重分布层(RDL)。TSV制造:

/ ]; L/ C$ ~8 L: P/ {

2m5ndffptcz640877010.png

( k1 x* Z$ M" x8 K; ]

( k1 x* Z$ M" x8 K; ]

图7概述了用于硅桥的硅通孔(TSV)的制造过程。

: T) z3 Y; Z3 k: {# _TSV制造过程通常包括:绝缘层沉积光刻和刻蚀以创建通孔阻挡层和种子层沉积铜电镀填充通孔化学机械抛光(CMP)去除多余铜[/ol]$ z% |. i- ?0 @+ A4 S3 o9 y( S

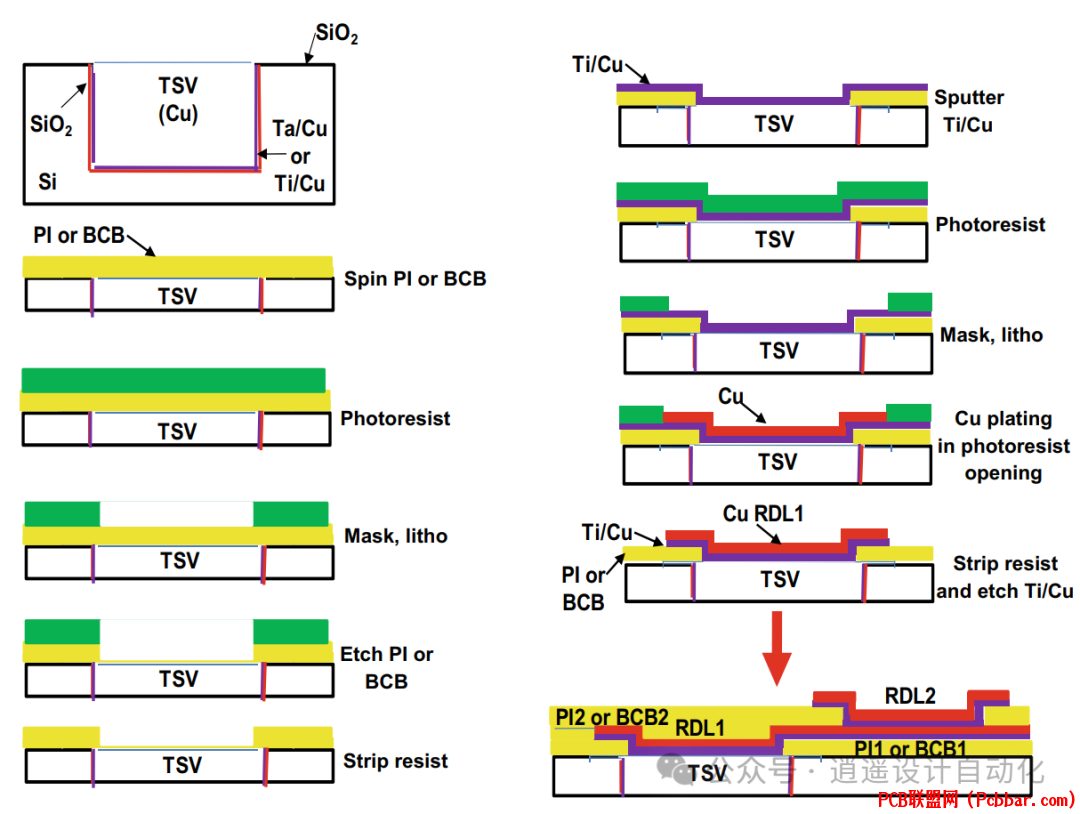

RDL制造:在硅桥上创建RDL主要有两种方法:

& o; n6 E# h/ z1 T; l3 k2 G, l1. 聚合物+铜电镀和蚀刻方法:

) t. X# b. p+ t+ a

dyojgyhgugj640877110.png

! D. S; Z0 w9 s; g4 }' I图8显示了使用聚合物和铜电镀/蚀刻技术的RDL制造过程。9 U: y) z7 d9 S/ R, Y# ` T

这种方法包括:旋涂聚合物介电材料(如聚酰亚胺或BCB)光刻和蚀刻以创建通孔开口铜溅射和电镀蚀刻以定义最终RDL图案

2 q# H2 Q1 k4 }' Z3 F- u* d2. SiO2+铜damascene和CMP方法:( @7 |9 L+ x5 x& F

1axtb4z2qy1640877210.png

9 ]6 k4 F2 E% E) U: S图9说明了使用SiO2介电材料和铜damascene技术的RDL制造过程。/ p C. D& m, }: j# i

这种方法包括:PECVD沉积SiO2光刻和蚀刻以创建沟槽和通孔阻挡层和种子层沉积铜电镀CMP去除多余铜并平坦化表面

5 k, T8 n# \/ K8 P+ ]

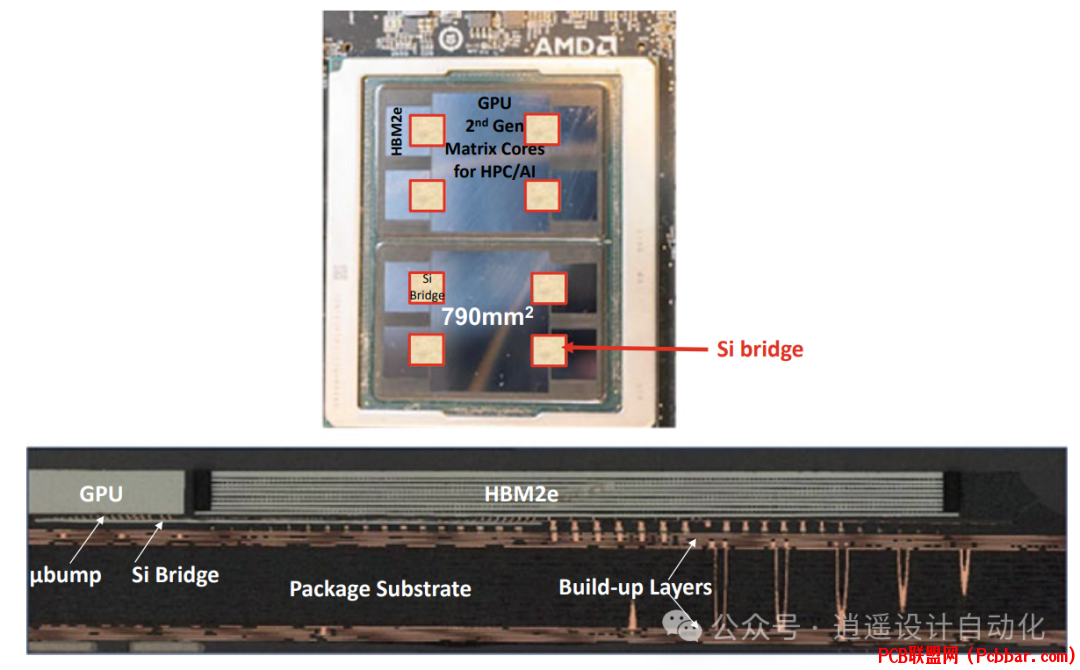

9 \* P$ o; v1 y; A使用桥接技术的先进封装示例几种高性能产品已成功实施各种桥接技术:1. AMD的Instinct MI250X计算加速器:/ a4 y( S6 D4 N$ w) a, ]: ~2 _

ash4jh3itix640877310.png

' G4 C1 N! y" n8 d; s' O

' G4 C1 N! y" n8 d; s' O

图10显示了AMD的Instinct MI250X计算加速器,它使用硅桥将GPU和HBM存储器连接在标准构建封装基板上。! U9 Z2 Z8 o) B2 b8 i: I

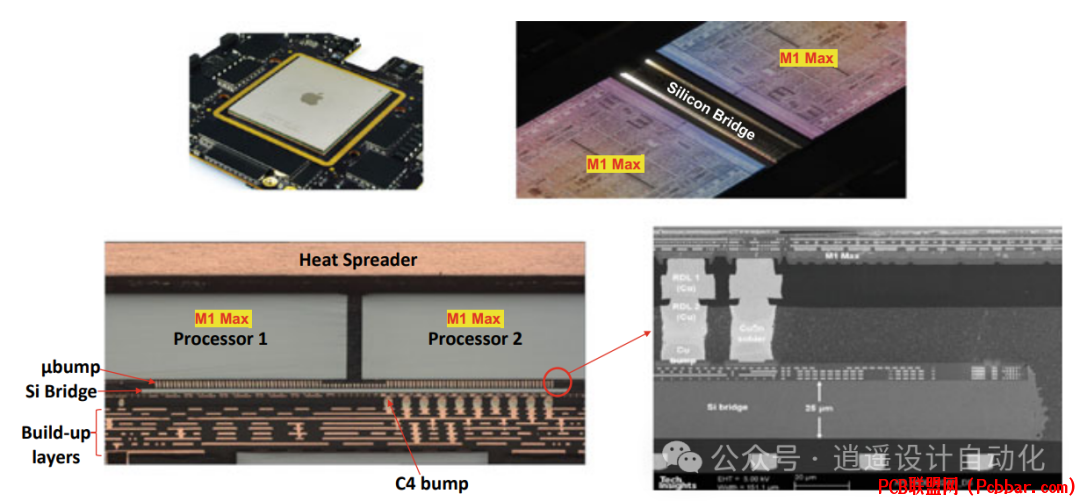

2. 苹果的UltraFusion:

( `" H9 p! V* o! D+ X0 B/ |3 M

rux3tyclcpf640877411.png

! @: d) l+ \- W, n$ G/ _# L" f

! @: d) l+ \- W, n$ G/ _# L" f

图11说明了苹果的UltraFusion技术,该技术使用硅桥在标准构建封装基板上互连两个M1 Max芯片。

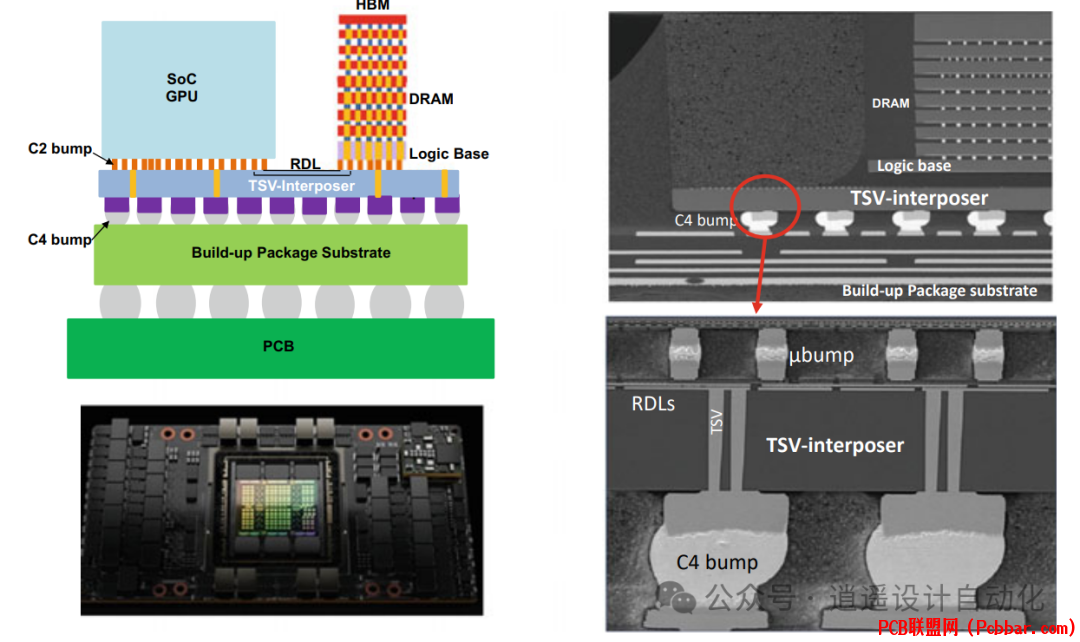

- D8 ]1 l( i! m/ x! I9 y p$ m3. NVIDIA的H100 GPU:

& }3 e8 b; Z$ X$ t9 `

yvijavel1dr640877511.png

* W1 N: i8 t& n. \图12描绘了NVIDIA的H100 GPU,它利用大型TSV中介层将GPU裸片与HBM存储器堆叠连接。" n/ J: t4 T. d0 H

这些例子展示了桥接技术在实现高性能计算解决方案方面的多功能性和可扩展性。

. P5 r# q) Q. K9 ]2 |; r% |" w通用Chiplet互连快车(UCIe)联盟为了促进基于Chiplet设计的互操作性和标准化,成立了通用Chiplet互连快车(UCIe)联盟。该行业组织旨在在封装级别建立通用互连标准。

5 a5 ~" N! ]6 L; B/ }% z2 Q

rnuag5r55b5640877611.png

( O7 W; A1 O- v7 A9 N图13显示了UCIe联盟支持的各种封装方法,包括标准封装和使用不同桥接技术的先进封装。

) y0 s0 Z, ^- Z' z: M; Z, wUCIe联盟的努力将有助于促进:可互操作的多供应商生态系统标准化的裸片间互连改善基于Chiplet设计的灵活性

2 s( R8 C& a, h; z( l: |& R结论桥接技术在实现异构集成封装中Chiplet之间的高效通信方面发挥着关键作用。从英特尔的EMIB到台积电的CoWoS-L以及新兴的混合键合方法,这些技术不断发展以满足下一代计算系统的需求。随着业界向更模块化和灵活的芯片设计发展,像UCIe这样的标准化努力变得越来越重要。通过利用这些先进的桥接技术并遵守新兴标准,半导体公司可以创造更强大、更高效和更具成本效益的系统,推动下一波技术创新浪潮。

) ?+ U/ q+ d5 U* [9 N+ z; }/ G5 b参考文献[1]J. H. Lau, "Chiplet Communications (Bridges)," in Flip Chip, Hybrid Bonding, Fan-In, and Fan-Out Technology. Singapore: Springer Nature Singapore Pte Ltd., 2024, ch. 5, pp. 427-462.

3 c, w+ N% [4 S @0 n+ H' K# e% a0 K8 K! n5 x; d+ A9 D

- END -

, v) K! U) f. L; O7 ~! v& _, S+ P, c8 d6 J. h0 t/ d

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。! S, V. _; u6 g. n' J5 R

点击左下角"阅读原文"马上申请

9 B$ n$ ]& T7 ?

2 h2 J+ w! n0 B; d' T1 S% C欢迎转载' y7 @' E9 r8 @3 M

5 q8 {+ i3 j/ p/ I# T* x# i

转载请注明出处,请勿修改内容和删除作者信息!

& d5 ]; E5 B6 q8 ]- t: A: }

+ U8 O3 i* a6 i. c

& ]+ n' x' f$ {/ G# n

* X5 x% ~( w+ b

ijhlnq12rfb640877711.gif

6 q# S6 r6 Y7 G$ t4 g5 w" Z8 C! @5 h. x! E7 v4 v# s

关注我们6 v5 F; a, Q: [2 A

2 l l8 ^" [* F1 Z

) `+ x$ P0 W j8 D8 X# M3 @& x% j

cj2qepfhfzp640877811.png

. b1 {/ U+ s z

. b1 {/ U+ s z

|

) k# M) {4 M& M7 h

4fpzxf5kxal640877911.png

9 w4 ~$ d1 `; \6 ` |

, _$ E) q/ ]! I) U; V

yqbcx1lyfjq640878011.png

- f$ r( N; A9 E- j4 Q7 c

- f$ r( N; A9 E- j4 Q7 c

|

: \2 L; A8 |) \" c: J$ c* d& K3 ^( a2 H# m

@3 |4 m2 e% ]' ^# Y/ x6 x& ]* G2 i

# A% f. l, k# ?& E0 A

关于我们:

1 B+ X" y7 Y) G$ U7 Y+ S深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

1 t& d7 b5 T, m% i/ U; b8 B

# v9 @! Z" f/ ~2 m$ ahttp://www.latitudeda.com/

0 J4 i8 R v$ P8 @, s$ m, C7 J(点击上方名片关注我们,发现更多精彩内容) |

|