【摘要】上篇文章介绍了PECL/CML/LVDS这几种高速差分接口电路结构、原理,本文将从这几种接口 的互联硬件设计对这几种接口作进一步详细介绍。9 G0 f4 K! v8 j4 L9 T

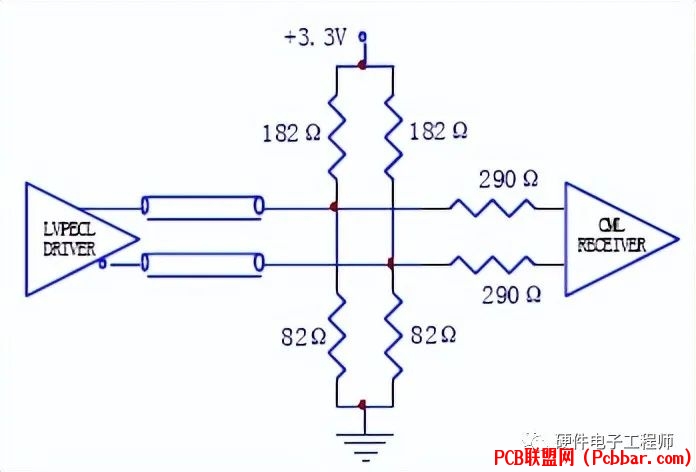

1 LVPECL与LVPECL之间的连接LVPECL 到LVPECL 的连接分直流耦合和交流耦合两种形式

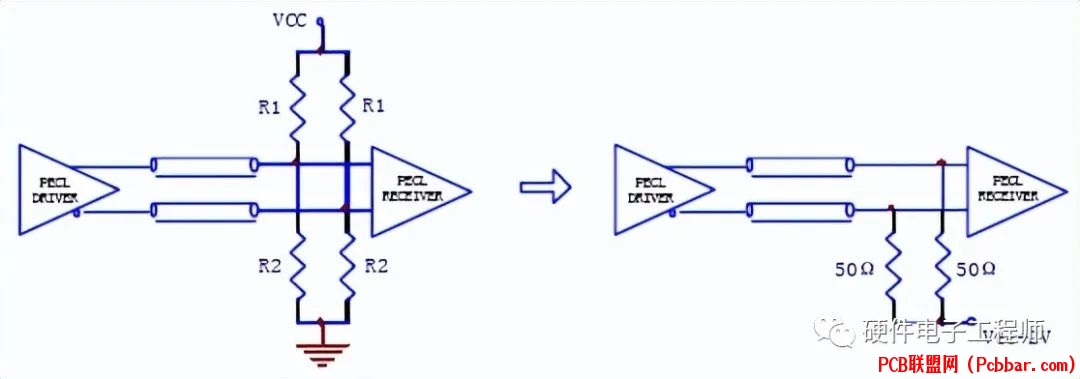

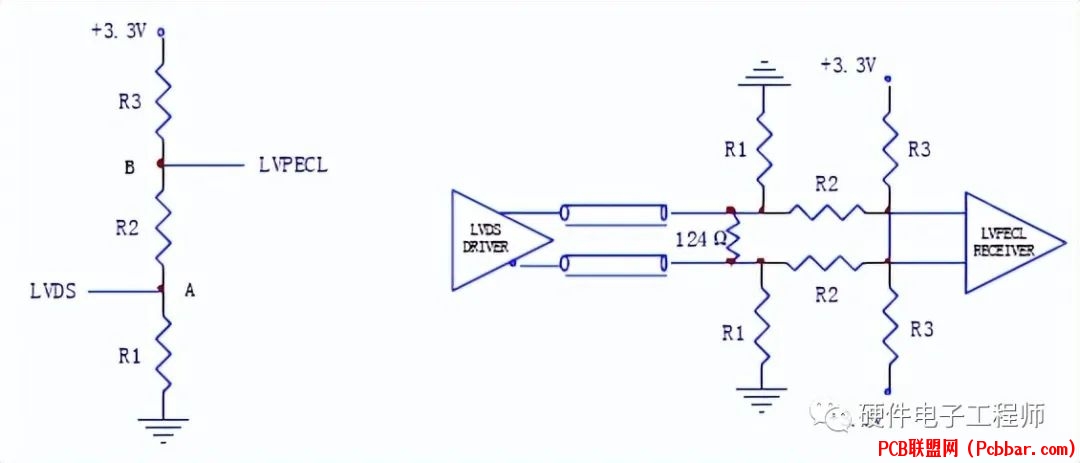

2 x1 E1 i( B! w4 N+ r3 I1.1 直流耦合LVPECL 负载一般考虑是通过50Ω接到Vcc-2V 的电源上,一般该电源是不存在的,通常的做法是利用电阻分压网络做等效电路,如图3.1 中所示,该等效电路应满足如下方程:0 i/ ?7 ?" Y% T

sshr2q3nqey64015176440.jpg

; v& g0 D5 i' K# B; y5 d图3.1 等效电路. [0 b( F# Q* `* C: j. c9 b

Vcc ? 2 V = Vcc R2/(R1+R2)

( F+ [ g% W: b) t! }( O! f: gR1*R2/(R1 + R2)=50Ω

, Z3 [6 \! Y. o+ }* l k" }解上面方程组,得到:. R) L; W- R. f

R1 = 50VCC/(VCC-2V) R2 = 25VCC

" y2 O+ d4 i! w6 ^/ C图3.2 给出了这两种供电情况时的详细电路。$ w/ W7 d) b5 a8 L: C

ghzwjffdcgs64015176540.jpg

- K1 I" d1 D' g

- K1 I" d1 D' g

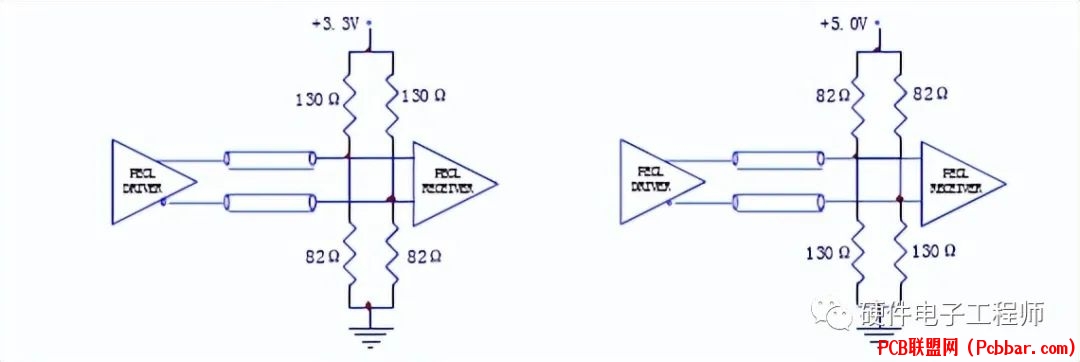

图3.2 PECL电路之间直流耦合

8 r1 }/ w! m3 x, { Z3 Y在3.3V 供电时,电阻按5%的精度选取,R1为130Ω,R2为82Ω;在5V 供电时(此时为PECL电平),R1为82Ω,R2为130Ω。0 C- [$ L% O# H B! ~/ J

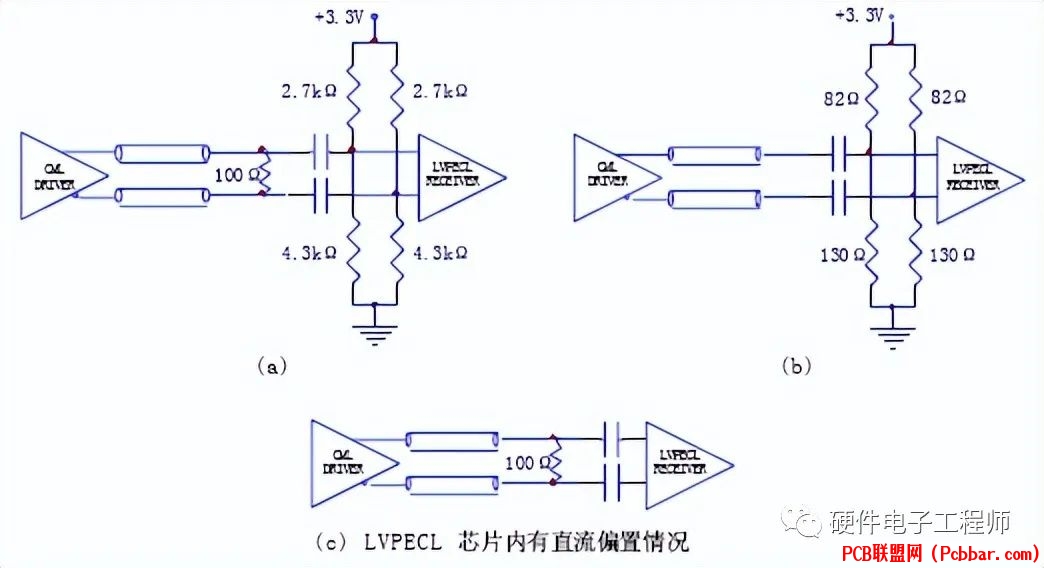

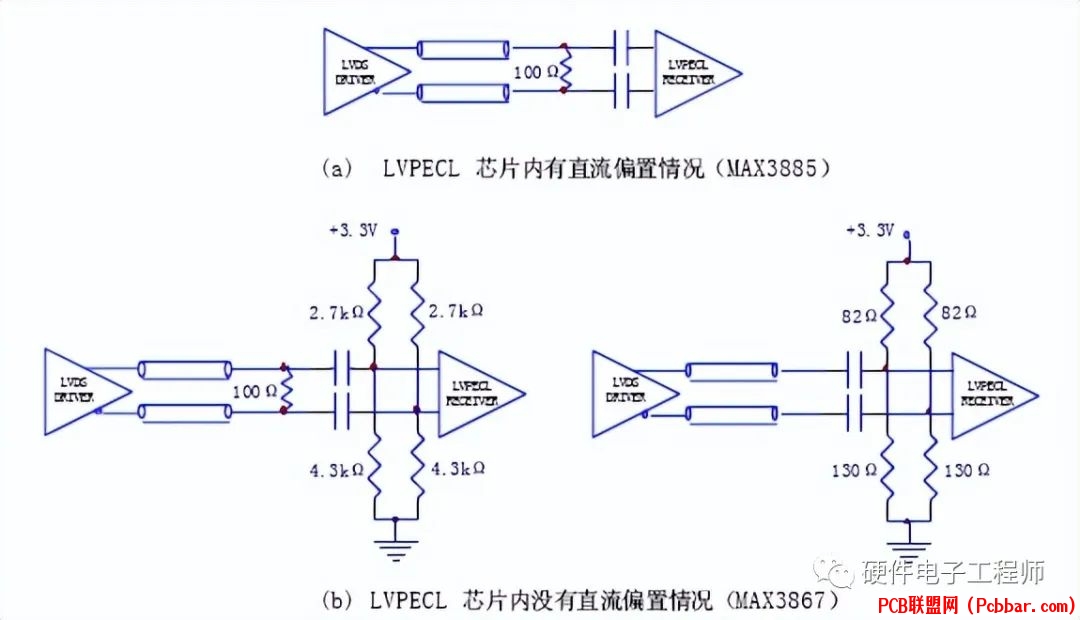

1.2 交流耦合PECL 的输出共模电压需固定在Vcc-1.3V,在选择直流偏置电阻时仅需该电阻能够提供5 O/ b% l H- D3 @

14mA 到地的通路,这样R1=(Vcc-1.3V)/14mA。在3.3V 供电时,R1=142Ω,5V 供电时,R1=270Ω。然而这种方式给出的交流负载阻抗低于50Ω,在实际应用中,3.3V 供电时,R1 可以从142Ω到200Ω之间选取,5V 供电时,R1 可以从270Ω到350Ω之间选取,原则是让输出波形达到最佳。7 W2 f5 ]4 H B. E, K

图3.3中分别给出了两种电路结构,在图3.3 (a)有一个缺点就是它的功耗较大,当对功耗有要求时,可以采用图3.3(b)所示电路结构。8 X8 f( h. M& P7 }7 S. I, O0 r

ddrsb0cxqpd64015176640.jpg

: g/ t& Q6 ~( T- ~$ }" n

: g/ t& Q6 ~( T- ~$ }" n

图3.3 PECL电路间交流耦合% ^/ u2 T/ e7 M* {3 @0 S4 L

在图3.3 (a)中,R2和R3通常选取:6 \. b$ Q4 A4 e+ o6 C1 S

R2 = 82 ? / R3 = 130 ? +3.3 V供电时

. Q W: K2 a% L: L ?, I! {R2 = 68 ? / R3 = 180 ? +5 V供电时

% \, U2 A) C# [4 L, x8 a7 M在图3.3 (b)中,R2和R3通常选取:: h. }0 u5 [6 |5 O4 O' _- H1 Z5 G

R2 = 2.7 K? / R3 = 4.3 K? +3.3 V供电时

2 j! y0 b1 a8 {3 g& OR2 = 2.7 K? / R3 = 7.8 K? +5 V供电时% m D5 U% t8 q

ldxw3pjzjf364015176741.jpg

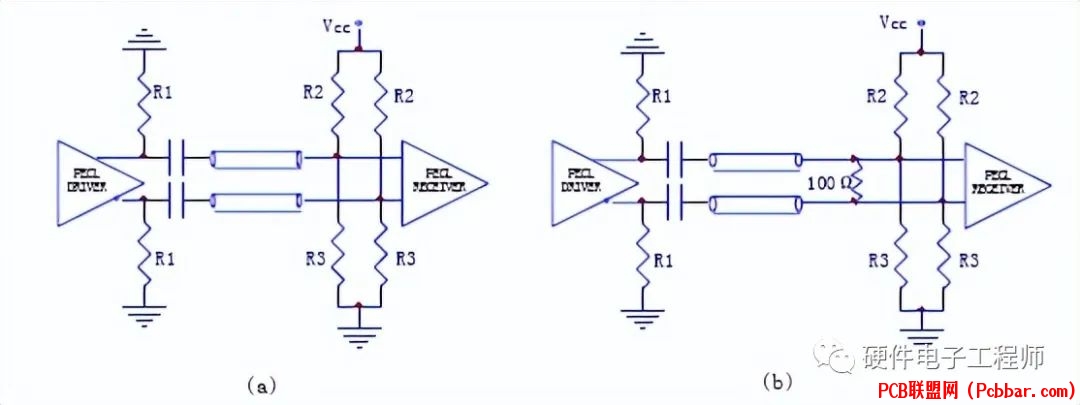

9 V. u+ f8 p; V4 m( D1 p2 LVDS与LVDS接口的连接LVDS 用于低压差分信号点到点的传输,该方式有三大优点,从而使得它更具有吸引力:4 j/ o4 T$ [* D+ ]4 W

(1)LVDS 传输的信号摆幅小,从而功耗低,一般差分线上电流不超过4mA,负载阻抗为100Ω。这一特征使它适合做并行数据传输。

8 e9 t/ B5 F) Q' N+ q(2)LVDS 信号摆幅小,从而使得该结构可以在2.4V 的低电压下工作。+ @8 d* m; S1 Q7 R4 i

(3)LVDS 输入单端信号电压可以从0V 到2.4V 变化,单端信号摆幅为400mV,这样允许输入共模电压从0.2V 到2.2V范围内变化,也就是说LVDS 允许收发两端地电势有±1V的落差。- r3 q# _1 l: B4 I

lhtz2qyzqxr64015176841.png

* V/ `* I5 ~& p- v9 w/ c/ T图3.4 LVDS间连接" q8 t0 N, T$ m0 k

因为LVDS 的输入与输出都是内匹配的,所以LVDS 间的连接可以如图3.4那样直接连接。但在设计时需要确认芯片内部,其接收端差分线对间是否已有100Ω电阻匹配,若没有则需在外面加100Ω电阻,电阻需靠近接收端放置。

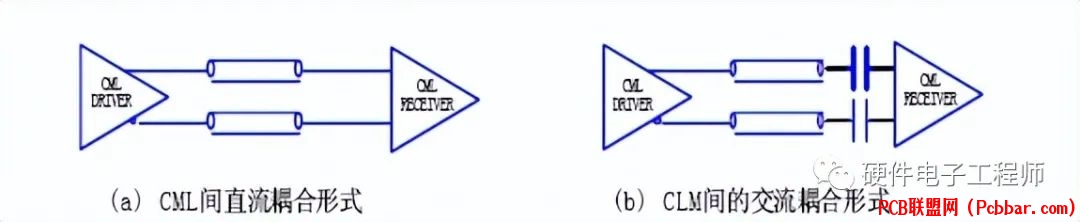

: x5 B$ v5 R$ }+ |. `6 r2 ^3 CML电平之间的连接CML 是所有高速数据接口形式中最简单的一种,它的输入与输出是匹配好的,从而减少了外围器件,也更适合于在高的频段工作。它所提供的信号摆幅较小,从而功耗更低。+ t( f* M) s7 w- S( F; W- l4 w

f0kus5phoiz64015176941.jpg

/ W- Y1 O$ @0 p$ z) I8 X. \

/ W- Y1 O$ @0 p$ z) I8 X. \

CML 接口的输出电路形式是一个差分对,该差分对的集电极电阻为50Ω。假定CML 输出负载为一50Ω上拉电阻,则单端CML 输出信号的摆幅为Vcc~Vcc-0.4V。在这种情况下,差分输出信号摆幅为800mV,共模电压为Vcc-0.2V。若CML输出采用交流耦合至50Ω负载,这时的直流阻抗有集电极电阻决定,为50Ω,CML 输出共模电压变为Vcc-0.4V,差分信号摆幅仍为800mV。

& B; s, E% C$ q* R% t. `3 m, ECML 到CML 之间连接分两种情况:

" P0 f) x8 S. Q( a(1)当收发两端的器件使用相同的电源时,CML 到CML 可以采用直流耦合方式,这时不需加任何器件;. V* m9 G) d7 i: E$ |

(2)当收发两端器件采用不同电源时,一般要考虑交流耦合,如图3.5 中所示,注意这时选用的耦合电容要足够大,以避免在较长连0 或连1 情况出现时,接收端差分电压变小。

( ~: z. H3 f# r- z9 ^: E

yvd1o5vnsb264015177041.jpg

5 [9 K- ]- x8 P( U$ n% P# j

5 [9 K- ]- x8 P( U$ n% P# j

图3.5 CML接口间连接

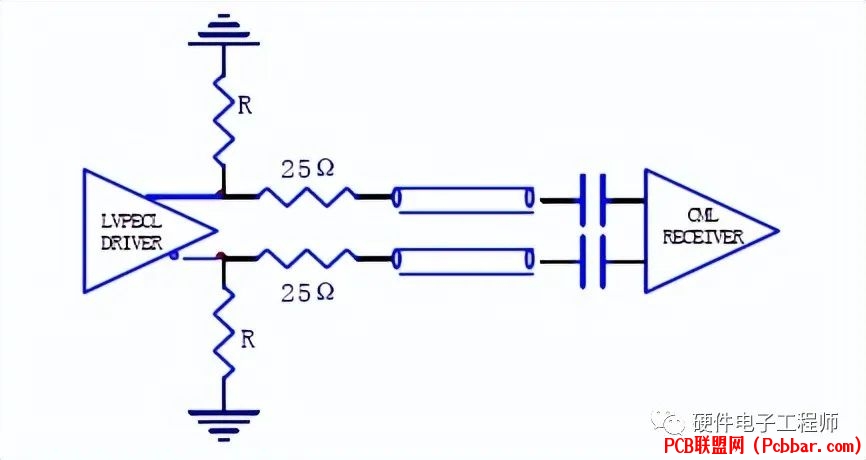

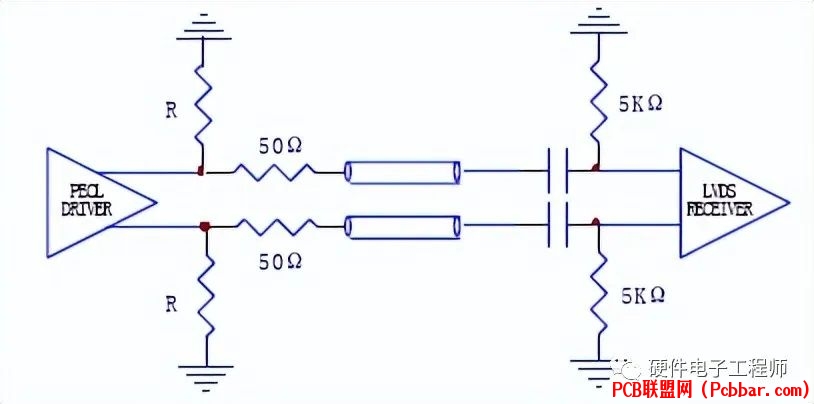

: u6 K3 M1 ^4 \& G9 J4 LVPECL到CML的连接4.1 交流耦合LVDS到CML的交流耦合连接方式如图3.6 所示。在LVPECL的两个输出端各加一个到地的偏置电阻,电阻值选取范围可以从142Ω到200Ω。如果LVPECL 的输出信号摆幅大于CML 的接收范围,可以在信号通道上串一个25Ω的电阻,这时CML 输入端的电压摆幅变为原来的0.67 倍。

# i4 P; P/ j* a% t( q

wpq2zuy311n64015177141.jpg

& s- }1 J% {5 N! x1 @

& s- }1 J% {5 N! x1 @

图3.6 LVPECL到CML的交流耦合连接

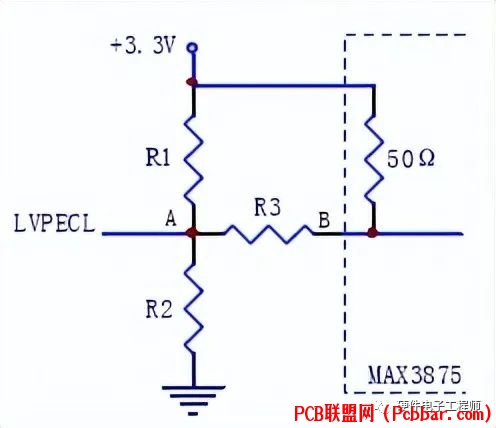

# Y D9 a) z5 H4 Y4.2 直流耦合在LVPECL 到CML 的直流耦合连接方式中需要一个电平转换网络,如图3.7(a)中所示。该电平转换网络的作用是匹配LVPECL 的输出与CML的输入共模电压。一般要求该电平转换网络引入的损耗要小,以保证LVPECL 的输出经过衰减后仍能满足CML 输入灵敏度的要求;另外还要求自LVPECL端看到的负载阻抗近似为50Ω。下面以LVPECL驱动MAX3875 的

9 `, C& D/ O1 r; g$ I+ Q

l0tzxwdq0a264015177241.jpg

/ ]5 d& I: J. U/ e3 z: o- a

/ ]5 d& I: J. U/ e3 z: o- a

(a)直流耦合时电阻网络

2 L5 [3 N( Q2 C6 P+ A% u

pb4pqqpzctn64015177341.jpg

# a3 l6 U" G" B3 K& j: M: q(b)直流耦合连接$ T. c/ d& B$ [3 K# H

图3.7 LVPECL到CML的直流耦合连接

0 Q1 c# |+ ^$ \0 tCML 输入为例说明该电平转换网络。如前所述,电阻网络需满足:

' W+ @! l; d/ N" `- SVA = VCC - 2.0V = R2·VCC /(R2 + R1//(R3 + 50Ω))

6 l+ h3 b. q3 p* n; P! E" rVB = VCC - 0.2V = (VCC·R3 + 50Ω·(VCC - 1.3V))/(R3 + 50Ω)

. {$ j" u+ d$ g' N. `Zin = R1// R2 // (R3 + 50 ?)= 50 ?6 f9 F4 Y$ l/ L* y9 V1 Q

Gain = 50 /(R3 + 50) ≥ 0.125

6 K" ]; L6 p$ N求解上面的方程组,我们得到R1=182Ω,R2=82Ω,R3=290Ω,VA=1.35V,VB=3.11V,Gain=0.147,Zin=49Ω。

m' p2 _6 Q' \) H1 }LVPECL 到MAX3875 的直流耦合结构如图3.7(b) 所示。对于其它产品的CML 输入,最小共模电压和灵敏度可能不同,设计时可修改VB值,再根据上面的公式计算所需的阻值。

& V! f8 R/ c+ S; T; [

thwf1va4cqb64015177442.jpg

0 E+ t8 V ~$ _9 x3 T) p5 CML到LVPECL的连接图3.8中,给出了CML到LVPECL的交流耦合连接。由于CML与LVPECL接口的中心电平不同,

2 E0 J) K. p/ C7 ^* |

s22lwsrmqhp64015177542.jpg

, c; y! Z0 g" B" d+ ^7 q4 @& ^

, c; y! Z0 g" B" d+ ^7 q4 @& ^

图3.8 CML到LVPECL的交流耦合连接

8 ~1 w' [: |3 [通常采用交流耦合,LVPECL输入接口需要外加直流偏置,保证中心电平在VCC-1.3V,图8(a)、(b)分别是外部加直流偏置电阻的连接方式。其中,(a)的连接方式功耗较低。(c)为芯片内已有直流偏置时的连接电路。

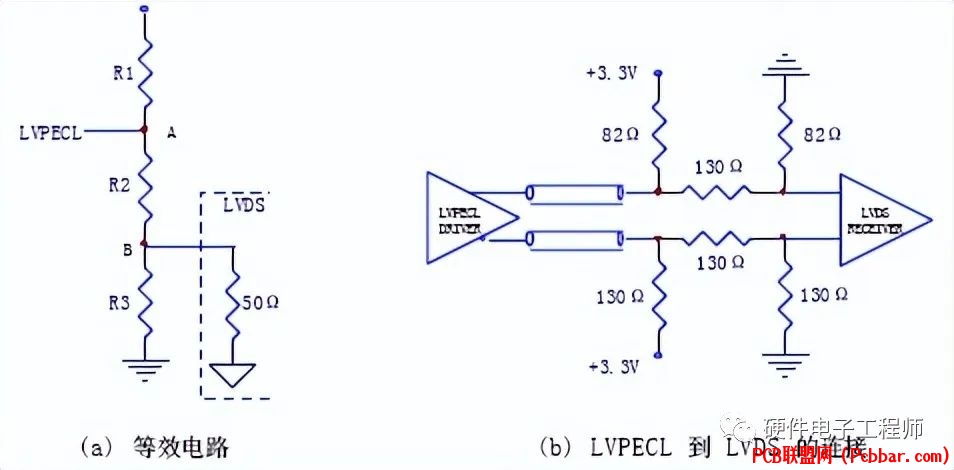

: x" T* ~# _5 E+ ~, F, |, i, H4 s6 LVPECL到LVDS的连接6.1 直流耦合LVPECL到LVDS 的直流耦合结构需要一个电阻网络,如图3.9中所示,设计该网络时有这样几点必须考虑:首先,我们知道当负载是50Ω接到Vcc-2V 时,LVPECL 的输出性能是最优的,因此我们考虑该电阻网络应该与最优负载等效;然后我们还要考虑该电阻网络引入的衰减不应太大,LVPECL 输出信号经衰减后仍能落在LVDS 的有效输入范围内。注意LVDS 的输入差分阻抗为100Ω,或者每个单端到虚拟地为50Ω,该阻抗不提供直流通路,这里意味着LVDS输入交流阻抗与直流阻抗不等.经计算,电阻值为:R1=182Ω,R2=48Ω,R3=48Ω。电阻靠近接收侧放置。6 E8 n5 O) Z- N: \5 I" a

ajerce0jd5u64015177642.jpg

. L7 S) y1 y. \2 e7 C

. L7 S) y1 y. \2 e7 C

图3.9 LVPECL到LVDS的直流耦合结构

# j. C8 F; l" N9 z6.2 交流耦合LVPECL 到LVDS 的交流耦合结构如图3.10 所示,LVPECL 的输出端到地需加直流偏置电阻(142Ω到200Ω),同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS 的输入端到地需加5KΩ电阻,以提供近似0.86V 的共模电压。& {9 g$ `* h, |- N* V1 ?. H6 h

0c4xkfdouza64015177742.jpg

f4 [: s& d% Z, \

f4 [: s& d% Z, \

图3.10 LVPECL到LVDS的交流耦合结构& ^% |" A2 O9 u" f+ z% p4 r5 N' Z

7 LVDS到LVPECL的连接7.1 直流耦合LVDS到LVPECL 的直流耦合结构中需要加一个电阻网络,如图3.11 所示,该电阻网络完成直流电平的转换。LVDS输出电平为1.2V,LVPECL的输入电平为Vcc-1.3V。LVDS 的输出是以地为基准,而LVPECL 的输入是以电源为基准,这要求考虑电阻网络时应注意LVDS 的输出电位不应对供电电源敏感;

* N( v9 w- [8 g& ?3 b2 T另一个问题是需要在功耗和速度方面折中考虑,如果电阻值取的较小,可以允许电路在更高的速度下工作,但功耗较大,LVDS 的输出性能容易受电源的波动影响;$ w4 ]( ^ t4 B# A1 P( G4 r

还有一个问题就是要考虑电阻网络与传输线的匹配。经计算,电阻值选取为:R1=374Ω,R2=249Ω,R3=402Ω,VA=1.2V,VB=2.0V,RIN=49Ω,Gain=0.62。LVDS 的最小差分输出信号摆幅为500mV,在上面结构中加到LVPECL 输入端的信号摆幅变为310mV,该幅度低于LVPECL 的输入标准,但对于绝大多数MAXIM 公司的LVPECL 电路来说,该信号幅度是足够的。设计中可根据器件的实际性能作出自己的判断。# e9 O( c# U8 Z6 L2 F& N2 U) b4 j

pdvu1neagv264015177842.jpg

6 x G5 Q. v* a6 K3 p2 a9 o

6 x G5 Q. v* a6 K3 p2 a9 o

图3.11 LVDS到LVPECL的直流耦合结构

/ I0 g1 G7 h7 n, l& s" b( t+ W7.2 交流耦合LVDS 到LVPECL 的交流耦合结构较为简单,只需要LVPECL输入侧加直流偏置,满足其中心电压的要求。图3.12 (a)、(b)两种为常用到的结构。- j6 p- R& q2 f- r7 ?. ?+ e; X5 J

3t1lvuvtjni64015177942.jpg

( C: i2 l. M, \/ G# Z( j图 3.12 LVDS到LVPECL的交流耦合结构

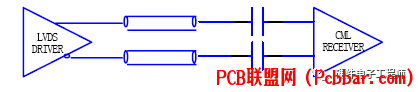

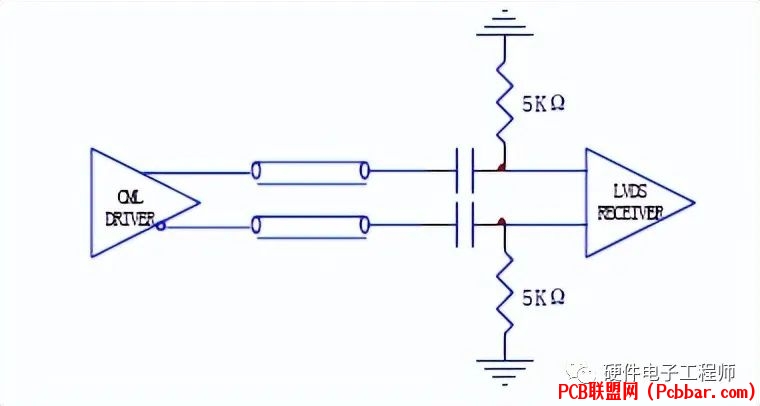

6 j* a! l2 x4 ]$ n! k8 CML到LVDS的连接CML到LVDS的连接通常采用交流耦合结构,图3.13、14给出了两种电路结构,需注意CML 的输出信号摆幅应落在LVDS 的有效工作范围内。

& w: I, J5 E9 n4 H; V$ S

qipu4iuc1ck64015178042.png

2 V4 Z9 G) Q0 ]* u8 ?图3.13 CML到LVDS的交流耦合结构

( L3 }& @ |( w2 g

1hfgx2izg5t64015178142.jpg

. x" a/ q4 w$ Q3 |图3.14 CML到LVDS的交流耦合结构% l1 B# ~5 Y; u8 O& c5 E6 e

9 差分信号设计原则在差分信号传输设计中,不同类型的差分线,其输入输出的中心电平不同,摆幅也不同。但设计中,以下设计原则还是比较通用的。

! ]# @0 L, U. Q; J! j+ v7 n, Q

b5azld05ep464015178243.jpg

6 y8 t7 T' b( |8 l1 @+ J- c

6 y8 t7 T' b( |8 l1 @+ J- c

(1)差分线的正、负端要求等长。一般来说,对于155Mbps的差分线对,其长度差应控制在160mil以内,建议控制在80mil以内;622Mbps的差分线对,控制在40mil以内;其余按速率类推,或根据datasheet推荐的值进行约束。

3 S' K, m/ b. g6 l% @+ S+ ](2)差分阻抗控制在100 +/-10%Ω。7 S8 _; y% ]1 C4 `2 G1 c6 i

(3)数据差分线与其它非时钟信号线的边到边间距应大于2倍线宽,与时钟信号线或时钟差分线应大于3倍线宽。* F% s) U, z) U) Z/ j: W

(4)一般来说,差分线在布线时尽量走内层,且要邻近平面层,表层走线尽量短;- P! |8 E. W8 w

(5)对于高速差分线为减少过孔数目,有时也允许走表层。差分线的过孔数目越少越好,在需要打过孔的情况下,差分线正、负信号线要成对打过孔,也即若正端信号线需要打过孔换层,负端信号线也需要在相应的位置打过孔。一般来说,155Mbps速率的差分线对,其过孔应数目控制在4个以内,622MGbps及1.25Gbps速率的应控制在3个以内;而2.5Gbps速率及以上的差分对,除在BGA下出线必须打过孔以及压接式接插件必须的压接过孔外,在其信号走线的其它位置尽量不要再打过孔。

9 r3 {% u- ~5 ] B: ?(6)时钟信号在不同电平间转换时,尽量采用交流耦合结构。交流耦合电容,选取不宜太小,通常1GHz以上频率选0.01μF,以下的选取0.1μF。泻放电阻和匹配电阻在PCB中的布局和选择。对于有泄放电阻或终端匹配电阻的差分接口电路,泄放电阻R1应尽量放在驱动pin附近,匹配电阻R2和R3尽量靠近接收pin;: K% P3 `2 k ?6 _ L& S% [

(7)考虑到散热和能承受的额定功率,最好选择选择0603封装的电阻,或者0805封装的电阻,不应选用0402及更小封装的电阻,否则应具体计算该电阻上的功耗。 |