【摘要】1 B6 o2 H7 }7 w) P

本案例描述了一个由于CPU和PHY之间RGMII时序不满要求导致通信异常问题,最后通过电感材料(磁珠)对信号相位的移位特性来改变信号延时,从而解决RGMII信号延时不够的案例,实验结果通过。

! A* J6 @6 u/ G1 a+ M

cwajykxcqmu64018456705.jpg

5 A% f3 X1 ~; h6 y9 k. O5 x1 u一、问题描述( A* P$ V5 i- |4 C$ q3 [7 [

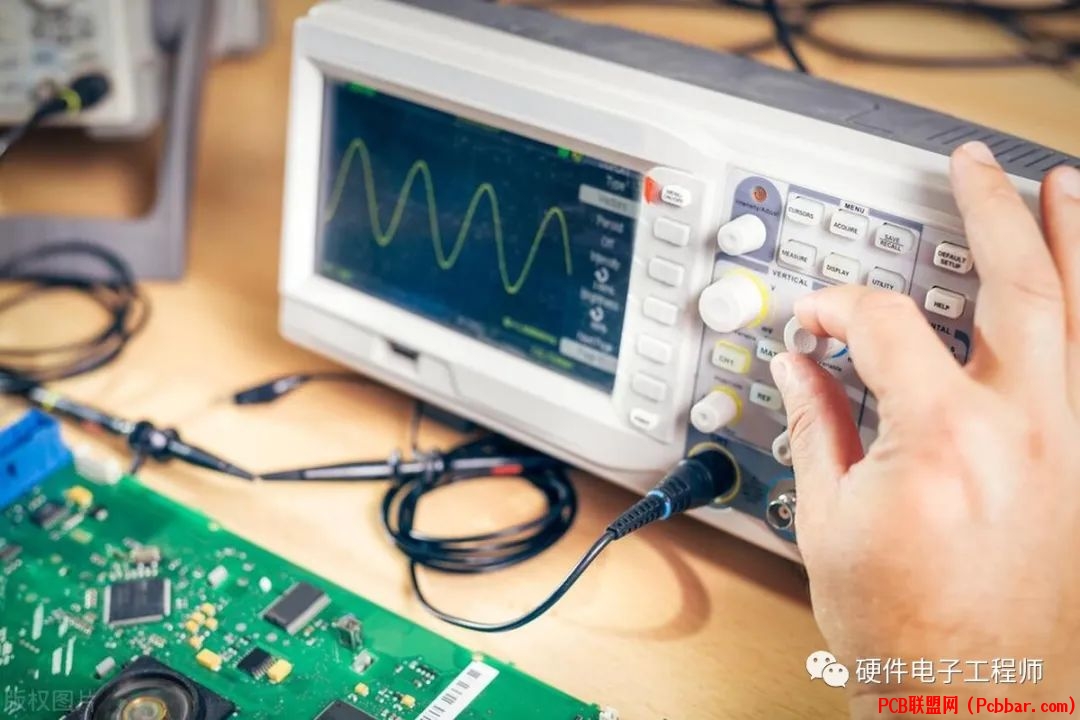

某单板上某物理层芯片和CPU之间的接口,采用的是RGMII方式。在该单板调试过程中,发现物理层芯片发送给CPU的方向,数据一直不通。测量芯片输出的RGMII信号发现,芯片已经有发出时钟和数据信号,但是CPU接收端无法识别,在CPU的RGMII接收寄存器中,接收到的数据个数一个为0 。

4 m9 m& h1 M2 u4 R1 R经实测信号分析,由于时序不满足要求,没法达到接收端建立时间要求导致该问题。如下对该问题进行分析和解决。

- k6 r0 s3 G* y! P) b

1kdngqjwale64018456805.jpg

! }2 y' r% }6 `

! }2 y' r% }6 `

二、问题分析! I% x6 X8 ]9 V! F

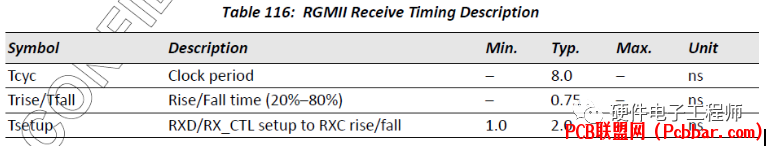

在CPU接收端,RGMII的接收时序如下:: V+ J% }+ X; T& o3 d

so5vbb3ofe564018456905.png

( T. b0 @# q: ?- Q/ {

( T. b0 @# q: ?- Q/ {

图1-1 RGMII接收端时序要求

/ s& M6 k2 R' N) x& Q4 h) P/ S从上面的时序要求看,在接收端,要求RGMII的时钟信号边沿比数据信号的边沿延迟最小1ns,典型的延迟时间是2ns。延迟2ns的时候,RGMII的时钟边沿正好在数据的中间。/ x8 i3 L4 h' m. m2 i9 P, S! j8 D

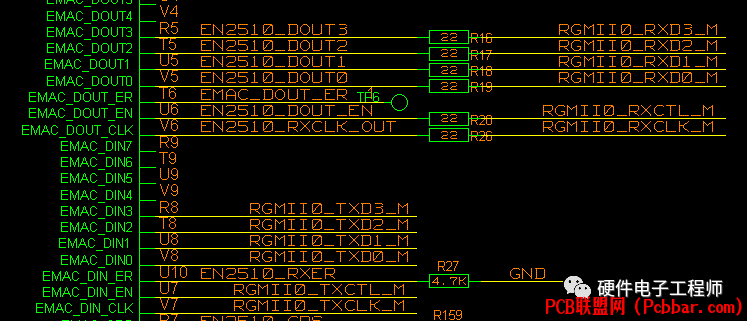

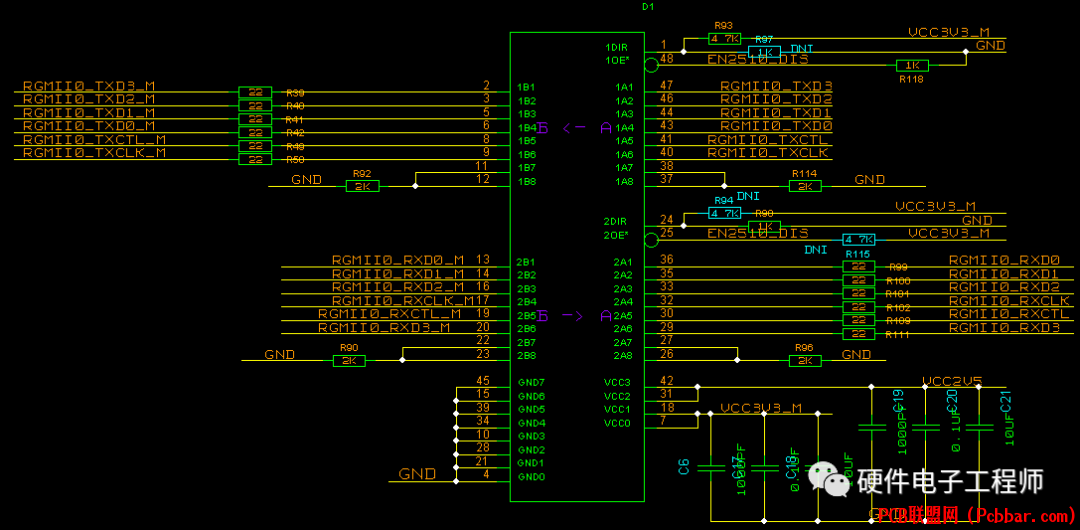

还硬件方案中CPU端RGMII工作电压为2.5V,在物理层RGMII工作电压是3.3V。CPU和物理层芯片之间,通过转换芯片74AVC164245进行电平转换。具体的连接图如下: M, c& {7 j2 L# ~" E

k3gn0erlbm164018457006.png

. D4 L) M8 w9 `3 s

. D4 L) M8 w9 `3 s

图1-2 物理层端的RGMII原理图

/ K) E6 z9 A. w- _& `- j

xhjxylb1dqi64018457106.png

# p/ f1 ?6 X3 `

# p/ f1 ?6 X3 `

图1-3 RGMII接口中的电平转换原理图

' K9 I; q" c/ G

l0bfuucmavc64018457206.png

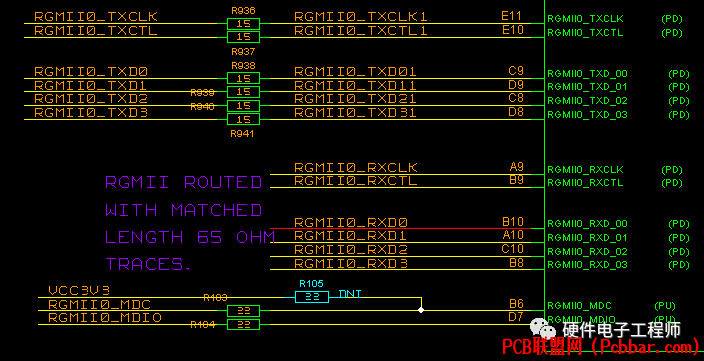

/ m* @# N+ `: ?- n: ?# h/ B图1-4 CPU端的RGMIII原理图9 N( e9 t4 E( B# s- e% ?3 t2 T

在CPU接收端,测量接收到的RGMII时钟和数据,边沿是对齐的,建立时间不够不符合时序要求1ns的延时。在CPU的RGMII控制寄存器中,对时钟延迟时间进行设置,但依然不能达到要求。经与CPU厂家沟通以及实测,这个RGMII控制寄存器能调整的接收时钟延迟,最大只能到600ps。在发送端芯片内,无法对RGMII的发送时钟进行延时设置。

' L1 q; D1 v+ Z1 |8 ^三、问题解决; `5 E$ T2 I: a, e2 r% {

为了验证该问题,首先做如下验证分析:

R; O, b7 L2 k: n, `- E0 O(1)为解决这个问题,考虑到增加走线长度,按照信号在PCB上的传输特性,1ns的延时,PCB内层走线的话,要绕5600mil,明显不现实。

1 l6 R% ?2 o3 x2 i(2)电平转换芯片74AVC164245手册中输入输出信号的延时,在1ns到4ns之间。正好在单板上,74AVC164245芯片有空余的PIN还没有使用,通过飞线的方式,把RGMII的时钟,在转换芯片上,多绕了一次,测试发现,数据可以通了。通过示波器测量信号,发现此时时钟比数据,延迟了大概1.5ns,满足接收端的RGMII时序要求。用这个飞线的方式,做大流量跑流测试,丢包严重,性能不稳定。

; t- A8 m$ J6 b. P7 o通过以上验证分析,在不改板前提下两种方式都无法解决该问题。经分析和头脑风暴,考虑到电感对信号的延时的特性,尝试使用感性材料来实现时钟的延迟。从理论上看,串联在链路中的电感,可以使交流信号相位延迟90度,这里的RGMII信号,时钟是125MHz,延迟90度,正好就是2ns,符合RGMII的接收时序要求。8 [' J6 h- Z9 k. d

把物理层芯片的RGMII输出端的匹配电阻R26,换为100MHz@220欧的磁珠,测试发现,数据可以正常通讯,在大流量,长时间的拷机过程中,未出现丢包的情况。测量磁珠前后的时钟波形,发现时钟结果磁珠后,延时大概1.6ns。更换100MHz@600欧姆的磁珠,时钟延时2ns,但是,磁珠交流阻值越大,对信号的衰减也越大。考虑到时钟衰减和和延迟的结合,使用100MHz@180欧的磁珠,测试发现,时钟信号幅度满足要求,延时1.5ns,能满足要求。经过大流量测试,无丢包情况,通过实验。8 c1 K! M2 \1 L, k

rjbtthz40uh64018457306.jpg

7 ]0 O' v2 t5 O3 o四、问题总结

3 S- A: V* H5 i- t$ e; r$ q本案例利用一个“野路子”解决硬件调试中常见的问题,该解决思路拓宽了我们思维边界。同时也告诉我们当遇到问题时,坚持第一性原则,追本溯源到最底层最原始的物理原理去,定能柳暗花明又一村。 |