这个问题呢我面试至少被面到过两次(主打一个记忆力,被面过的问题都记着仇),问题都给出的差不多:如果读写时钟频率差异过大,会不会有功能问题。我一次回答了有,一次回答了没有,但是都说不出理由,其实我打心底里是觉得没有问题的,毕竟这机制设计的这么好对吧。不过最近系统的把异步fifo的系列写完之后我满脑子都是走线的事,然后突然就好像把这事想清楚了,这篇我试着说说自己的理解啊。先说结论:如果读写时钟频率差异过大,会有功能问题。然后咱们聊聊两点,差异多大是过大?会有什么功能问题?咱们就盯死指针格雷码异步传输这个点看,看什么呢,看每次目的时钟采样是不是只有1比特有跳变。异步fifo里最核心的点就是这玩意,如果不满足了那99%会出问题。

慢时钟打快时钟

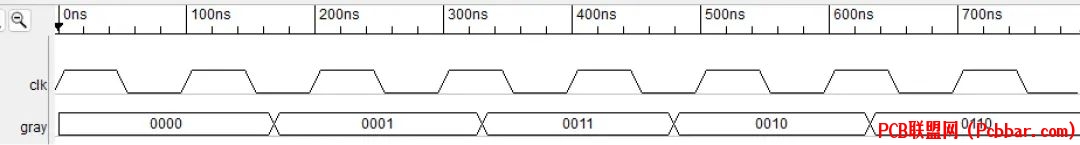

就像下面这个图,格雷码的生成时钟域(不论读写了就)比目的时钟慢:

vqn1w0xc2mm64024562731.jpg

那么容易看出来,快时钟每次采样时,要么采样到和上一拍一样的数值,要么采样到和上一拍相差1比特的值。因此,即使出现亚稳态那么也无非是恢复到正确值或者上一拍的值,符合异步fifo的预期。

快时钟打慢时钟,频率差异不大

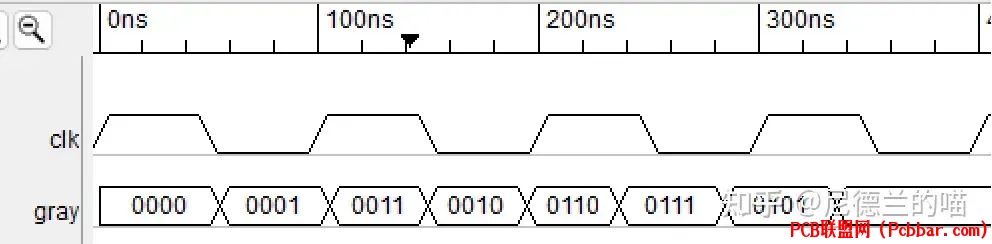

快时钟打慢时钟但是频率差异不大时,最严重的会发生下图所示的“跳点”情况:

5hdmkbd0xnl64024562831.jpg

第一个上升沿目的时钟遇到的是格雷码4'b0001,第二个上升沿遇到的是4'b0110,这一看好家伙跳变了3个比特还得了。不过这个问题老生常谈了,观察一下就会发现,4'b0110并不是从4'b0001跳过来的而是从4'b0010跳变的,因此bit[0][1][3]比特都稳定足够久了(相对于目的时钟上升沿),有亚稳态风险的只有bit[2],而无论bit[2]恢复为0还是1也还无非是当前值4或者真实的上一个值3,都不会影响异步fifo的对外逻辑判断。

快时钟打慢时钟,频率差异过大

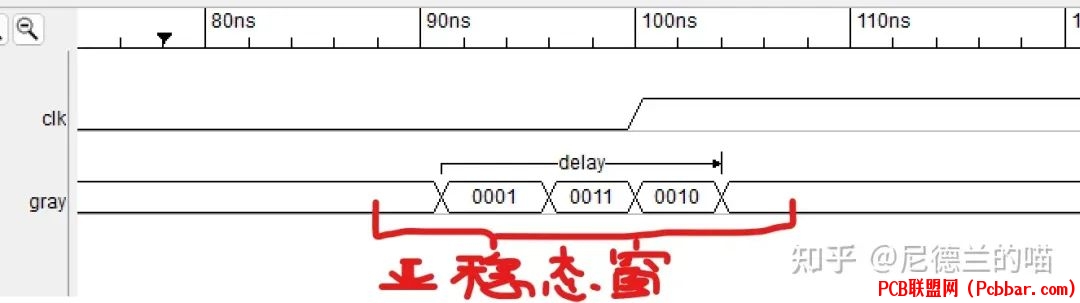

好了,那咱们分析分析是时候是频率差异过大。上面的情况咱们说了,两次上升沿之间采样到的数虽然有多比特不一样,但是就单个上升沿而言其实采样时只有1比特发生了跳变有亚稳态问题,因此不会发生功能问题。那么深入想一下就会发现,如果频率太快了那么就会发生采样过程中不只1比特跳变的情况:

1413k25vpzm64024562931.jpg

亚稳态窗内发生跳变的信号,均可以视作在上升沿采样时存在发生亚稳态风险的信号。因此如上图所示的情况下就存在bit[0][1][2]三个比特都在跳变的情况,因此恢复时指针可能就不知道飞哪去了,自然也无法保证功能正确了。根据这个分析,频率差异过大的判断边界应该是这样:

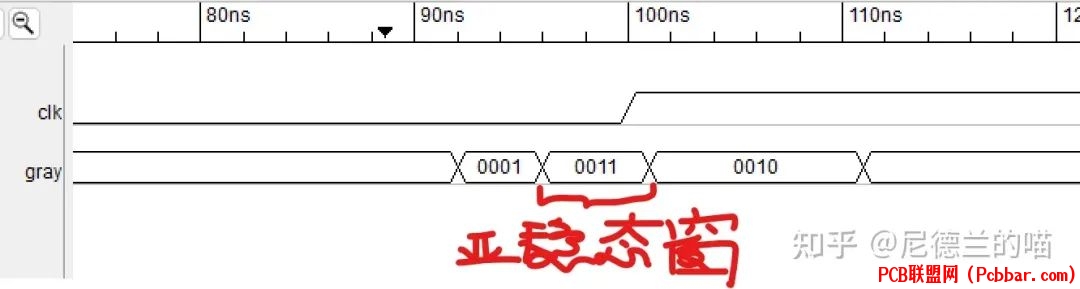

5vdhiwqhcb464024563032.jpg

亚稳态窗内最多最多包含一次格雷码信号的跳变,再多就会发生多比特亚稳态恢复异常的功能问题,所以快时钟的一拍数必须至少撑满一个亚稳态窗。所以咱们估算一下,假设快时钟时钟周期为T_fast,满时钟周期为T_slow,慢时钟周期亚稳态窗所占周期的比例为ratio,那么当:

dooedqutl3q64024563132.png

则会发生功能问题。如果我们假设ratio为10%,那么当快时钟周期小于慢时钟周期的10%即相差10倍时,可能会发生功能问题。

以上均为我自己的理论分析,并未在项目中实践和求证过,仅供参考。 |