|

t11oxekduta64022958132.png

O2 V- X4 M( x8 B h0 S5 T

O2 V- X4 M( x8 B h0 S5 T

# i' |6 L8 T& U z$ m& y( ~

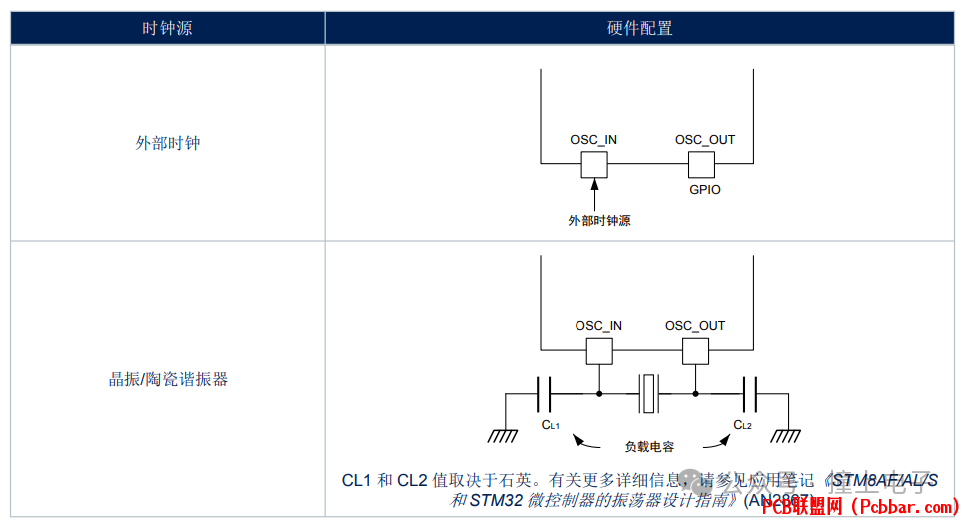

1 HSE 时钟

a6 }+ r( N, O3 b2 Z$ U' a4 s高速外部时钟信号(HSE)有以下几个时钟源: ? HSE 外部晶振/陶瓷谐振器 ? HSE 用户外部时钟,提供 OSC_IN 引脚

" q. |& Z E- w, T, z8 h3 v谐振器和负载电容必须尽可能地靠近振荡器的引脚,以尽量减小输出失真和起振稳定时间。负载电容值必须根据所

# G! k9 \7 C9 v$ Z4 k7 f选振荡器的不同做适当调整。: m& M5 W3 n9 e6 |

24b1xh5ba1e64022958232.png

: |; z- E3 {7 u2 m u/ Y

: |; z- E3 {7 u2 m u/ Y

1.1 外部晶振/陶瓷谐振器(HSE 晶振) 9 L% b5 o ?" i& J4 |6 u

4到50MHz外部振荡器的优点是可以生成一个精度非常高的主时钟。有关详细信息,请参见数据手册的电气特性部分。 1 S2 Z3 A4 g: G# \* J7 E* O

- }3 U- H. T9 K. T, \1.2 外部时钟源(HSE旁路) 4 M* p$ I; F Y

在此模式下,必须提供外部时钟源,频率高达50MHz。必须使用占空比约为40%至60%的外部时钟信号(方波、正弦波或三角波)来驱动 OSC_IN引脚,具体取决于频率(参考数据手册),同时OSC_OUT引脚可用作GPIO使用。: g, h. b' c. u! l& C0 g2 o

2 HSI16时钟

1 H, ^* k( @6 M+ RHSI16时钟信号是从16MHz内部RC振荡器生成的。RC振荡器以低成本提供时钟源(无需使用外部元件)。它还比HSE晶振具有更快的启动时间。但即使校准后,频率也不如外部晶振或陶瓷谐振器的频率精度高。HSI16时钟还可作为备份时钟源(辅助时钟)使用,以防HSE晶振发生故障。

: Z0 F% H# d! |- v* d% d3 MSI(MSIS 和 MSIK)时钟 MSI由四个内部RC振荡器组成:MSIRC0 (48MHz)、MSIRC1 (4MHz)、MSIRC2 (3.072MHz)和 MSIRC3 (400kHz)。每个振荡器提供一个预分频器,从而提供1、2、3或4分频。由这些分频振荡器生成两个输出时钟: : @) @: B" j2 a2 D

? MSIS,可选择作为系统时钟

3 ?% f* P# C2 [1 H? MSIK,可由一些外设选择作为内核时钟 ) u$ _) A0 I9 Q d7 k

$ ]. I& a. C2 Q! n( B; j& K+ e可由软件分别使用RCC_ICSCR1寄存器中的MSISRANGE[3:0]和 MSIKRANGE[3:0]字段(且MSIRGSEL=1)来调整MSIS和MSIK频率范围。提供十六个频率范围,由四个内部RC生成。* k9 A; ^7 b3 T+ l' \% y

如果HSE晶振发生故障,则MSI时钟还可作为备份时钟源(辅助时钟)。MSI振荡器可提供一个低成本(无外部元件)低功耗的时钟源。此外,当和LSE 一起用于PLL模式时,MSI可提供一个非常精确的时钟源,该时钟源可用于USB OTG-FS外设,并且PLL反馈,使系统以最大速率160 MHz运行。利用LSE进行硬件自动校准(PLL模式)9 [* @1 D/ y5 z; P

当应用中存在32.768 kHz 外部振荡器时,MSIS或MSIK可配置为PLL模式。此模式已启用,如下所示:

9 z" N# e* U1 c. L? 对于MSIS:在RCC_CR寄存器中将MSIPLLEN位置为1 # D$ z: `0 D' [0 b, D% _* l

? 对于MSIK:在RCC_CR寄存器中将MSIPLLEN位置为0 - k" x9 S8 ?: L& S0 e$ ?7 h

( p: A* M3 a5 i, P, o6 r; D如果MSIS和MSIK范围是从同一MSIRC源生成的,则PLL模式应用于 MSIS和MSIK。当配置为PLL模式时,MSIS或MSIK可利用LSE自动校准。该模式可用于所有MSI频率范围。48MHz时,处于PLL模式的MSIK可用; _ ?1 K% |0 G; u+ o( _) [

于USB OTG FS器件,不需要外部高速晶振。

2 q6 k \. F! ?5 w

% g9 g. E9 m. H( o2 d$ z8 o4 LSE 时钟

' \- ]% ?" M, p7 c% Z/ H. KLSE晶振是32.768kHz低速外部晶振或陶瓷谐振器。它为RTC(实时时钟)外设提供低功耗且精度高的时钟源,用于时钟/日历或其他定时功能。使用RCC_BDCR寄存器中的LSEDRV[1:0]位,可在运行时更改晶振驱动强度,以实现稳定性、短启动时间和低功耗之间的最佳平衡。外部时钟源(LSE 旁路)在此模式下,必须提供频率高达1MHz的外部时钟源。必须使用占空比约为50%的外部时钟信号(方波、正弦波或三角波)来驱动 OSC32_IN引脚,同时OSC32_OUT引脚可以作为GPIO使用。- l' T1 j$ V" g; F8 G8 {

==========' L: ]8 _$ @' P0 \- ~' ]" e) ^% b

往期回顾:Keil中变量不被初始化方法

3 [; q4 o( e" G' \' R如何提高单片机的运算效率之FPU

- X: x- G# A6 ]& O% R- C0 G蓝桥杯物联网教程汇总_240529

2 K" p: M ~* Z" J==========

9 @8 {5 j( h' T3 @1 N! E- U9 l- t

iwkmtvoh1r264022958332.png

: `1 s8 U. b, P8 Y. k5 T2 x. f* `

: `1 s8 U. b, P8 Y. k5 T2 x. f* `

' |1 ]* F6 I8 l

fnhakhenun564022958432.png

' L6 K! O2 N+ N/ n! P" I

' L6 K! O2 N+ N/ n! P" I

9 B& M U0 D) L C, }5 F0 ?; X

jp2y2cgmvdb64022958532.png

|