|

|

引言

0 ]6 a x+ A7 g* }在集成电路(IC)设计领域不断发展的背景下,Chiplet作为应对摩尔定律挑战的解决方案逐渐兴起。Chiplet是小型的、专用的集成电路,可以组合成更大、更复杂的系统。这种方法有许多优点,包括降低成本、提高可重用性以及集成异构组件的能力。然而,设计高效的Chiplet架构也带来了独特的挑战,特别是在性能优化和可靠性方面。

0 d! `* L0 m/ Q1 k7 `$ o4 Y* z# r m h/ t O9 f

为了应对这些挑战,研究人员开发了Floorplet框架,用于共同优化Chiplet架构的平面布局和性能。本文将探讨Floorplet的关键组成部分,并展示如何利用它创建更高效、更可靠的Chiplet设计[1]。8 \6 g. P# y8 D

xkoahsuxinn6402424924.png

1 t2 {- S) X% U3 e* |

- L# ~8 H1 b/ h: h7 y" T理解Chiplet及其挑战

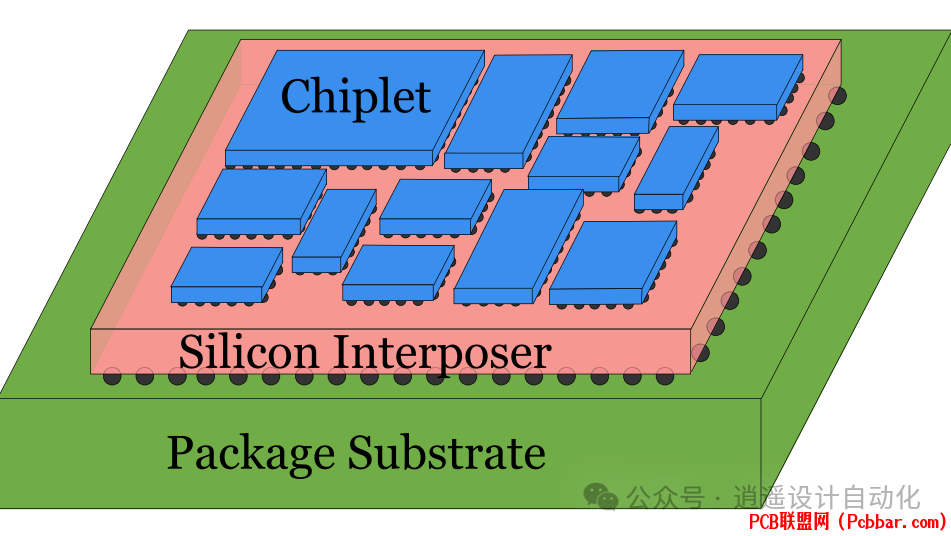

0 {8 H4 ]! j `) H2 g ^在深入了解Floorplet的细节之前,了解Chiplet的概念以及为什么在IC设计行业越来越受欢迎非常重要。Chiplet是一种集成电路,包含了整个系统功能的一个明确定义的子集。与传统的单片系统级芯片(SoC)不同,基于Chiplet的架构允许更灵活和更具成本效益的设计。

) w& N5 f( V' l$ o: F5 V

wgdlkfb0lzx6402425024.png

5 t- K" h9 w* k6 A% P5 G' C- ~

5 t- K" h9 w* k6 A% P5 G' C- ~

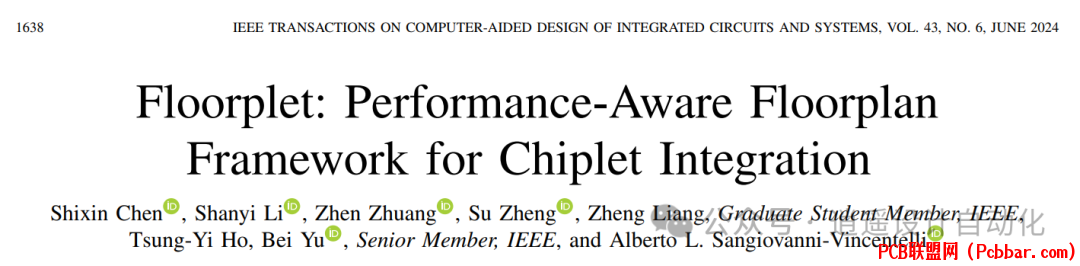

图1:基于Chiplet的2.5D封装架构。这张图展示了使用多Chiplet架构的2.5D封装的组成部分。+ L. o& {6 e- D8 X6 a8 o

- |0 a* g1 U. }7 a0 Y1 Z7 s然而,基于Chiplet的设计也带来了新的挑战:性能下降:Chiplet之间在中介层上的额外物理线长可能导致延迟增加和整体系统性能降低。可靠性问题:Chiplet集成中使用的先进封装技术可能引入可靠性问题,如翘曲和凸点应力,这些问题可能影响功能并缩短系统的使用寿命。设计复杂性:在基于Chiplet的设计中平衡性能、成本、面积和可靠性需要复杂的工具和方法。

4 W' k3 n2 E( w" \[/ol]

* W+ M4 s* ?* l7 b8 \5 f$ z! \+ B- s# SFloorplet框架# N& V( ^: X2 v

Floorplet通过提供一套全面的工具来解决这些挑战,用于设计和优化基于Chiplet的架构。该框架由三个主要组成部分组成:

9 H$ W6 \! _/ |0 j: oparChiplet:将现实的SoC划分为功能性Chiplet的算法。simChiplet:用于评估不同平面布局方案对性能影响的模拟平台。optChiplet:考虑多个目标的平面布局优化框架,包括可靠性、成本、面积和性能。

/ I7 j) B: r$ @) x$ R

4 `4 G; w" h, {( o8 d$ r让我们详细探讨每个组成部分。( t) Y6 Z( X; t* v3 R, d) f |: V

, i; M: s7 W* s$ P, I( x1. parChiplet:Chiplet生成6 P1 V+ k) K+ V9 ~; z2 B

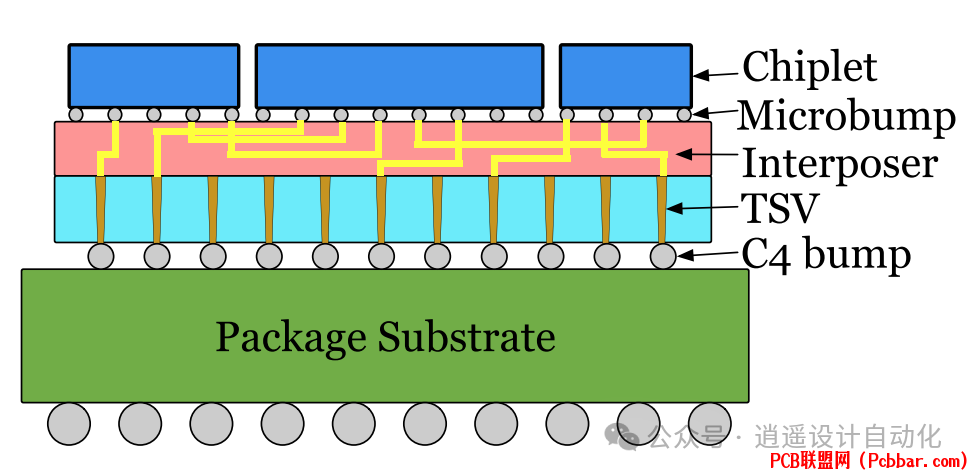

设计基于Chiplet的系统的第一步是将单片SoC划分为更小的、功能性的Chiplet。parChiplet通过分析SoC的层次结构并将其划分为可以独立制造和分析的组件来完成这项任务。5 b& b. v# S7 d, [1 |( y

1hlqbn4nl526402425124.png

+ J s: r& V2 c) L& o图2:SoC组件的层次树。这个图表展示了如何将SoC划分为功能块以生成Chiplet。

" Q4 B' _) i2 L0 H( D' c

: C0 `. s; v. _9 `. L; qparChiplet算法在划分SoC时考虑了几个因素:

0 ~# \+ ~; o" g( [( q, w(1) 功能完整性:确保紧密通信的电路宏单元保持在一起。

( \2 t7 F1 l' T6 W9 m0 N9 A/ X(2) 面积约束:控制划分的粒度,以平衡制造可行性和成本收益。& o7 Y' I) j% h% M( ~

(3) 可重用性:创建可作为可重用IP组件用于多个系统的Chiplet。' m$ ?& |: b1 i- s

& w4 G4 k/ J1 H/ G( fparChiplet的输出是一组具有明确定义的功能和面积规格的Chiplet,这些Chiplet构成了基于Chiplet架构的基本构建块。

: d1 J% d$ r7 x

- \4 M; f% X0 ]& n- h$ l2. simChiplet:性能评估$ S6 d: ]' l, d

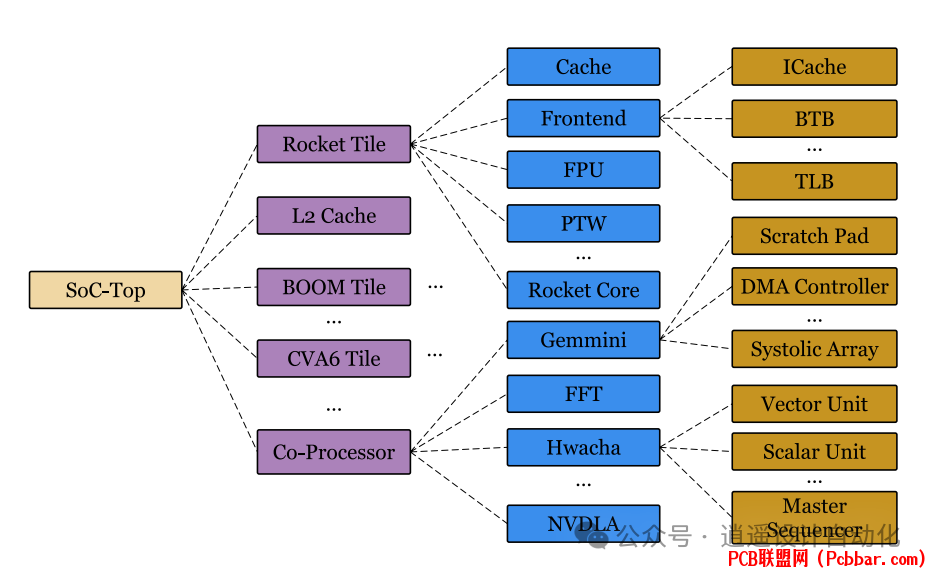

一旦生成了Chiplet,评估不同平面布局设计对整体系统性能的影响就变得非常重要。simChiplet是基于Gem5模拟器构建的模拟平台,用于模拟基于Chiplet架构的应用工作负载、通信模式和内存层次结构。" E2 G! ^( P2 B- d" M

5olsls50lpu6402425224.png

# i& y" N5 p8 I' o1 o图3:嵌入到Gem5平台的模拟流程。这个图表展示了simChiplet组件如何与Gem5模拟器集成以评估Chiplet性能。

- N" d: G* I6 J4 L6 v0 g+ l/ u" T5 {9 e; k6 C0 G

simChiplet的主要特点包括:

4 C: [: g# B* L7 g" z. L3 h- S2 r(1) 数据移动频率分析:该平台报告Chiplet对之间的数据交换频率,这对优化Chiplet放置非常重要。

( j6 C& J5 o8 G2 E3 ~(2) 延迟建模:simChiplet结合了延迟-线长模型,根据Chiplet在中介层上的物理分离来估计Chiplet之间的通信延迟。

$ j: W! R% I- W6 J3 x# B) Y# v$ w(3) 工作负载模拟:该平台可以运行各种基准测试,以评估不同Chiplet配置在实际工作负载下的性能。

: |1 l: z; |5 L! I. ? l& T0 c X

. Y/ n0 F/ F8 U& A* QsimChiplet生成的性能数据为平面布局优化过程提供了宝贵的输入,使设计人员能够就Chiplet放置和互连做出明智的决策。

5 m8 Q8 ]3 T% r( U& `* d0 {6 Z& V# N: g: N; D3 C! d! f

3. optChiplet:平面布局优化

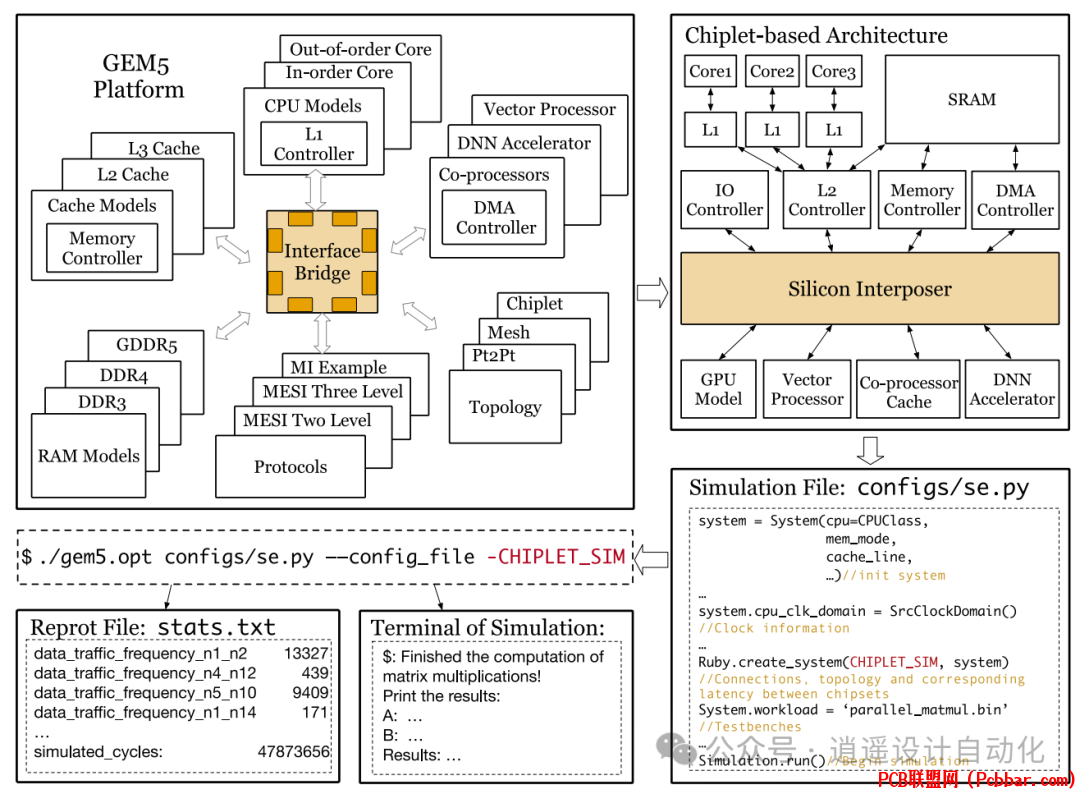

9 ]0 W: \( \0 K1 rFloorplet框架的核心是optChiplet,这是一个复杂的平面布局优化工具,考虑多个目标以产生最佳的Chiplet布局。optChiplet使用数学规划技术来平衡各种设计目标和约束。7 D! }" z" D9 R7 [9 s7 V4 _4 W# q

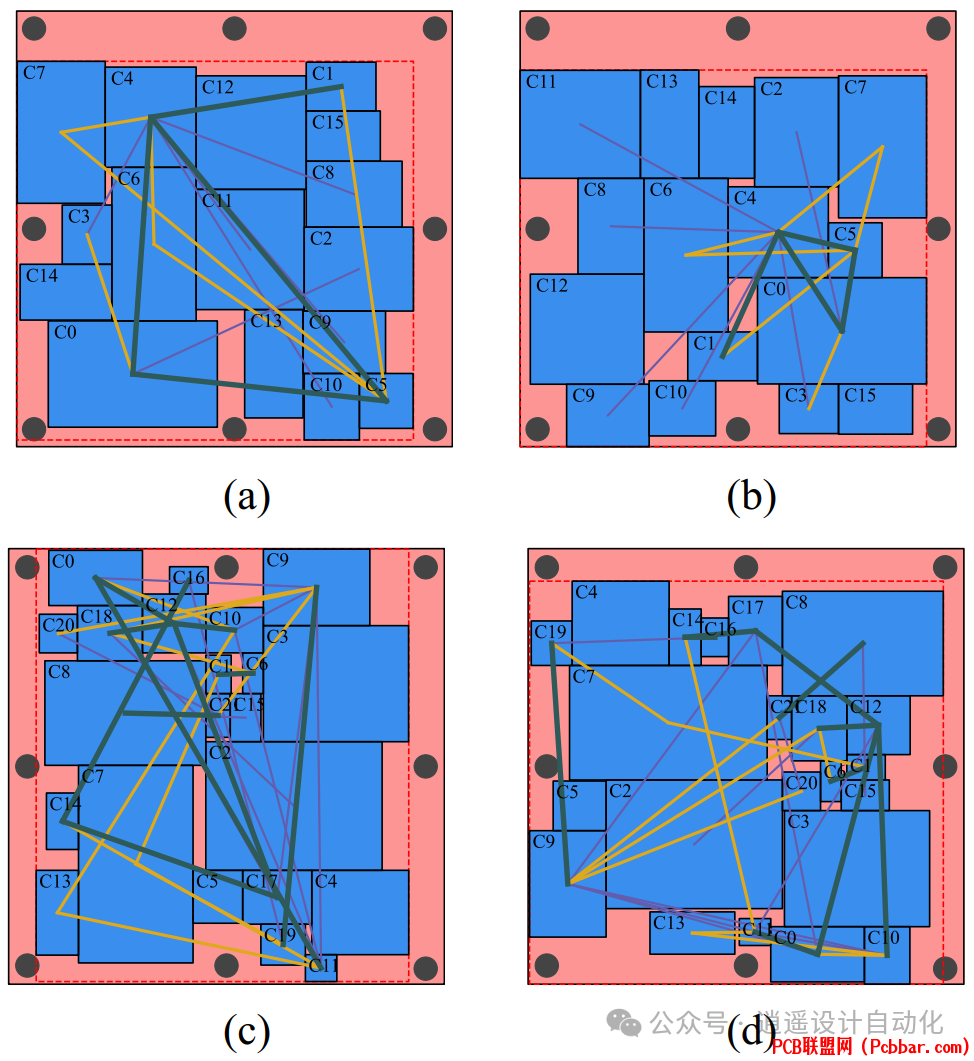

pbpp4oxq1xf6402425324.png

2 ?* _% G2 [) z @$ X# {图4:2.5D封装中的Chiplet平面布局设计。这张图展示了Chiplet在硅中介层上放置的例子,说明了平面布局优化问题的复杂性。7 j) u- F* I7 W1 M$ h

) W e+ l/ f; [3 uoptChiplet中的优化过程分为两个阶段:; t4 o( x9 Y+ u1 g( _, E6 t

(1) 主要平面布局:这个阶段关注基本放置,考虑以下因素:

9 ]$ y) m! @8 IChiplet尺寸和方向线长最小化面积优化翘曲约束避免凸点应力! r. W+ h* @1 E# `; [

4 x1 f( F5 f5 q4 S) u4 V& D(2) 性能感知平面布局:这个阶段结合simChiplet的性能数据进一步优化放置,考虑以下因素:

, s$ T& x, P6 [* KChiplet之间的数据移动频率通信延迟优化性能与其他目标(如面积、成本)之间的权衡6 n4 E v+ M3 a

' y2 p0 R1 s/ e) A7 A/ ]' a: u* Q

xra353hpql26402425424.png

. H1 P( K" W* _5 d; H

. H1 P( K" W* _5 d; H

图5:基于Chiplet架构的平面布局设计(C=16和C=22)。这些图像比较了主要平面布局解决方案和性能感知平面布局解决方案,展示了Floorplet框架实现的改进。

* ]5 j+ g- @5 M7 X2 I. R* M( }- X# F' S9 T* A

optChiplet使用复杂的数学模型来表示各种设计约束和目标。例如,包含以下模型:

% }* \/ D( P* q! u( C3 b k翘曲计算:估计由于热应力导致的封装弯曲。凸点应力:确保热点凸点周围有足够的间距以降低失效风险。成本估算:基于良率和焊接过程等因素计算2.5D封装的总成本。

8 l- p& n- ?5 k5 V/ V" W- u+ H$ I+ P h! D" T2 d/ _

通过同时考虑所有这些因素,optChiplet可以产生有效平衡性能、可靠性和成本的平面布局解决方案。

9 l' J' L% K" s: r$ B4 ?9 v% ~7 ~8 J5 E' \& v

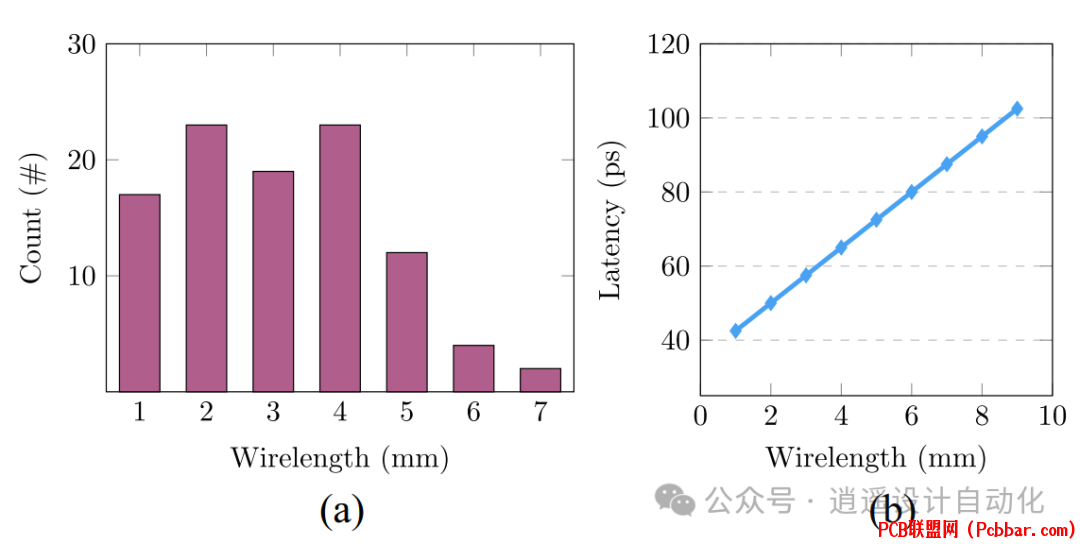

实验结果和效益

1 k! \% u9 n6 P. lFloorplet框架已在各种基于Chiplet的架构上进行了测试,相比传统平面布局方法显示出显著的改进。一些主要结果包括:通信成本减少:Floorplet平均减少了24.81%的Chiplet间通信成本。性能提升:该框架将完成工作负载的平均时钟周期减少了13.18%。最小面积开销:性能感知平面布局仅增加了0.86%的总封装面积,这是为显著性能提升所做的小幅权衡。可靠性增强:通过考虑翘曲和凸点应力问题,Floorplet提高了基于Chiplet设计的整体可靠性。+ \8 |. c# `5 T; {, w

[/ol]4 F" e: P3 j9 v! x. G# z4 j+ R! C

qc25akzl2xr6402425524.png

4 R+ X$ v7 Z9 W4 b3 m+ T/ @图6:延迟-线长模型。这些图表显示了(a)Chiplet之间线长的分布和(b)延迟权重与线长之间的关系,这对Floorplet中的性能优化非常重要。, V8 t. H' A5 b8 a, X, j3 J* I

9 Y3 x7 C$ V: R+ A6 h) B7 Q+ i结论+ l' g5 U. ^ G, x G6 H' N$ O

随着半导体行业继续推动摩尔定律的边界,基于Chiplet的架构提供了有前途的发展方向。Floorplet框架为设计和优化这些复杂系统提供了全面的解决方案,解决了性能、可靠性和成本方面的关键挑战。, u* u4 ]4 `4 Q3 C: @3 x- \) w7 ]

( a: {" m$ C" ?- A

通过整合Chiplet划分、性能模拟和多目标平面布局优化,Floorplet使设计人员能够创建更高效、更可靠的基于Chiplet的架构。随着这项技术继续发展,像Floorplet这样的框架将在塑造集成电路设计的未来方面发挥关键作用,促进更强大、更具成本效益的电子系统的开发。

N; V% A7 z: U" {: c, S

' z5 b3 ^" r, |参考文献

# v% W. V4 V% a% E3 ^[1] S. Chen et al., "Floorplet: Performance-Aware Floorplan Framework for Chiplet Integration," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 43, no. 6, pp. 1638-1649, June 2024.2 ~ B& [ O- F0 c; Y

, w% ~( Z6 J8 H$ l7 G

- END -( ]- a% I9 C5 }' e) |

. T: V7 w, m) G c, \# D2 G

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

; }" N& L `8 y. i) q5 L$ ]" L点击左下角"阅读原文"马上申请) i% u% W! Q4 h- F; t/ d: V

8 r: A; x2 F. O9 S3 m3 m7 {5 W

欢迎转载2 i* h3 i9 a" a) b. y9 a) G

1 u( b0 ?, }; y, c

转载请注明出处,请勿修改内容和删除作者信息!6 a: |! u* P( j) |/ l; E& n

8 u2 j; y: w0 K) ?8 X4 {2 E$ F4 n# _

% S2 P9 t& W4 y1 v4 `5 ~. b& O4 z, h% Q; x- j

2v4y4wk5rlt6402425624.gif

3 p/ s+ j# Z8 I" H2 h/ D9 r n

1 _0 F3 m1 ]# @$ M) p' V2 B关注我们7 B5 x, V" \8 }8 q& b3 M

( a+ w. ]( C# j

5 N9 @+ Z( E8 Q" ~) z

bmo2xfqd5nl6402425724.png

& j3 y9 T3 P$ H# q0 r! h

& j3 y9 T3 P$ H# q0 r! h

| - p/ g) U* b' Y4 W' D; h0 A/ L

tvksjvhluo36402425824.png

- o& n) g& _# t' h# E

- o& n) g& _# t' h# E

| ( ?$ z9 \5 u5 U" ]

3zpjr5a4xcw6402425924.png

: u/ v% I* \; z |

! k9 q. Z& F/ e6 {, M7 B

9 q' `' U" D* |& \1 ?, b# Y7 S+ h1 R8 ^1 D4 R

7 E: _+ Y+ C$ c; |0 O

关于我们:0 _6 ? e7 h( j$ I3 w

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。& `( } ]+ g0 h3 n# T- ]

, F$ y0 I/ C, v0 c/ a; G

http://www.latitudeda.com/

! C3 P/ w8 F2 r4 D& g7 ?$ G8 J(点击上方名片关注我们,发现更多精彩内容) |

|