|

|

引言

( k# |; F. G! B绝缘体上铌酸锂(LNOI)波导因其优异的光学性能,在集成光电子技术中有广泛应用。然而,由于铌酸锂(LN)的硬度高、化学惰性强,且在刻蚀过程中易产生材料再沉积,制作低损耗LNOI波导具有很大挑战。本文基于美国国家标准与技术研究院(NIST) NanoFab设施的研究,介绍了优化LNOI波导制作工艺的关键步骤和注意事项[1]。) ~1 K% c4 x. m6 @% k# w3 K; ~

& r/ d% @; u. p1 q0 z3 k

e3h5t41zxn364024936228.png

0 v @# w4 z% I. I* `

0 v @# w4 z% I. I* `

- F- _* K( {( t7 a8 i% x' t% ]% h

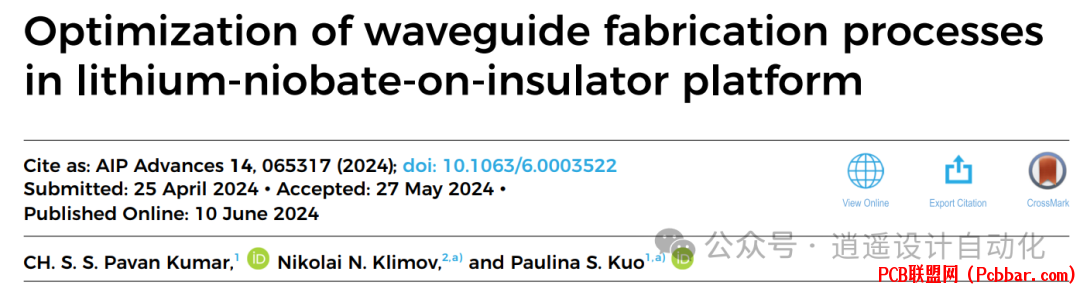

' g3 s# X7 P. }+ i6 }掩模选择与图形化

% t& D: f) e8 v选择合适的掩模材料对获得高质量刻蚀结构非常重要。虽然软掩模(如电子束光刻胶)使用简单,但通常会导致侧壁质量较差。硬掩模,如铬(Cr)或二氧化硅(SiO2),一般能产生更好的结果。

0 q0 `& a7 g3 S$ I4 h3 m4 p7 f8 t

为图形化波导,通常使用电子束光刻(EBL)和正性光刻胶如ZEP520A。将光刻胶旋涂到LNOI芯片上,用EBL曝光,然后显影。对于硬掩模样品,在涂覆光刻胶之前需要先沉积掩模材料(如Cr或SiO2)。( ^$ U* ~! \* x; y

x54xmuvxgiz64024936328.png

! J4 M) V8 [' B& X1 H1 B7 Q, B图1:使用ICP RIE图形化LN的制作过程示意图。

6 b0 C& T) o! ]5 p

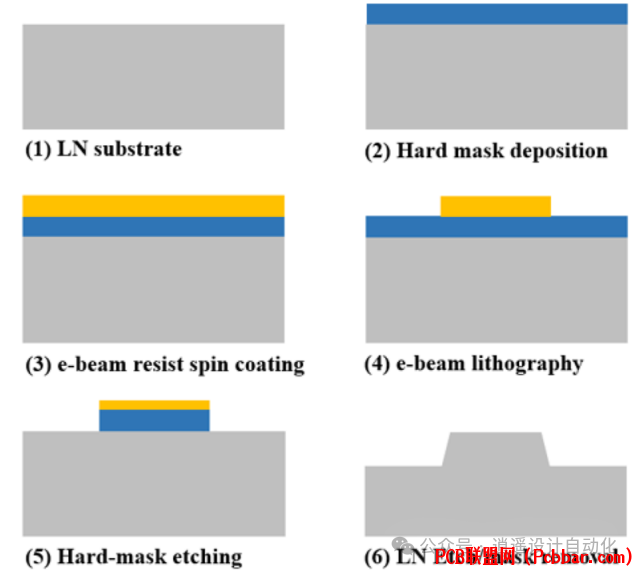

% F! T Q; G% e0 {+ G) U& u1 q刻蚀过程 q: v, h4 U9 F9 O

电感耦合等离子体反应离子刻蚀(ICP RIE)是刻蚀LN的首选方法。

" F, {& g+ `2 h, N( Y$ c' ~" F' K该过程使用氩(Ar)等离子体物理刻蚀材料。需要优化的关键参数包括:$ | F" L: N. c; j- d0 n

射频(RF)功率:控制离子向基板加速,显着影响刻蚀速率、深度和再沉积。ICP功率:决定等离子体密度。 W/ q$ C8 [5 k1 [' F! H" k

腔室压力' \, h8 j5 f: W0 U; W' e: ~

气体流量. Z6 P+ v, R& v S: W; E- m7 I

基板温度

; {6 ^5 E$ m+ h% g8 o0 O. J% B8 k; k! d, I, L; v

5 M: Z& s* `) V J9 m( E

ejootsvwz0r64024936428.png

, n/ S, v) I) \( e5 N, ^7 S A

, n/ S, v) I) \( e5 N, ^7 S A

图2:用于LN刻蚀的ICP腔室示意图。

( a+ X, r/ u4 E( G( j( Y

% F/ L( u- v1 C( F- H5 V6 v0 @

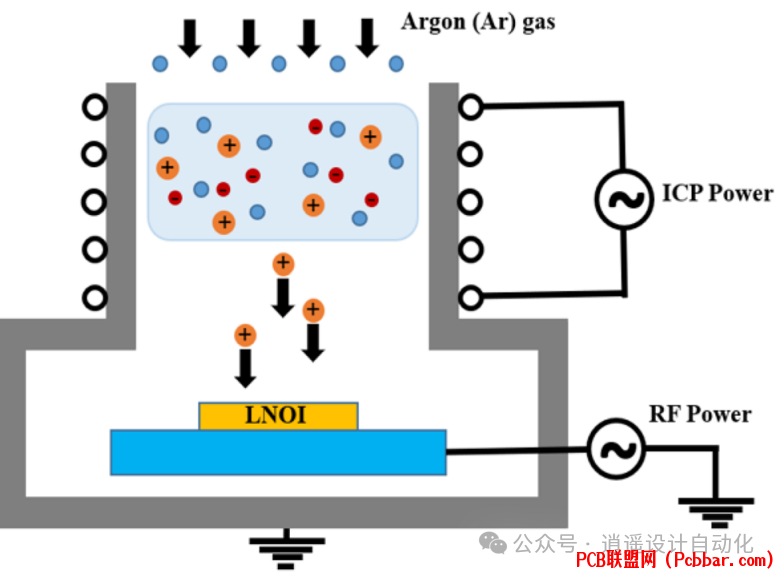

. h- V, G5 }0 j5 m9 l4 X0 NRF功率优化2 s7 C. u$ O: K( S0 q' J) V

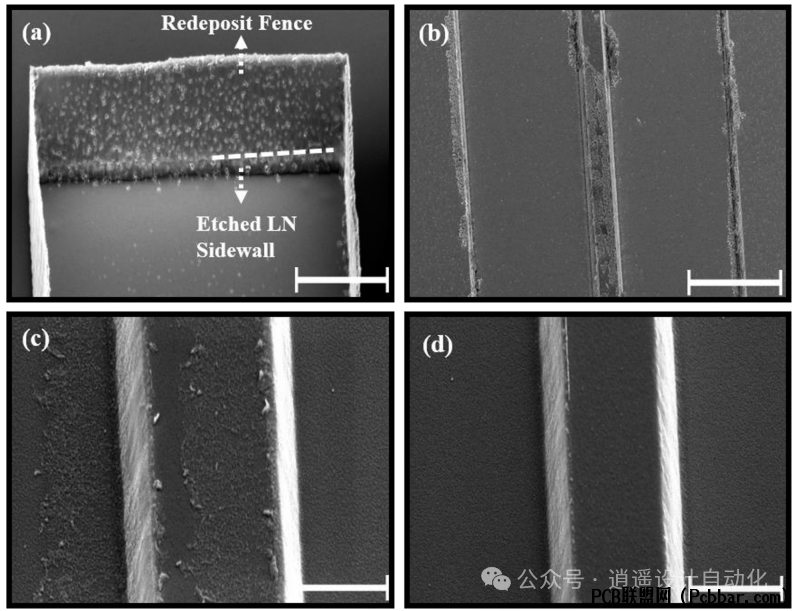

RF功率是影响刻蚀和再沉积平衡的关键参数。在低RF功率下,再沉积材料往往积累在侧壁上。随着RF功率增加,刻蚀速率超过再沉积速率,导致侧壁更干净。: {% X( J# y. K- H+ X5 ], g

vlehck5wtqz64024936528.png

9 k9 B o) [# G1 |0 P, A7 O

9 k9 B o) [# G1 |0 P, A7 O

图3:SEM图像显示了RF功率对使用Cr掩模样品再沉积的影响。

- |" g7 a% a* V$ ]* ~2 o

, o& N' P J' t然而,过高的RF功率会导致波导结构损坏。最佳RF功率范围通常在100-200 W之间,但可能因具体使用的ICP RIE设备而异。

( d$ a) Y7 c3 R. Z, Q0 m% w; p, [" F S* _3 t

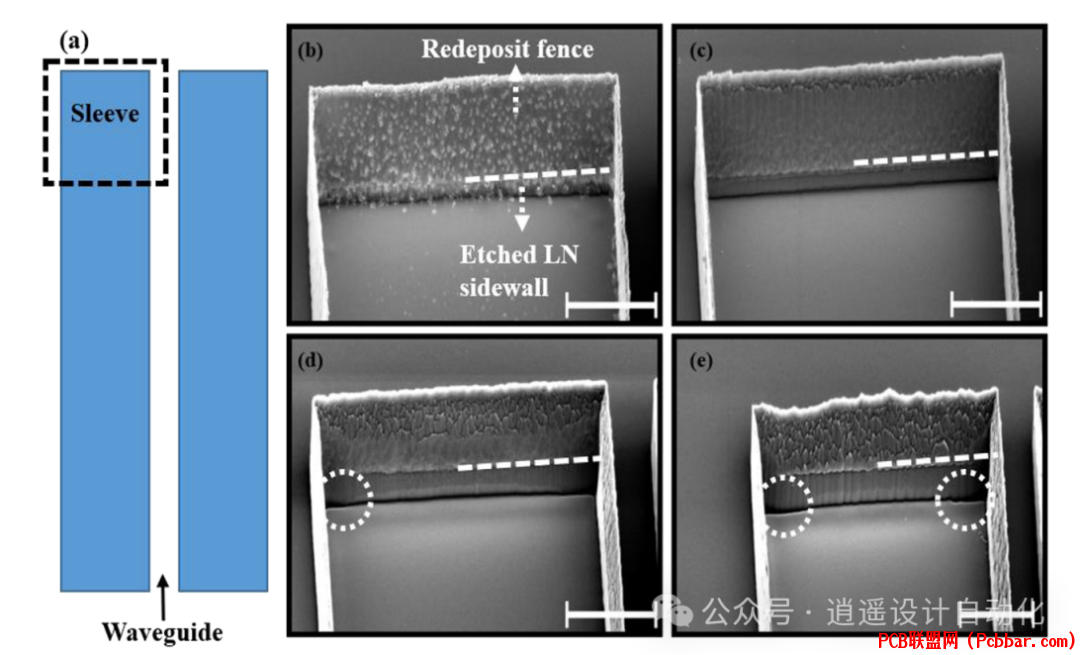

再沉积物去除

* U( w7 Q2 I4 n: V即使优化了刻蚀参数,通常仍有一些再沉积物残留,需要通过湿法清洗过程去除。改良的RCA-1溶液(NH4OH:H2O2:H2O比例为2:2:1)加热到85°C对此很有效。6 r4 {. L7 {1 [' n; }9 H# E

qgsrx35kcbr64024936629.png

6 A: Q; A& I; ^; ]5 k& G

6 A: Q; A& I; ^; ]5 k& G

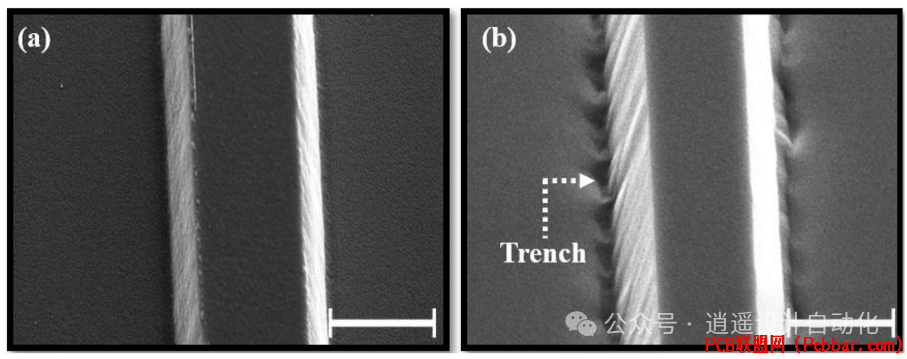

图4:清洗过程不同阶段的LN波导SEM图像。

( @# {6 B4 Z' h) P* A

$ Q1 x n' L Y; t- ~. J, v, L) t清洗过程需要仔细优化:持续时间:清洗不足会留下再沉积物,过度清洗会损坏波导。方向:样品应在相对于搅拌方向的0°和90°方向上清洗。溶液新鲜度:改变样品方向时,应准备新的清洗溶液。

& g {! T3 H9 i( O[/ol]

$ K7 m5 o$ P# `( P( W, R典型的优化清洗过程包括每个方向15分钟,总共30分钟。

" \/ |3 u. \) R3 G+ a" e

fyvfj3jmxz364024936729.png

4 b# x3 D/ d# ^7 T: i

4 b# x3 D/ d# ^7 T: i

图5:SEM图像显示了过度清洗导致的波导损坏。

; H( |* k, g( d, ^4 H

" e1 P1 a& f; d6 T; e8 T2 W7 Q硬掩模比较: d2 U- v) E( a0 ~- t

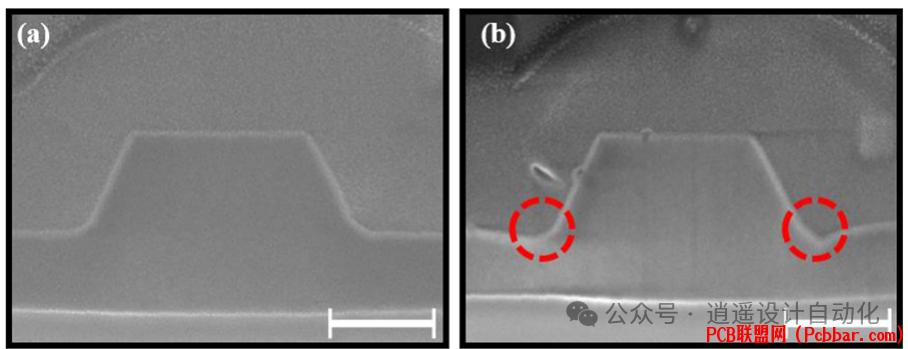

虽然Cr和SiO2硬掩模都能产生良好结果,但它们具有不同特性:

' C4 f! _! J; @ ~ K' V5 i+ z5 `3 t& f* d1 z. F9 j

1. 铬掩模:% v+ [0 Y6 ^+ G8 S; K7 [3 Q$ c

由于Cr的多晶结构,在侧壁上产生颗粒状特征与SiO2相比,通常产生更光滑的侧壁不太容易出现沟槽问题

" T- y1 Z7 ]% x( h, d8 i. W2 B& I" B$ j7 s {& R. @

2. 二氧化硅掩模:; E# L- u0 _0 r- P" H, |& H; b

可能在侧壁上产生条纹更容易在侧壁底部产生沟槽可能需要额外措施来缓解充电效应

- b6 O4 r3 @4 K2 k/ |! B) @- O% Y; Q7 E% g J" f- z9 a

; b1 R1 D- y+ i5 ^: ]. p! G

n4izrx34oyw64024936829.png

0 l, w4 c+ X: A+ G

0 l, w4 c+ X: A+ G

图6:比较使用(a) Cr和(b) SiO2硬掩模刻蚀的LN波导SEM图像。) w9 H, ]6 y2 {$ d& C! C* J* a+ a

, Z; B! q7 P+ k$ r* g" A

mod4olhxdjh64024936929.png

* L9 B; X! J& `! a5 Y( [: f图7:使用(a) Cr和(b) SiO2硬掩模刻蚀的LN波导FIB-milled横截面SEM图像。

! J3 w. }2 X$ V' ^; ^: A6 P! a

8 C$ w" k0 l2 h- D波导制作流程6 f) ^+ G/ y, ^

基于上述优化,以下是制作低损耗LNOI波导的流程总结:

, Q# c8 F$ M' V2 u2 B: y4 S* H1 D* _6 ? @' f, ]

1. 基板准备:

7 Y/ |- [* D5 h: U从LNOI晶圆开始(如700 nm x切割LN薄膜在2 μm SiO2上,再在Si基板上)

/ c3 X* f- U" d L7 ^& z& E使用硫酸高锰酸钾溶液清洗基板,然后进行RCA清洗

& p% w# g8 D& v) v' i+ I$ \

" T' i0 t% Q5 K( C g2. 硬掩模沉积:) Y1 L3 D. ~ R

使用电子束蒸发沉积50 nm Cr(替代方案:500 nm PECVD SiO2 + 10 nm电子束Cr)

+ }/ Z- G+ {) [; ^$ k9 E

7 q* a- q7 U. ?; N1 D3. 光刻:0 ~1 ~! m% o6 m- Q4 k3 p

旋涂ZEP520A电子束光刻胶进行电子束光刻定义波导图形显影曝光后的光刻胶

: |) F' J, V. C) E3 p1 L& a, v. u" q3 U( v5 W+ h3 {

4. 图形转移到硬掩模:0 X+ I0 a& o( s) N9 D6 f% V! J

使用ICP RIE刻蚀硬掩模层

+ o9 {: g' S' X) j7 L, [

9 w G) z N: V" b' X- J5. LN刻蚀:

. k j1 f( h' `$ I K- Y2 U" d使用优化参数进行LN的ICP RIE刻蚀:! [3 U$ z: ?' J4 N! P

RF功率:150 W

" I& {; O' z, r" L5 `3 v1 J% `% q ICP功率:1500 W

1 v: m" f( T# f' A$ { 压力:5 mTorr2 l: J1 y3 }3 o5 l. ]

Ar气体流量:20 SCCM, a6 I( `* t% z

温度:5°C6 {- G( ]& i: K1 v

使用多个短刻蚀循环,中间有冷却期,以防止样品损坏

' q9 Z) u) E& P6 ^

9 Z6 ]$ r( w- k, i5 a6. 掩模去除:

/ W, z. B3 p# @7 Y: Q4 V' j6 Z( V/ l使用适当的刻蚀剂去除剩余硬掩模

: m9 ?) k# U5 S! m

0 p4 Z" `/ ~# ?7 @% Q+ d8 u9 B. v' K9 ~7. 再沉积物清洗:

# m. ]4 h1 }/ r! |8 F- C0 o+ N在加热的RCA-1溶液中每个方向清洗15分钟(总共30分钟)4 W; |1 R& _! o; F

" b) R* f/ m, ?8. 包覆(可选):

' d; I, k$ K! G& w6 U9 n使用PECVD沉积2 μm SiO2作为上部包覆层

; f+ X2 `1 J, z% J- ]

$ {! m9 }" j3 T+ c$ S- C9. 端面准备:$ \5 K4 X- i# r9 S" F, K0 P, x8 G

抛光端面以进行光学耦合; {' \! B( X! R+ q8 T# _

) n( Y/ m1 l9 [- n( C# w光学表征

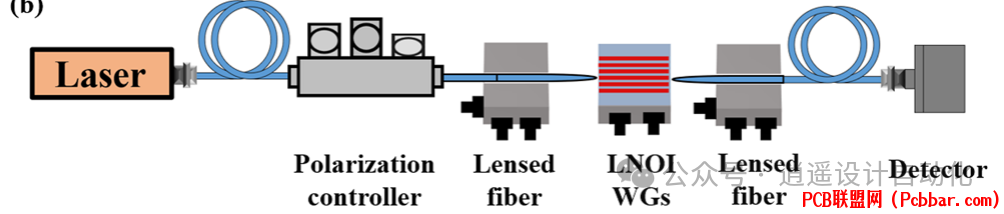

# @3 N4 J6 S) g5 [为评估制作的波导质量,光学损耗测量非常重要。典型设置包括使用锥形光纤将1550 nm激光耦合到波导中,并测量输出功率。

8 m: P) Q5 l3 L& `3 ]9 T/ M( @& N: f# V% V

wtvd2posuzu64024937029.png

" G% b! H' x$ e4 r

" G% b! H' x$ e4 r

图8:测量LNOI波导在1550 nm波长下光学损耗的实验装置示意图。1 j8 `2 X2 A6 a# |5 Y7 q3 d4 M) n

% i7 F( ]; i4 s: ^

ul1kuapvt2164024937129.png

' j6 v% V- _2 E3 B5 d

' j6 v% V- _2 E3 B5 d

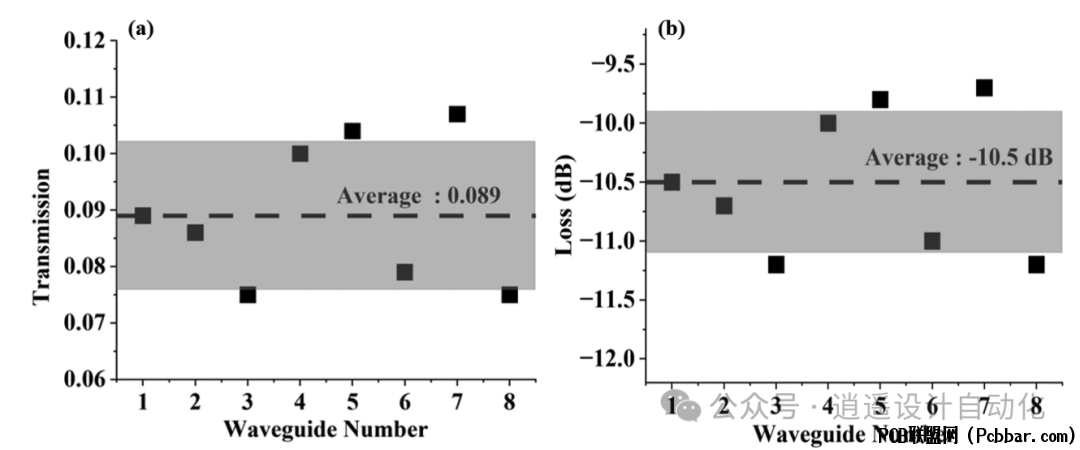

图9:对八个相同LNOI波导进行的光学损耗测量结果。) j: I ~6 B% s- z2 H% w2 q8 t

' `3 j* t* |1 m6 {使用本文描述的优化制作工艺,可以实现长度为4.5 mm的LNOI波导,总损耗(传播+耦合)约为-10.5 dB。这相当于传播损耗的上限估计约为2 dB/cm,与文献报道的数值具有竞争力。; G/ N4 c9 H! ?0 i( C$ {

0 |' X, E/ b$ i! l4 q; @结论

& X# T/ n0 E$ `" g* z0 C制作低损耗LNOI波导需要仔细优化多个工艺步骤,从掩模选择到刻蚀参数和刻蚀后清洗。作者认为通过遵循本文提供的指南,研究人员可以开发可靠的工艺来制作高质量LNOI光电子器件,即使在共享洁净室设施中也能实现。持续改进这些技术将进一步推动集成铌酸锂光电子技术的发展。

6 S8 U1 n/ T8 z: j6 y! I+ H0 ?6 [4 \ ]% p0 t& [1 T

参考文献

. o+ n/ o! Q& V% l* J[1] CH. S. S. Pavan Kumar, N. N. Klimov, and P. S. Kuo, "Optimization of waveguide fabrication processes in lithium-niobate-on-insulator platform," AIP Advances, vol. 14,

/ V7 W! ?( C9 F% a- w0 A1 M5 J" @6 D/ u l% z J

- END -$ D. A9 ^5 b5 @

- w5 S* ~4 q9 |& h软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。0 z9 r) g5 w- Q( ]# P* B

点击左下角"阅读原文"马上申请

. p& [4 r* W4 Y9 t2 V

% N' f. q( I2 J/ {! g' b欢迎转载

7 S2 N* q3 D9 h& `4 M3 v, p! G% n$ f& B o- |) {

转载请注明出处,请勿修改内容和删除作者信息!

. b2 s$ K; I. f! h2 x, @5 F2 r

8 v/ J+ A3 W0 z

+ k$ D2 ~$ {# `1 m8 q- ~& ?- N6 }* w v( J" w

hw1s5dht4m264024937229.gif

3 L! G" T* r: j( N* b& n. a) a, P- Q' e# h* _: n* H

关注我们5 W2 a% ?0 X8 O* g; H

. N" Z! I2 h1 g; r/ ^- _5 R# J4 @

, q* @- H, g G2 y

whn4bmjbqz164024937329.png

% J/ [ `8 ^) B# G$ S, A | " v$ O6 g' i8 a2 ?- k. d$ f# ]

tzptan0dw4364024937429.png

8 C& u% ?3 Q4 \ Z- M, v

8 C& u% ?3 Q4 \ Z- M, v

| 6 K3 T& O- P' h; t* k. F1 o

o1vn0vh3cek64024937529.png

6 e. V! x! @+ ]# n# W' J |

6 r {, d; {# L0 M( l2 {0 H: @+ D% m! P2 b3 d; s5 T( G# P

" \+ C6 {0 O1 |: m0 N8 H0 f: N9 ?) y8 @' U5 g$ Z+ f

关于我们:

- Y( K: W7 B5 o8 q6 i) A: S深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。: k* G5 ?+ x! z' f/ w3 n2 O X: b* O* o

- n, i' L2 `3 }: \7 H& ihttp://www.latitudeda.com/. l/ a, {+ k4 o/ Q

(点击上方名片关注我们,发现更多精彩内容) |

|