|

|

引言

; b8 h8 u3 \# w0 p2 _Chiplet是具有特定功能的模块化芯片,这些芯片单独制造,然后互连形成更大的系统。与传统的单片系统芯片(SoC)设计相比,提供了更好的多样性、可扩展性和性能优势。随着全球Chiplet市场预计每年增长超过42%,了解与这项创新技术相关的测试挑战和解决方案变得非常重要。

) Y' W! e3 n$ O6 a

3 C) y, f$ S. U7 q+ g本文将探讨Chiplet的世界,重点关注电气测试的重要性、测试协议的最新进展以及业界正在进行的测试方法标准化努力[1]。% \3 s( S. b" b. P' }; }

]" ? V7 u* i5 [ ?* q4 Y0 W* I+ v# {

o0lzffknfg464050446714.jpg

+ L+ h! N5 C- r! h. Y: }+ d0 F; G5 P$ |

9 F3 K9 l2 }+ m7 a/ ]Chiplet测试的重要性

! A$ y' V. `7 v% C$ d3 ^0 EChiplet的电气测试对确保异构架构的可靠性、功能性和互操作性至关重要。由于Chiplet经常来自不同的来源,在最终集成系统中保持一致的质量和性能成为重大挑战。

: N6 W# | }; C

9 n4 e3 h5 R4 U7 y* z q质量和可靠性标准

0 v+ P0 [4 O$ d/ r2 H+ GChiplet的质量指制造时的状态。与单片SoC一样,Chiplet必须满足特定的质量标准,这些标准因应用领域而异。这些标准涵盖性能和功能等方面。

: l2 n ?0 N+ K/ q8 a5 }1 b. y) p y& n4 s8 N$ N6 Q; O, B! |

尽管进行了严格的测试,一些缺陷可能仍未被检测到,并逃逸到最终的Chiplet中。这些"测试逃逸"以每百万缺陷部件(dppm)来衡量。对于手机等消费电子产品,典型的容忍度是100 dppm,这意味着每百万个Chiplet中,可以接受100个有缺陷的产品。! ^. S. t1 a3 Q1 a8 F3 ?% p

4 | |1 a9 D1 k0 E( y! C& s* p7 p

然而,某些行业要求更严格的标准。例如,汽车行业通常要求"0 dppm"(实际上转化为个位数dppm)。这种严格性是由于车辆电子设备的关键性质,即使是小故障也可能带来严重的安全隐患。

( \$ D& r( i! N6 t% h+ H( g+ i$ b) f

dbude0iqibh64050446814.png

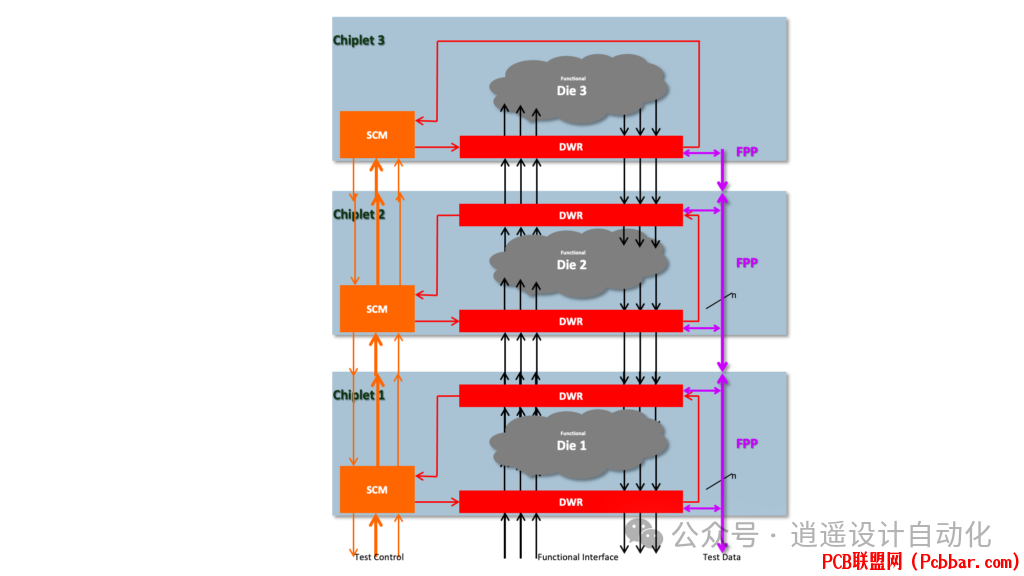

0 D% z8 L7 C" o4 y, n; I3 s3 R; {图1:展示了一个包含三个Chiplet的3D堆叠的横截面,显示了形成测试激励和响应"电梯"的设计即测试(DfT)元素。

9 Y. n; J# i7 A) x9 k! a1 e8 p) s: \7 {/ P; x Z

测试阶段+ ~& o$ s+ A ?, g: I9 _/ |. V9 t

基于Chiplet的集成线路通常比单片SoC经历更多的测试阶段:预绑定测试:检查单个Chiplet,确保符合规格且无缺陷。互连测试:验证Chiplet之间互连的完整性和可靠性。组装后测试:Chiplet组装完成后,对整个设计进行评估。7 z, Z' i( g; T5 u8 j! _

[/ol]

! K9 V2 c, J& |# F

; P+ q/ J9 _/ O( s+ w0 a标准化努力

% ?# ~: j6 ^) F测试基于Chiplet设计的一个主要挑战是确保测试激励能够到达每个Chiplet,并且能够有效读出响应。为解决这个问题,业界领导者已经开始了标准化努力,以确保来自不同来源的Chiplet之间的兼容性。& G9 |' s; Q8 u$ U# S

( {- p, x( M3 j3 g1 T4 v" F5 j8 y( X2 ^3 J2 }% m0 A

IEEE Std 1838? 3D设计即测试标准

' `( w4 z/ M U. W7 a6 b3 b作为纳米电子和数字技术领域领先的研究和创新中心,imec发起了IEEE Std 1838? 3D设计即测试(DfT)的标准化。该标准规定了允许测试激励和响应通过多个堆叠Chiplet传输的DfT结构。) d* ~9 z$ p5 X; d6 M5 [: b6 e

/ J" R& D p# l. M x/ d6 v! @例如,要测试四个堆叠中的第三个Chiplet,第一和第二个Chiplet必须具有标准化的DfT结构,以便于测试数据的传输。自2020年以来,所有主要的电子设计自动化(EDA)软件公司都遵循IEEE Std 1838?标准,确保了整个行业对Chiplet测试的一致性方法。+ m% ~, S* V! D5 h3 ~2 f

; F, H3 P( \6 z% F, `# z+ V+ N" {通用Chiplet互连快车(UCIe)

8 m6 |+ a, d, F: ^, z0 ~9 x' B另一项关键的标准化努力是通用Chiplet互连快车(UCIe)。该标准专注于裸片或Chiplet之间的互连,超越了竞争的界限。UCIe确保来自不同供应商的Chiplet能够有效通信,这对Chiplet技术的广泛采用很重要。

$ z) N- R% Y3 W$ t S% q" p

6 E8 E6 R$ Q: V" i4 ^互连测试的进展

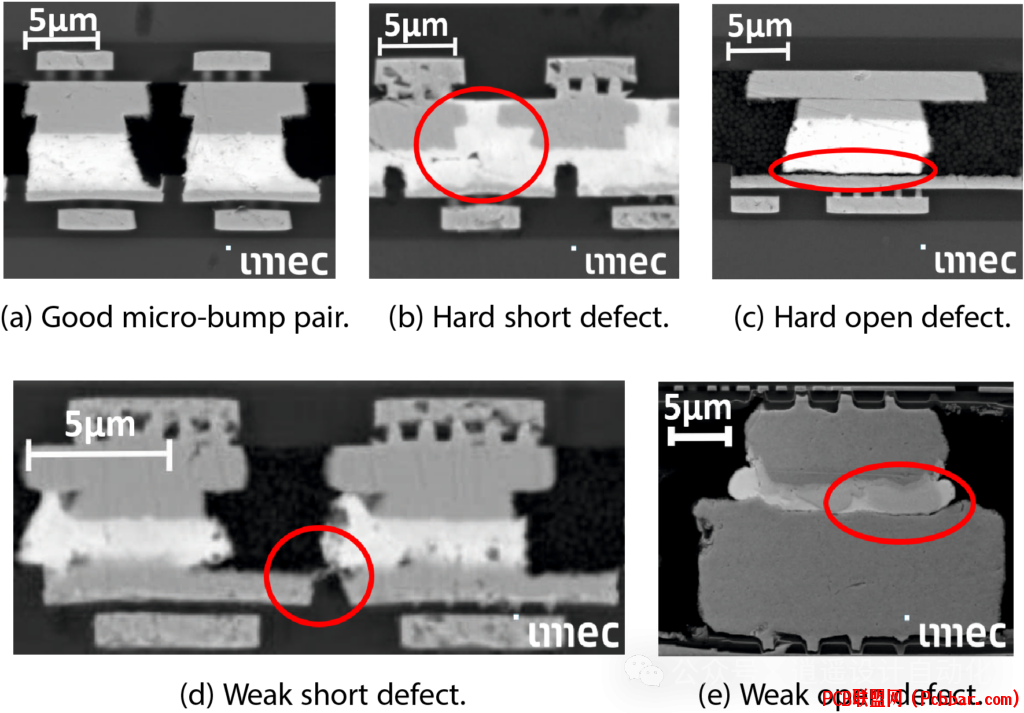

; k& J" M1 E! _4 q传统的互连测试方法主要针对硬开路和短路缺陷。然而,最近的进展导致了更全面的测试方法。

$ S6 R( y: q+ s" R4 a+ H+ q! h

3ptzkxf3fbj64050446914.png

$ z) L, Y/ \9 Y/ e0 o图2:显示了各种微凸点缺陷的扫描电镜照片,包括电阻性变体,这些现在可以通过imec的E2I-TEST方法检测到。

9 _, }& ^, P7 F# q2 X+ o

+ `: Y8 U5 L" v$ {8 V B( v3 D; rImec的E2I-TEST方法

- s2 b& D q/ B* VImec提出了一种改进的互连测试生成方法,称为E2I-TEST。这种方法相比传统方法有几个优势:提高效果:E2I-TEST覆盖了弱缺陷变体,包括高电阻短路和低电阻开路缺陷,这些缺陷通常被以前的方法忽视。提高效率:通过仅考虑相邻互连之间的短路,该方法减少了所需的测试模式数量。可扩展性:E2I-TEST将测试模式数量与互连数量解耦,使其更适合未来互连密度不断增加的Chiplet设计。- y& Y- K" ^( C3 s3 [, B7 d8 _& k

[/ol]

! n, _" [2 i+ {) O! J! O, I0 V; b& i% l- G/ F( K

挑战和未来方向

# I! y5 l: n) c7 L- Z0 p6 K7 B随着Chiplet技术的不断发展,出现了几个挑战和机遇:异构集成:随着来自不同供应商和工艺节点的Chiplet的组合,确保无缝集成和测试变得更加复杂。已知良好裸片(KGD)测试:开发高效的方法来测试集成前的单个Chiplet对降低总体成本和提高良率至关重要。热管理:随着3D堆叠的应用,在测试过程中管理热量散发变得更具挑战性,需要创新的解决方案。测试访问:随着Chiplet设计变得更加复杂,确保对所有组件的充分测试访问,同时不影响性能或增加成本,仍然是一个重大挑战。人工智能辅助测试:利用人工智能和机器学习技术优化测试模式并预测潜在故障模式是一个新兴的研究领域。

) Z: G/ _1 t+ o2 G0 U3 k+ q[/ol]& u6 y8 N: `% ?' ^! I( S) K7 q5 I( o

结论# |8 i. P8 p1 M) I% s$ l

Chiplet技术代表了半导体设计的重大进步,为性能、可扩展性和成本效益提供了新的可能性。然而,从单片SoC到基于Chiplet的设计的转变也带来了测试和质量保证方面的新挑战。" f, |5 X# s( j/ C$ b7 ~5 R c

4 s# W6 ]4 k& b7 B: Z' d5 z通过IEEE Std 1838?和UCIe等标准化努力,以及E2I-TEST等创新测试方法,业界正在解决这些挑战。随着Chiplet技术的成熟,可以期待测试方法的进一步发展,确保这种有前景的方法在各种应用中发挥全部潜力,从消费电子到汽车等领域。

4 u4 ~4 T* }7 a! S# a% O

$ i, o, O+ ~) e" [: Q. g

1 \ h' J2 E) K) y) v参考文献% O! l/ B0 n5 G/ t X+ a7 o

[1] F. Author, "Chiplet Test: Piecing Together the Next Generation of Chips - Part 2," 3D InCites, Jul. 2024. [Online]. Available: https://www.3dincites.com/2024/07/chiplet-test-piecing-together-the-next-generation-of-chips-part-2/. [Accessed: Aug. 25, 2024].

! h# c: O) y' ~; B& L+ ]+ w- g" D/ j

- END -9 P9 B/ Z: @. A4 F& j: a$ p

$ s) e6 }. H: T& p

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

& G/ e( t. ~9 r& F- J, m& j$ {点击左下角"阅读原文"马上申请3 x7 w4 i2 y7 ^' j1 r. N& Z

- n- M/ K# R8 T9 \9 `

欢迎转载3 I, q. O) z( e* d

; f2 e1 Z% C% |. X" Z4 @转载请注明出处,请勿修改内容和删除作者信息!9 G% J8 W9 c7 f m" S! z9 w4 W

4 q. k; U( i8 e

/ D7 b0 U3 v' L8 `. ?5 F+ }8 W9 l: |! d: X6 k

efvy0tjrmun64050447014.gif

9 G7 a* m2 t9 a+ s: \

5 n4 {, p( k* f关注我们

1 j) [* h* O$ u6 m8 q! Q, V/ V2 }! p3 G

* o, a( P% Z! T+ N' ~

do01s2qoyxb64050447114.png

: U& _! a3 p7 u | " |* @6 q; ~+ P0 Y" E! S3 l" O# D4 u9 }( {

jpd5rurhpjy64050447214.png

: I1 v/ C/ E, c7 L8 X7 ?

: I1 v/ C/ E, c7 L8 X7 ?

|

/ ~3 g: S. b5 ^/ C9 {. P p

qppm3pmktdt64050447315.png

6 r8 O0 S! Q% }) s

6 r8 O0 S! Q% }) s

|

, ^7 M- J5 g0 I+ ^: d+ g( w9 p

6 p- a. z& d6 f. k3 y G) a' [+ C& d8 ~4 i5 a9 K) ~' c2 c

! @7 |3 `3 t/ n

关于我们:

& i* K3 D: ~7 s深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

) E, f" {) }4 d. v- S# T' h# l2 Z0 `7 ^. a( w T

http://www.latitudeda.com/

! a, H9 ~% O% n) ^( G(点击上方名片关注我们,发现更多精彩内容) |

|