|

|

引言

9 R7 V! h$ Q9 q# M0 O. s( L在人工智能和高性能计算快速发展的今天,对更快、更高效数据传输的需求不断增长。本文探讨光电共封装(CPO)技术的发展历程、当前状态,以及其在规模化网络和计算架构中的应用潜力。介绍这一技术面临的技术挑战、创新解决方案及其在实际应用中的表现[1]。6 o' ~( x$ }0 G3 l! u

/ V0 Q8 B' \. i9 k9 q+ Z; ]光电共封装技术的必要性9 H* E1 z7 w0 Z3 O

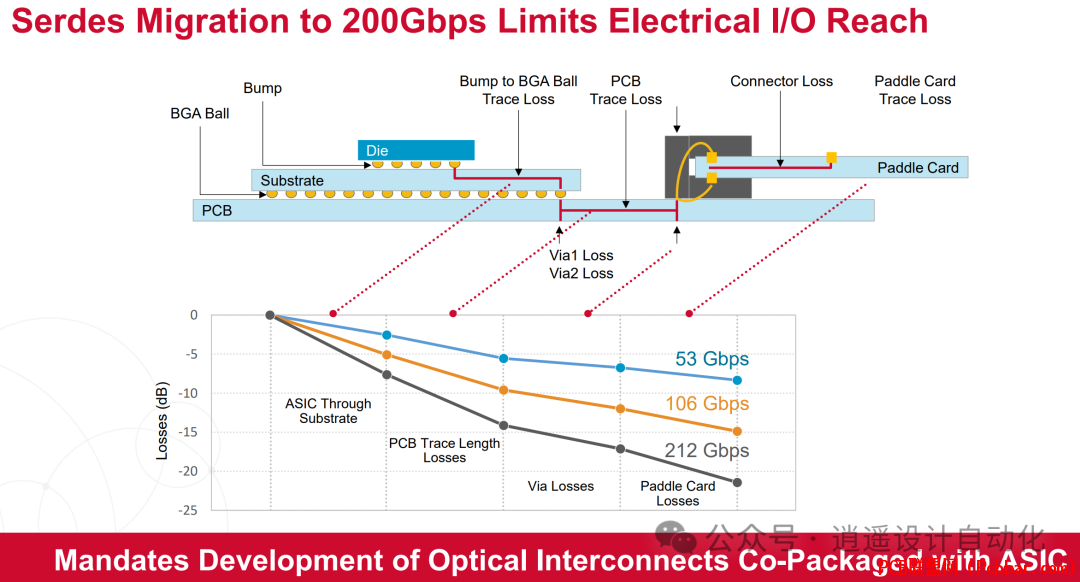

随着数据传输速率不断提高,传统电子互连面临着重大挑战。串行器/解串器(SerDes)向200Gbps迁移的过程中,电气I/O传输距离的局限性日益凸显。

6 P: K1 _1 ]2 b3 N# ?4 [$ r" E+ V& s# F' P+ s6 z

y5w4kbh0u5m6409976215.png

# Q; U8 _9 [1 n图1展示了高数据速率下信号损耗的增加,说明了光电共封装与ASIC集成的必要性。" p1 q' o3 h$ k' U3 U! S3 d5 Q

/ w, ^+ D, d! X9 }; [5 t, k6 l' b在这些高速率下,信号完整性成为主要问题,主要由于信号路径各个组件的损耗,包括:$ V) H3 _- H8 o7 i% Y( F

ASIC通过基板的损耗PCB走线长度损耗过孔损耗Paddle card损耗

: v) z h2 i3 W+ E0 ^

4 t. ^ @$ f3 A$ W1 T' D. T5 H4 a5 A随着数据速率从53 Gbps增加到106 Gbps,甚至达到212 Gbps,这些损耗变得更加明显。图表清楚地显示了更高频率如何导致更大的信号衰减,使得通过电气互连维持可靠通信变得越来越困难。3 w+ O, j9 ]: l5 L+ R( L* `

5 W. ?+ j* Z" |/ ?

这一挑战促使了光互连技术的发展,可以与ASIC共同封装,以克服这些限制并实现下一代高性能计算和网络系统。2 S( G0 `8 D: @0 V; Z' c8 L

, e4 }/ u# h% W; l5 X

光互连技术的演进& e3 H$ y }( {! f3 a

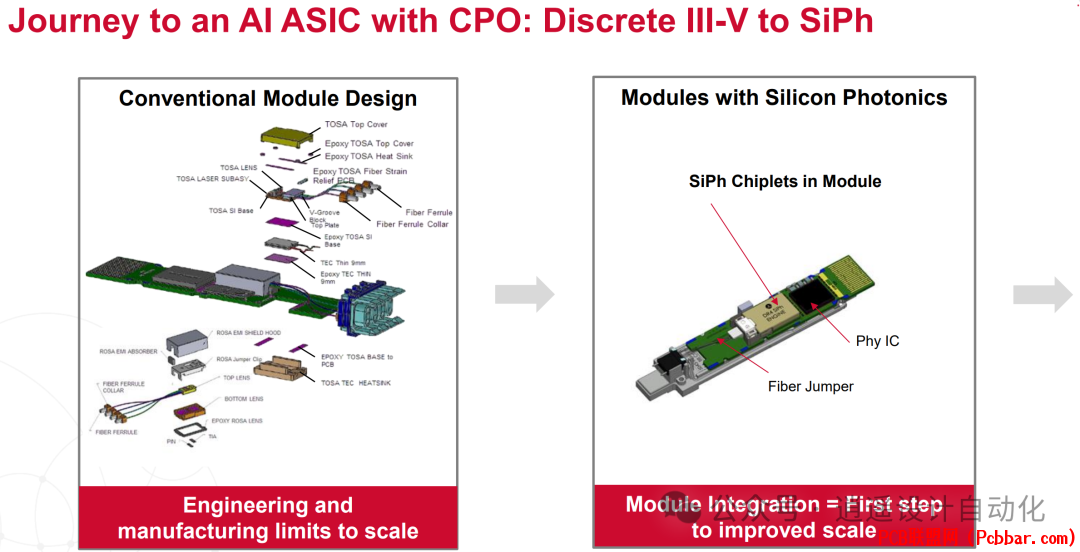

开发具有CPO功能的AI ASIC的历程是渐进的演变过程,从分立元件逐步发展到高度集成的解决方案。$ c' h( S# Y3 d' T) W- X

; A- Q! w" p/ b

nhpp0ayfzm56409976315.png

, G7 E; B5 n Y2 Z

, G7 E; B5 n Y2 Z

5bqsdb3keye6409976415.png

7 p9 k9 ]& e+ k0 e$ l) y

7 p9 k9 ]& e+ k0 e$ l) y

图2展示了从传统模块设计到硅基光电子Chiplet模块的发展过程。& Y; y4 \ [, E( R9 {/ Y! T

传统模块设计:最初的方法使用分立的III-V族元件,在可扩展性方面存在工程和制造限制。模块集成:提高规模的第一步涉及将组件集成到模块中,减小尺寸并提高制造性。硅基光电子模块:在模块中引入硅基光电子Chiplet标志着重大进步,实现了更高的集成度和更好的可扩展性。光电共封装:最后阶段涉及将光学组件直接附加到ASIC上,实现前所未有的集成度和性能水平。! y, T2 m9 F' {4 | f& S2 {5 b

[/ol]1 i* \, G; l: s9 m

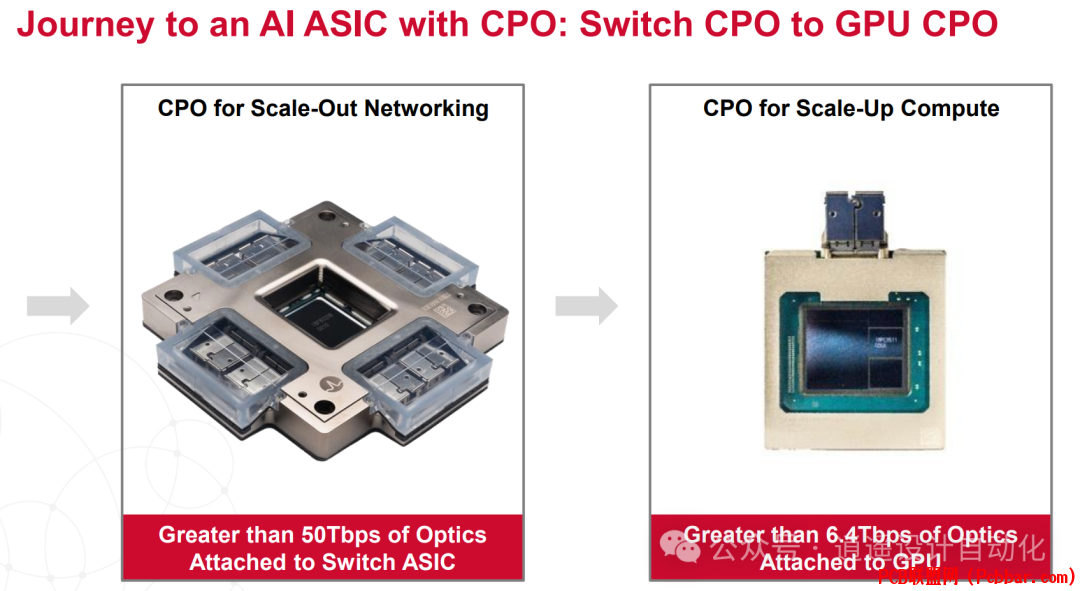

这一演变导致了CPO的两个主要应用:

) `* H3 {6 M, y" j

5 Q& u, A7 z7 n

zzrytwsssqq6409976516.png

3 Z/ ?. u+ b% u8 z a$ ]图3对比了用于规模化网络的CPO(>50Tbps连接到交换ASIC)和用于规模化计算的CPO(>6.4Tbps连接到GPU)。1 w( l" I. i, P K; ]

用于规模化网络的CPO:将超过50Tbps的光学直接连接到交换ASIC。用于规模化计算的CPO:将超过6.4Tbps的光学与GPU集成,用于高性能计算应用。1 `# |4 U1 R, G

[/ol]

- m3 E# m- m0 B# ^% NBroadcom的CPO平台$ B* |4 e- v1 Z) q

Broadcom在CPO开发方面处于领先地位,创建了一个全面的平台,解决了高速、高密度光互连的挑战。

l7 f! k8 M+ j

- T4 D8 _9 \$ z# | ?) o8 o4 ^

qxlxrqockuq6409976616.png

' i0 D: U$ w% b+ A7 ?图4提供了Broadcom 51.2Tbps TH5交换CPO的示意图概览,展示了其关键组件。

: {& Q. r1 R) @: V& U- [1 p

1 Z0 ]" w. @ U, E+ sCPO平台的关键组件包括:

) G, I4 H2 P$ m9 K7 b6 ^51.2Tbps TH5交换CPO,配备8个6.4T光学引擎16个可插拔激光模块(可现场维修)光纤Cable Assembly前面板端口I/O连接CPO(光电共封装)Broadcom FAU连接器PLS盲插连接器(MPO)6 x+ C( b* M/ l4 w8 D* \7 A0 j( `. m

9 e8 C7 }: @* f

7 Z, U! e- e% _" J. |7 I1 c

kaep0astv5m6409976716.png

/ E) W, ] p0 {

/ E) W, ] p0 {

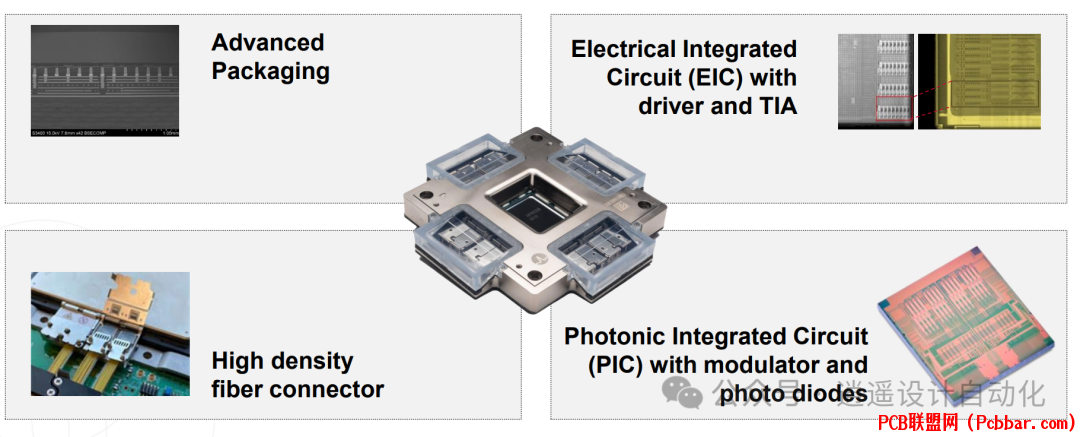

图5突出显示了CPO的关键组件:光电子集成芯片(PIC)、电子集成线路(EIC)、先进封装和高密度光纤连接器。

+ j: g8 |) l. i4 v5 X4 Y9 v$ h7 M2 B9 J: ~) j3 X

CPO系统的核心包括:光电子集成芯片(PIC):包含用于光信号处理的调制器和光电二极管。电子集成线路(EIC):包括用于电信号处理的驱动器和跨阻放大器(TIA)。先进封装:实现光学和电子组件的紧密集成。高密度光纤连接器:便于连接外部光网络。2 Z6 x9 a# h( c2 @. H2 I5 [0 H

[/ol]' y5 M I D( w. c

" F( h, L2 h0 u& Y8 b$ a使用CPO的规模化网络% b ^# N/ y' n7 m) _' y, Q

Broadcom在实施CPO用于规模化网络应用方面取得了重大进展。让我们来看看两代交换系统:! U+ q* N+ i+ l' s

- j/ _4 [( Z- z; J0 C- }第一代:TH4-Humboldt

, E" I/ U. u4 O) g7 ^8 X N/ ~7 ^, R: g2 M

avmpcmsuhs46409976816.png

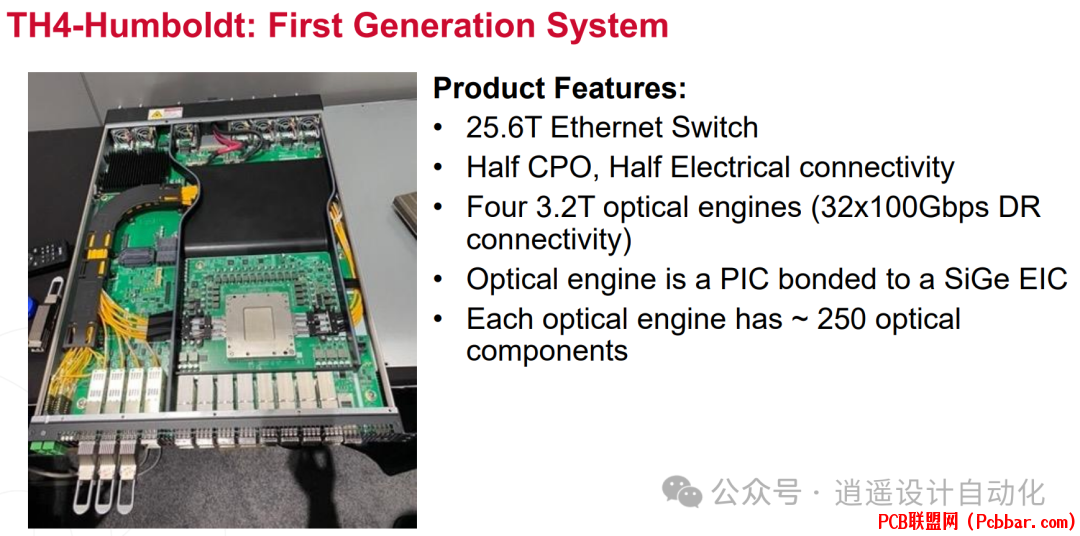

- W0 K2 ]+ u! x4 v C3 R图6展示了TH4-Humboldt,Broadcom的第一代25.6T以太网交换机,部分实现了CPO。1 W% f5 X l5 e* N1 G

- m" }( S* n2 @& Z. uTH4-Humboldt的主要特点包括:8 E D* T6 a1 k \

25.6T以太网交换机一半CPO,一半电气连接四个3.2T光学引擎(32x100Gbps DR连接)光学引擎:PIC与SiGe EIC键合每个光学引擎包含约250个光学组件* {* b+ i7 [. ~

: p& {* e# Q* y K2 n

* q- x* W+ ^4 w9 w( Q& n

0cbisbbttyw6409976917.png

1 p2 e7 W7 _3 S* V4 E& a- ^3 @图7说明了TH4-Humboldt设计中硅基光电子PIC、SiGe EIC和TSV(硅通孔)的集成。7 E4 |" j( F. g# v% C

& H. x) a L& r8 `6 B

第二代:TH5-Bailly$ M! c# X; ~3 \6 y1 @4 e4 z

orlr4vbrlu26409977017.png

; X2 ?' u# H8 x& r2 j5 p

; X2 ?' u# H8 x& r2 j5 p

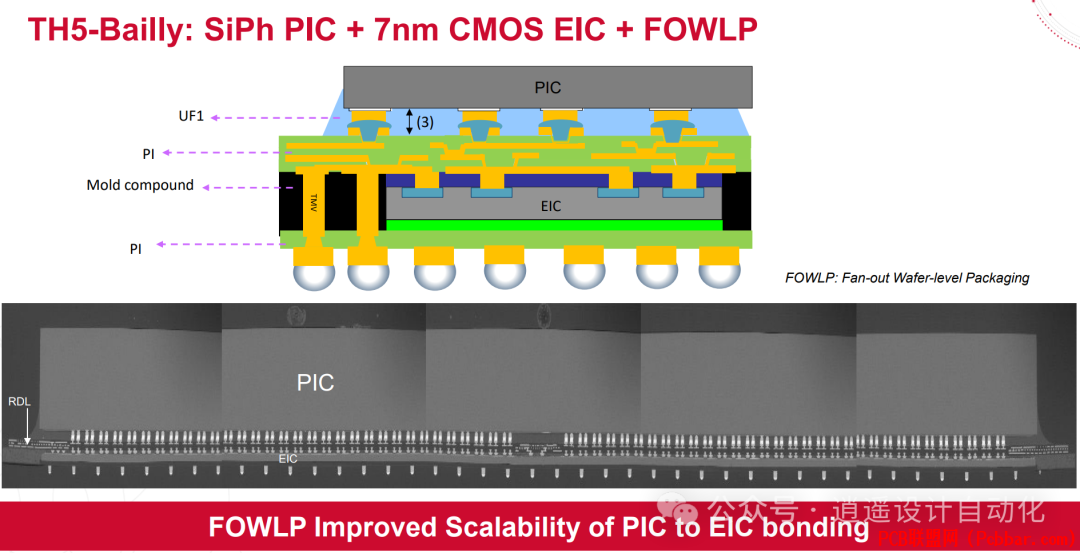

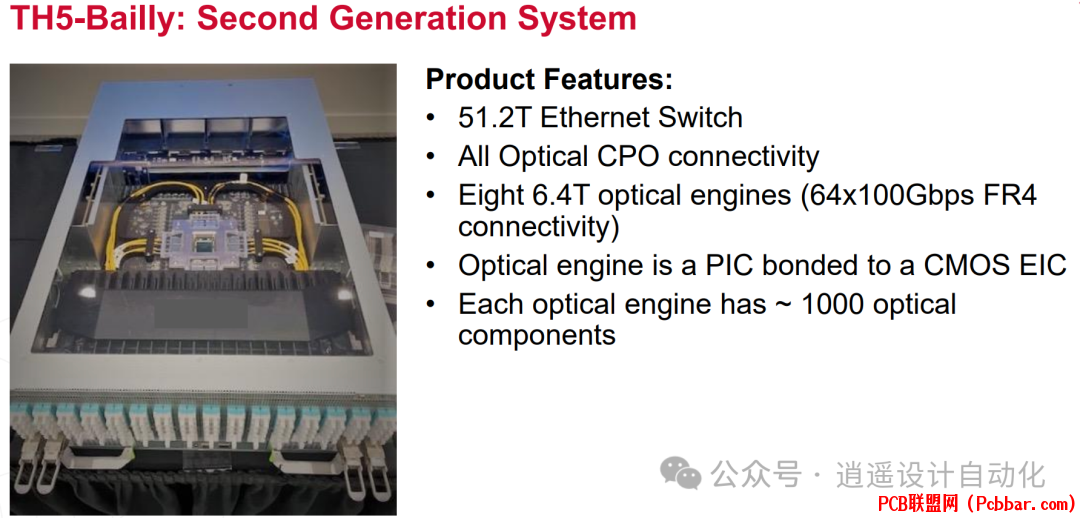

图8展示了TH5-Bailly,Broadcom的第二代51.2T以太网交换机,实现了全CPO连接。5 a# M& \1 Y& i. k3 A" E5 J

4 s6 K; y: q x8 o# }7 U( K

TH5-Bailly代表了重大进步,具有以下特点:

5 H3 ?: k8 W8 Z4 m- {. U# T/ c/ Z0 f7 s9 s51.2T以太网交换机全光学CPO连接八个6.4T光学引擎(64x100Gbps FR4连接)光学引擎:PIC与CMOS EIC键合每个光学引擎包含约1000个光学组件

7 h4 G) B* Q$ O. N) f

! o( P2 q5 y, z- D) I- @2 [

/ g8 w+ T1 T# r0 n9 H

fjz3bnm1hgg6409977117.png

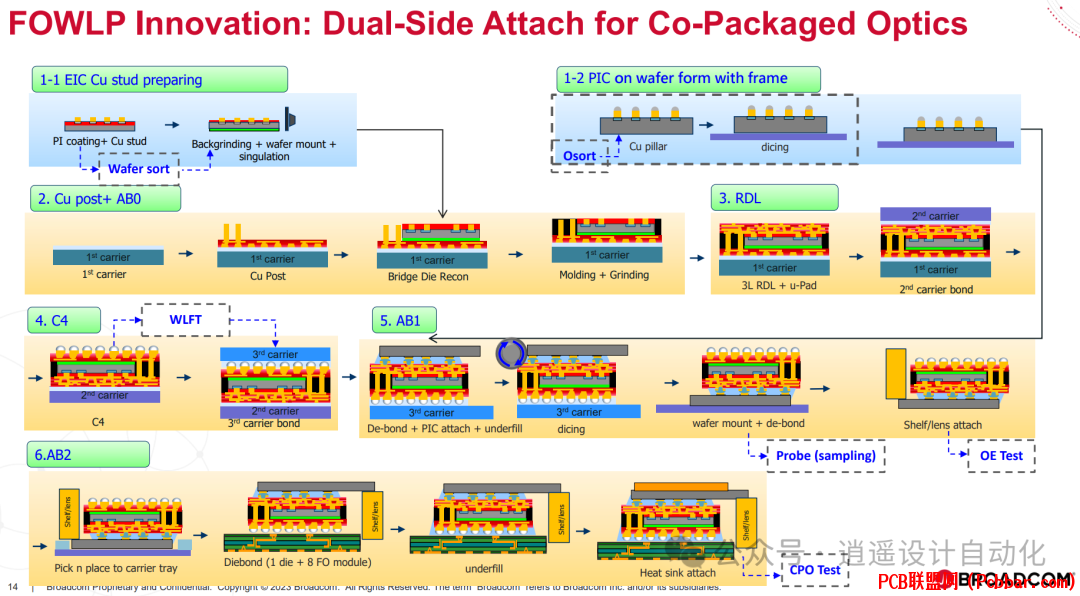

+ m# Y5 q2 L) N图9显示了使用扇出晶圆级封装(FOWLP)技术改进的硅基光电子PIC与7nm CMOS EIC的集成。

: V2 I% y7 ~0 ~

+ |( s! G5 K$ JTH5-Bailly中使用的FOWLP技术实现了PIC到EIC键合的更好可扩展性,允许更高的密度和性能。

8 {6 m7 X. F- y$ |" @% L# i5 e4 L- K

性能和功耗效率

2 X+ y. \ e6 l$ ZTH5-Bailly展示了令人印象深刻的性能和功耗效率:

" X: f5 o) X6 q! r

' g& [( d: l3 R5 u/ L$ H7 t& Q, t

21fnm5r4zll6409977218.png

& @$ U1 M4 K/ H/ I图10显示了完全集成的51.2T交换机72个端口的FEC(前向错误纠正)尾部分布,显示了无错误操作。

% T; P; ]+ Q1 f. y! u

3 e! c! Z% k# s! X6 J2 B0 O) j图表显示FEC尾部快速衰减,表明所有端口都具有出色的信号完整性和错误纠正能力。

$ t% O: w1 G9 I- ]% @5 h$ `) W8 I' J" \" U7 n

qb3tntuhtr36409977318.png

- e8 a. B: D0 _, Z. B, P

- e8 a. B: D0 _, Z. B, P

图11比较了51T交换机盒中CPO和传统可插拔光学的功耗。

8 w& Y, K' d2 _% l% g. r# v6 O5 n1 U( g/ J

主要发现:

! \9 f; m1 t7 o+ H4 T8 L' E使用Bailly CPO的光互连比传统可插拔光学消耗少70%的功率使用Bailly CPO的总交换机盒功耗降低约30%对于32k GPU集群,CPO可实现超过1MW的功耗节省

; l; u# e3 Z7 J$ p) t1 S) T5 s: V# Z! x4 l

使用CPO的规模化计算# H* z2 T2 U+ j. K0 a4 Z

CPO技术不仅限于网络应用;对于规模化计算架构,特别是在人工智能和高性能计算领域,也具有巨大潜力。

V8 ?' J t. _3 T7 k% h- b( B9 e0 w' p# ^

dwhrn31bzjg6409977418.png

' t, v0 G" c9 f- ?& E图12说明了具有CPO的计算ASIC,在2.5D多芯片封装中每个光学引擎具有6.4Tbps I/O带宽。! d0 T. P9 O+ m; K1 y

5 B& m8 ?- y6 m4 M这种先进的封装方法集成了:

* \5 C% P' n a3 ~- U& M5 [1 {计算ASICHBM(高带宽内存)SerDes芯片6.4T光学引擎Chiplet

% t ~- A# t2 \2 K' Q# J9 _0 I& C& X

5 m' p" b$ }, u4 k; m& q在计算ASIC中使用CPO实现了:: o& I$ K2 z; M1 ]- H7 Z& F1 s- M

更高的带宽密度降低功耗改善信号完整性大型AI集群的可扩展性

( V5 X$ W$ [# j" | d, [5 N

* y4 P [- ?+ I5 [6 C$ y: N! [0 Q4 s% R" w- w

uyxw340g0ov6409977518.png

/ p& O7 w% I5 U

/ p& O7 w% I5 U

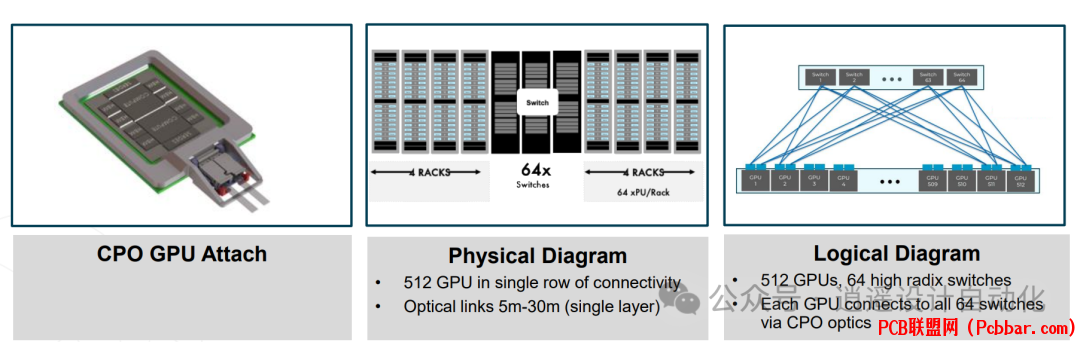

图13显示了使用CPO的512个GPU全连接单级规模化架构。+ `3 j. T9 G% i7 f+ P

$ W+ s. E" |" D/ b# B# r5 b这种架构展示了CPO实现大规模扩展领域的潜力:

, L, ~ j1 s2 Q3 F单行连接中的512个GPU光链路范围从5m到30m(单层)64个高基数交换机每个GPU通过CPO光学连接到所有64个交换机/ K6 m7 L6 ~* |% N4 c# n* K

9 s8 i1 B4 b: `3 M$ `

未来发展和路线图

! X X/ ]5 A, U随着CPO技术不断发展,我们可以期待密度和性能的进一步提高:0 W0 W+ O) U8 X: E2 q8 K

" g; Y4 |6 E! J

eap4distaua6409977618.png

1 g7 F. t* b2 |: ] v% C图14展示了规模化光学Rooftop密度路线图,显示从2025年到2028年从12.8T到102.4T的发展。

& O/ W2 o+ w+ T/ S- |5 `, r

& l# l* a% p$ R5 n. z Y路线图显示光互连密度快速增加:

- h4 c( ?6 S1 J% }2 o. ~8 T8 b2025年:12.8T2027年:51.2T2028年:102.4T(发送+接收)

- @( [9 _) v/ e3 c& I7 X. I# R) f$ }; _) |1 P

这一进展将在未来几年内实现更强大、更高效的AI和HPC系统。: m9 E0 t, V0 W- T

7 }1 K: ?7 b& ~4 y9 g结论

# [5 k# J% A' {1 J5 ]5 |+ T光电共封装代表了光学和电子组件集成的重大进展,用于高性能计算和网络应用。通过克服传统电气互连的限制,CPO使更强大、更高效和可扩展的AI和数据中心应用系统的开发成为可能。

6 S" L% Y7 X( O; u/ R& d) i

- g- Y& D7 R2 u4 d正如我们在Broadcom从TH4-Humboldt到TH5-Bailly及以后的发展历程中所看到的,CPO技术正在快速发展,以满足现代计算不断增长的需求。先进封装技术(如FOWLP)的集成,以及光学引擎密度和性能的持续提高,为下一代AI和网络架构奠定了基础。3 T5 z- y" y; j6 b' K" E' p9 R4 w) `

/ q) O; C& p! s% H0 U

CPO的优势,包括降低功耗、改善信号完整性和提高带宽密度,使其成为应对网络和计算系统扩展挑战的关键技术。随着技术的不断成熟,我们可以期待看到更多创新应用和架构,利用集成光电子技术的力量推动高性能计算和AI世界的发展。

) Q7 u* G5 i3 {1 _/ |9 [% l

6 ^ e7 r) f! q; n/ x( {( S参考文献3 M2 N+ r# m* ?5 J1 e N+ D

[1] M. Mehta, "An AI Compute ASIC with Optical Attach to Enable Next Generation Scale-Up Architectures," Hot Chips 2024, Aug. 26, 2024.7 G# O: [. U7 b5 ]

$ ~, I; q# E) x& H+ D- END -

( H! ?; u' Y) E3 {. N2 W: s- J

6 @4 Y& F! }- {' ]/ e4 L- n8 a4 |( \9 ^4 B5 w. j- h3 N& g* {/ ]' @

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。* U" K% @& ?- ^

点击左下角"阅读原文"马上申请

$ f8 t: g' i# |6 }5 H7 @0 O4 l

6 W& Z( `" z4 \" }* T欢迎转载" X! h, {5 j3 C- ~5 D6 G

+ P" b. l4 [( s7 {. l h转载请注明出处,请勿修改内容和删除作者信息!7 G; Y1 Q `" h: @. p

3 _+ `8 d% `" A- V$ B

# Y7 T; V1 R9 D$ {; I- ]0 J# Z

8 v- s& U: x( e3 I$ |

tl2y5mxgkdz6409977718.gif

0 p) A# N8 a8 a5 ?: g% |

0 p) A# N8 a8 a5 ?: g% |

/ ?) j# l; f H/ H, ^: V

关注我们# v7 A- d9 d1 a. F$ s. N2 p" D/ H

' `2 P3 Y! y; X9 C& d$ Q* ~1 m

7 d; i9 W% H, m2 E% U4 j

ji4uymkena16409977818.png

/ ]$ _( }- v& {! {

/ ]$ _( }- v& {! {

| % w5 @4 B# C$ O y, ~5 m

3jpatpf4vcv6409977918.png

$ F1 T4 q( T7 x1 Y

$ F1 T4 q( T7 x1 Y

| 0 E2 |2 I, l6 g j/ I* J

5t2mrkpsbym6409978018.png

; ]5 b( N" G |& | |

1 }# } n( ]$ m% N4 B- r

, X" m, D# c4 W9 `3 l5 A2 U$ I6 h, o) p: \" V d

. c6 G6 K) k0 Z/ b

关于我们:1 K8 v8 N* t8 t9 `. c- [7 U

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

4 E$ Q- a* w2 [' C! [, y0 }8 _) w- Z9 o( p; C: b

http://www.latitudeda.com/

) _6 y6 R/ ~, S3 A(点击上方名片关注我们,发现更多精彩内容) |

|