|

|

引言. ?7 P" P% E: d, r) H9 w0 ^$ L

在半导体技术飞速发展的今天,人工智能(AI)正在成为优化芯片设计过程的关键工具,本文帮助读者了解AI,特别是强化学习(RL)和生成式AI,如何应对现代芯片设计的复杂挑战[1]。

3 k0 H- y' O3 z4 v4 l5 B4 R7 ?

芯片设计复杂性的挑战4 A) u: P: B9 z6 k

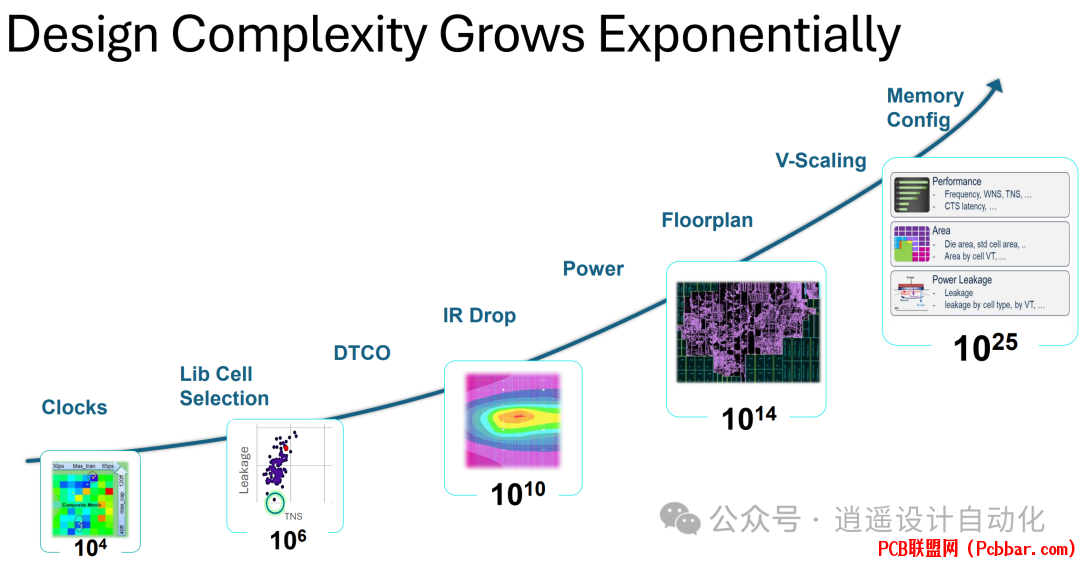

现代芯片设计是涉及众多变量和权衡的复杂过程。随着半导体技术不断推进,设计空间的复杂性呈指数级增长。. v8 u) l6 [$ P

d1shonlpwai64034882926.png

$ c" R( q- x5 J) z. r9 u F0 h图1展示了设计复杂性在时钟、库单元选择和电源管理等多个因素上的指数级增长。, ^3 U3 H% Q+ i; E

6 |' A# o- j! F0 v4 _ c5 }, c这种日益增加的复杂性带来了几个主要挑战:" `6 g4 W( B' M) y5 n1 [

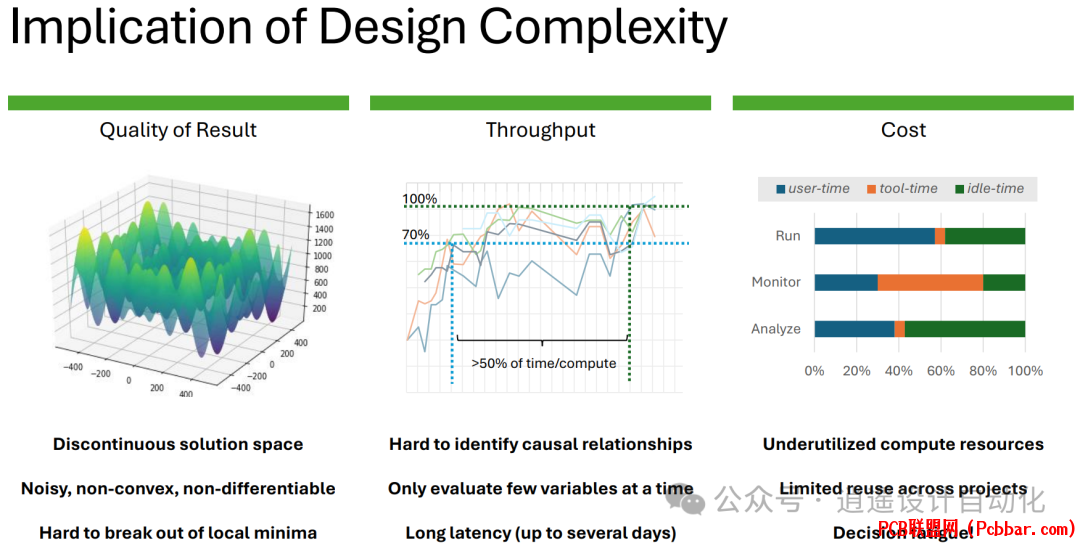

结果质量:解决方案空间不连续、噪声大且非凸,难以跳出局部最小值并识别因果关系。吞吐量:设计人员一次只能评估少量变量,导致设计过程延迟长。成本:设计过程常常导致计算资源利用率低下,跨项目复用有限。

$ d: m$ v& A% G$ W% q# |1 Y' {

7 a9 u! m* A; x0 `/ B

) Q6 ^7 G) [, h- `1 W G

4bprb3o41ud64034883027.png

1 ` A/ G$ `0 C5 u! |4 V/ B& | J

1 ` A/ G$ `0 C5 u! |4 V/ B& | J

图2显示了芯片设计过程中时间分配的breakdown,突出显示了当前方法的低效之处。

. \; n _) j" {3 ^# u& G- a' t' K f- G- I4 m; A0 ]( `* s3 @

AI在芯片设计中的应用前景

C* b. T& l# ~ @% L3 I9 j/ f" O为应对这些挑战,半导体行业正转向AI,特别是强化学习(RL),以优化芯片设计过程的各个方面。7 Y( W2 _9 a l p4 r

2 b- e; r4 Y' E9 [ r: B$ y

理解强化学习, d( I1 |/ Y: S" t- L$ ^" z8 H. W

强化学习是机器学习的一个分支,其中代理通过与环境交互来学习决策。在芯片设计中,RL代理可以探索各种设计选项,学习实现所需性能指标的最佳策略。

5 c! k9 n' M& z4 d

wtdqj5jnstl64034883127.png

3 Z2 T3 r# j" M图3描述了强化学习的基本概念,展示了代理与环境之间的交互。4 I* v: O: S/ t; M) |* b

/ X" u# e1 z) Z/ ~

将RL应用于芯片设计

6 ]/ P3 h- [& M9 n将RL应用于芯片设计涉及将各种设计参数和约束映射到RL框架:

& x6 P/ a3 z- s) p- Z/ g) x( t+ o# u- S状态:当前设计配置动作:对设计参数的更改奖励:目标指标的改善(如功耗、性能、面积); y- F; k" t8 C3 u/ D+ d! ^ I

/ a4 K" Q! _8 b9 w0 A

% ?+ G7 H5 M3 Z. k& s V

efv4512mfi464034883227.png

) h. I4 ^, R! L- b

) h. I4 ^, R! L- b

图4说明了如何将RL应用于芯片设计问题,将设计输入映射到动作和结果。

3 c7 m4 n- a; t7 { [+ g0 A! N! o0 ?- o3 Y1 @

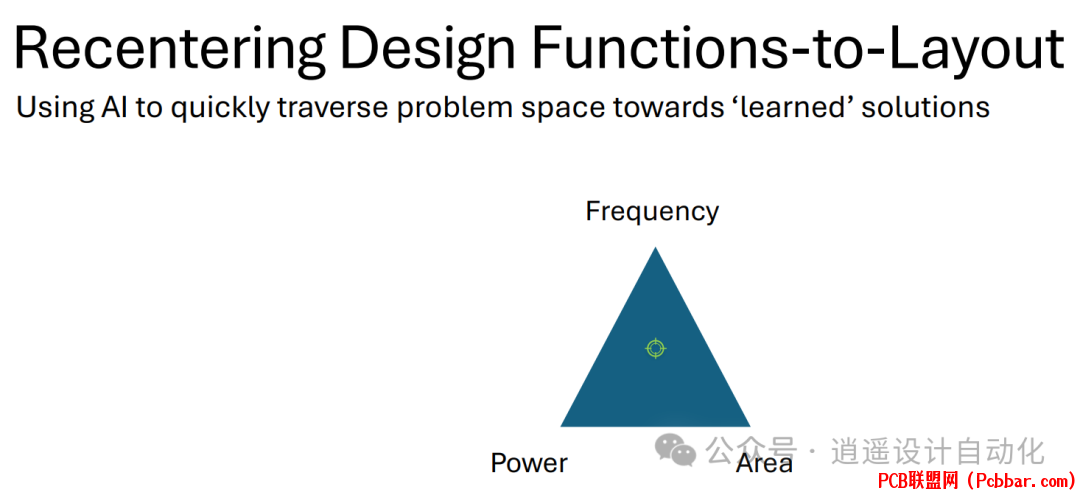

AI辅助优化贯穿设计流程

- G4 V8 T+ A7 x) T3 I/ PAI驱动的优化可应用于芯片设计过程的各个阶段,从架构到制造。5 P0 ~3 K! G. D! X$ R4 E

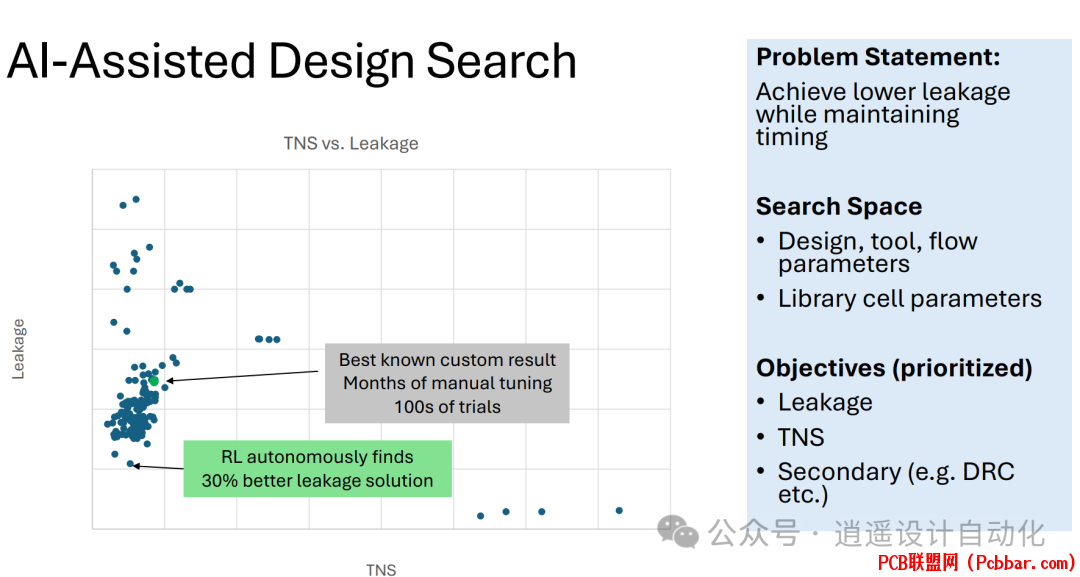

( e$ p" N. T& t& o6 e1.数字实现

1 Z3 ?* F$ ^* R3 u GAI可以辅助探索不同的平面图选项,优化芯片面积和最大频率等指标。

4 o: _1 {, V( U+ g6 m, U' P

3wwioxv2aro64034883327.png

& Y/ K( S4 G; M+ o图5展示了AI优化设计的帕累托前沿,平衡了芯片面积和频率。

- z; M- z/ m5 B2 y0 Q8 }2 |7 d% V

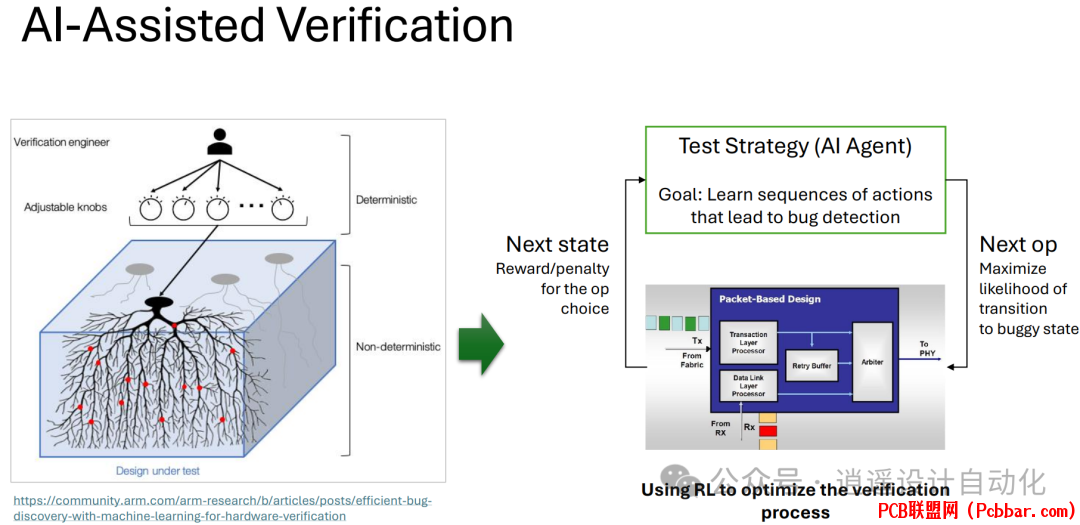

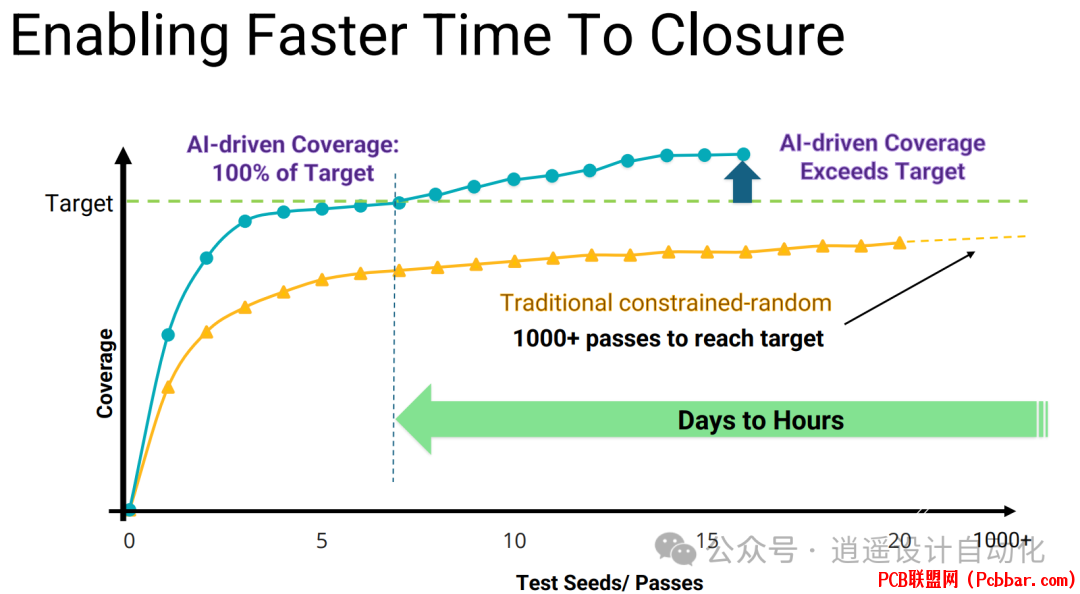

c# D) L- _6 W0 z1 }' |' V ? Z2.验证

. W( A \) ?$ B% H! P) }+ yAI可以通过智能选择测试用例和优化覆盖率,显著提高验证过程的效率。

2 s! p# C. k" b. ~: Z, m6 F

ulo20taddbd64034883428.png

+ v4 t8 z# u, x4 u图6演示了AI如何优化回归测试的分布,以实现更高效的验证。

; c/ j: X: ?9 s0 ^- y+ @4 r3 c

, z& i! i8 x) q7 Y3.测试和ATPG1 e3 B U/ R& L- @9 K

AI可以优化测试生成的各个方面,包括非扫描设计、X处理和中止限制。

; I% x1 M% @# i1 q, U

1 A W# |4 } ^$ C, K4.电路优化3 j8 ~' g) X; w) J) B" g& ]5 R4 ~

对于模拟和混合信号电路,AI可以在复杂的器件参数空间和PVT(工艺、电压、温度)角落中导航。

* {& Z/ n6 t4 Y& j

2 r2 L8 G% ]2 q R! S' m2 L* d5.3D集成

+ y8 Q5 U3 l1 e! P8 A" f G+ N* X9 AAI可以辅助多芯片配置的探索,优化性能和功耗效率。4 O- u7 ^0 N- P5 y

5 o" c$ S! U$ k; V* [3 ^+ Y; {

6. 多抽象层次优化

; Z! @5 a- B- E$ i6 z+ n4 u/ BAI在芯片设计中最有前途的应用之一是跨不同设计抽象层次进行优化。7 v' K) z* ?, ^3 F

0qjhttmsz0n64034883528.png

, J( W: e- x( s, e. S图7阐述了跨多个设计抽象层次优化的概念,从高层架构到低层实例。

/ P% H4 W# w. c! h+ }9 ?" B3 L: X$ R

7.单抽象层次vs多抽象层次优化6 N- T& ^& W% U( J% ^0 t! {

最初的AI驱动优化集中在单一抽象层次,如布局优化。然而,当应用于多个抽象层次时,AI的真正威力才得以显现。

4 I- w, j* A9 j H5 u

mxxbw5fllhz64034883628.png

; X+ e$ ]8 S# w4 C. `& Y图8显示了基于RL的布局优化结果,展示了功耗和频率的改进。) p$ L: H" l7 H$ L7 ^

% d1 W9 J+ s1 Z5 V5 g: i2 y

xexfbdvlp0w64034883728.png

6 E. L+ \1 N' Y, g/ L3 \* G0 q

6 E. L+ \1 N' Y, g/ L3 \* G0 q

图9比较了单抽象层次优化和多抽象层次优化,揭示了功耗-频率权衡的显著改进。' X" g1 T: X% r6 ^3 R* o

8 `! C9 q0 B; ]! M& Y7 m: h& w7 t

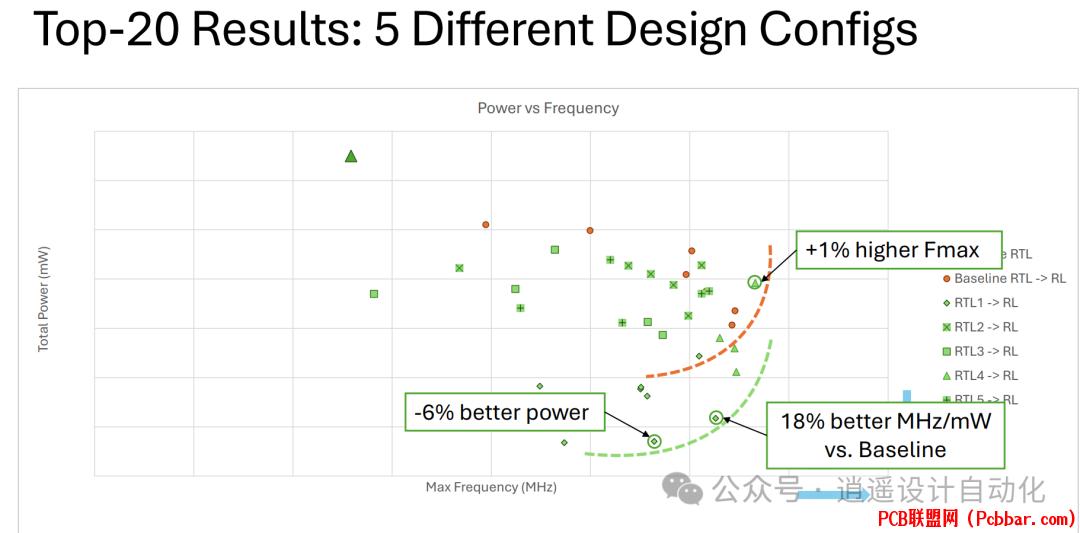

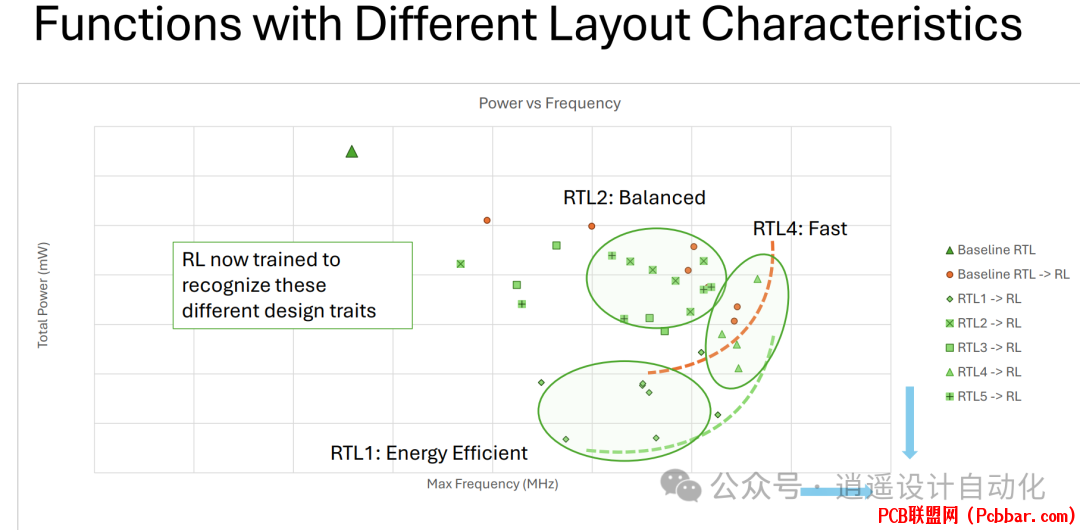

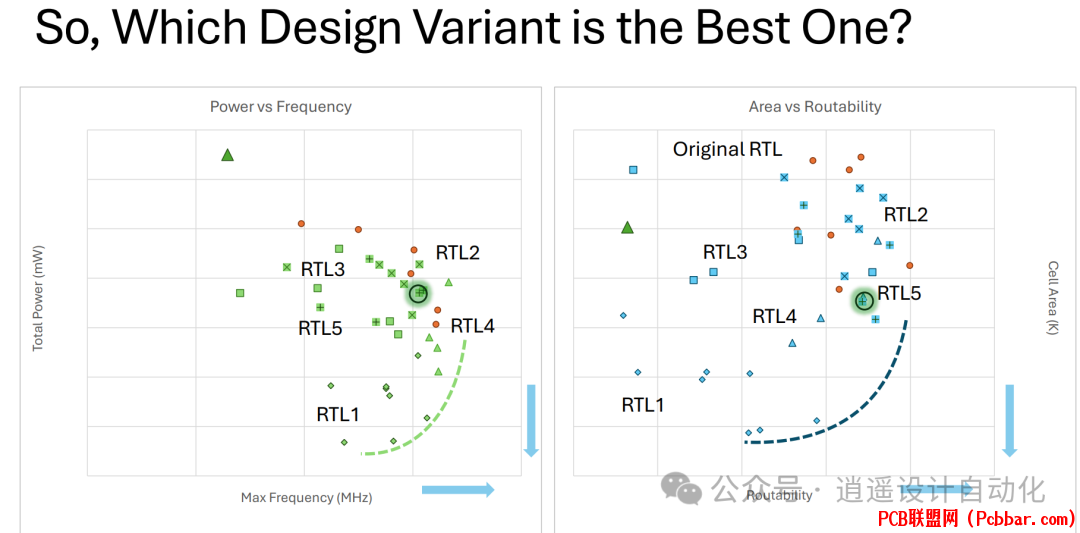

8.探索不同设计配置& J8 K& E/ _5 K1 q/ H9 Y% [1 m

AI可以高效地探索多种设计配置,每种配置具有不同的特性和权衡。

7 r& `/ h3 A% B/ Z. e/ i

1ly0ttoawws64034883828.png

, c& @- ~3 w" a/ R7 `% p, j" L

, c& @- ~3 w" a/ R7 `% p, j" L

图10呈现了探索五种不同设计配置的前20个结果,展示了AI可以生成的解决方案的多样性。

7 U8 y. J8 I& x$ w6 l& j7 C; y+ q; k8 B. Q$ h( ?/ {9 o

rkh2rtxptpe64034883928.png

7 e1 D) T: [ Z

7 e1 D) T: [ Z

图11突出显示了不同的RTL配置如何导致不同的布局特征,展示了AI识别和优化不同设计特征的能力。

: P" t+ j7 F2 u0 d& F( p7 |

8 E& I3 j% L$ h4 }0 a( s4 z! \

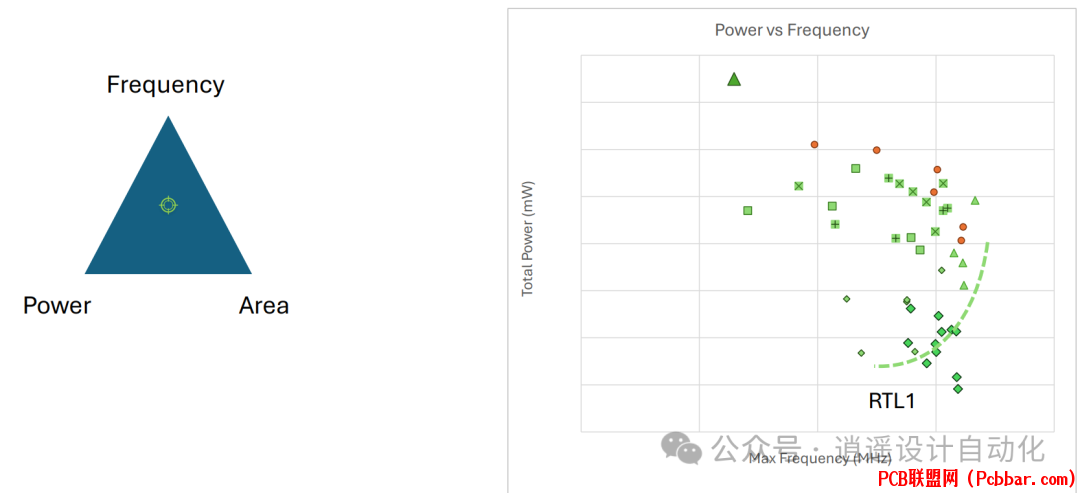

) b5 s9 C; M- \! V基于RL优化的局限性7 J; _5 {; ?4 i! M

尽管功能强大,基于RL的优化面临两个主要挑战:创建设计变体的工作量大设计变体评估速度慢6 v. V. r ?5 X, ^* S+ Q% g

[/ol]

4 v) F0 T7 f! b- T+ g* G为解决这些限制,业界正转向生成式AI作为补充方法。

" x9 x8 A! Q8 i) Y4 H$ J6 M( [. b/ J' a% d' Z4 ^6 B+ t4 A' C# S: @/ W" y

用生成式AI增强RL

8 F; ?1 {1 p7 x) z! q4 N X: E生成式AI,特别是大型语言模型,正在为芯片设计优化开辟新的可能性。$ a4 o8 B& X* b1 b8 Z$ M

& S- w4 \- i2 V! B7 S+ nRL和生成式AI的比较2 y7 }( J+ A0 L: _6 @: q

RL擅长在定义的搜索空间内找到最优解生成式AI善于快速生成多样化的设计选项. S/ z) X2 q; r2 ~5 u, s. f4 y" B O

' `) a" L& _: D) F2 y

5avsevicsyo64034884029.png

) z# s1 k" E# U

) z# s1 k" E# U

图12比较了RL和生成式AI在芯片设计优化context中的优势。

) A4 c2 V3 ~% `' R

& Q7 ~+ L; a! x, S! G _! T' V/ O9 B! ~" E" K

硬件描述语言(HDL)生成* j8 w: `! n# t: O8 \" r

最近的研究在使用AI生成HDL代码方面显示出了令人鼓舞的结果。( j% s$ g9 e; J) z( \

irftfgae0p264034884129.png

5 m/ s: X; c2 y/ }" D' i图13显示了HDL-GPT(一个用于生成HDL代码的AI模型)在各种设计挑战中的表现。

7 m. k+ Y d s' }1 m% r6 ~

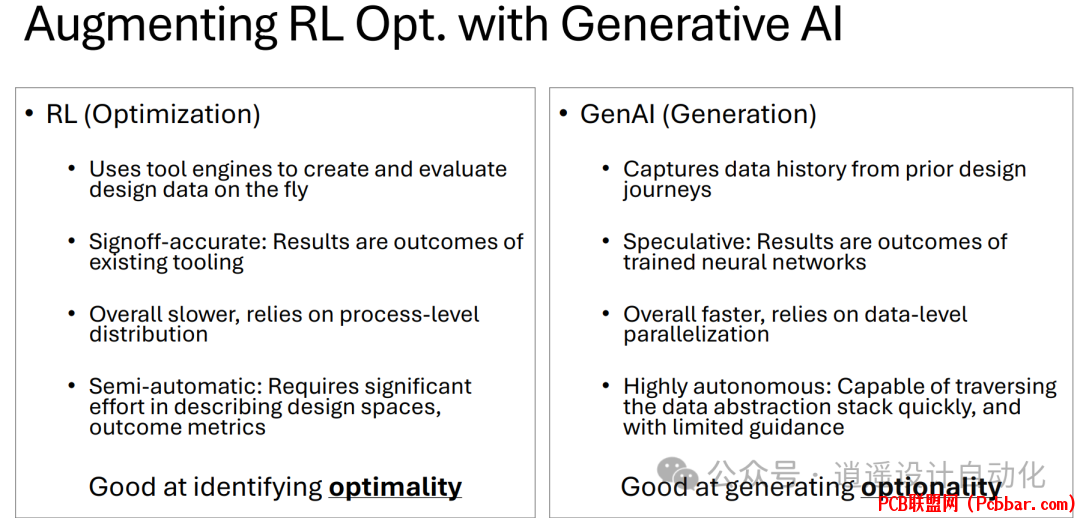

J s& q* v* O# K1 x. U: J+ S2 B功耗、性能和面积(PPA)推测9 }8 L; b$ x) g: B _

AI的另一个令人兴奋的应用是快速PPA推测。

$ f- Q" X$ ?( {

qemdwgitzkp64034884229.png

8 [% h$ K% C5 E9 A$ W4 |7 U

8 [% h$ K% C5 E9 A$ W4 |7 U

图14说明了使用AI执行端到端PPA推测的工作流程,可能将设计评估速度提高10倍。/ p3 ]( S% r* b9 D' c

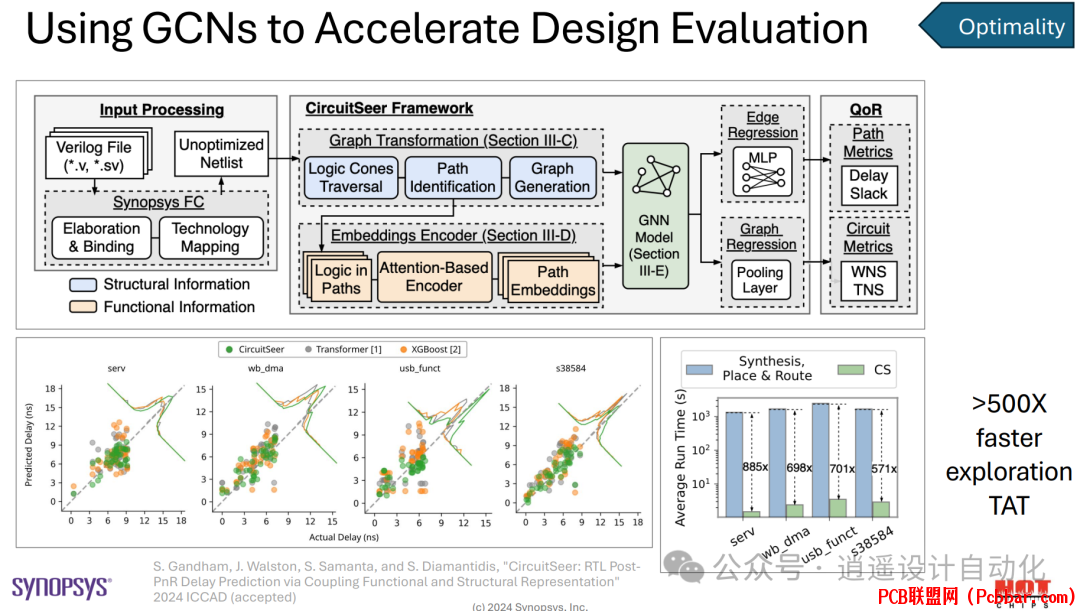

& | @; o$ M& B加速设计评估

6 Y. ^; h" E; M0 R; o- ~图卷积网络(GCNs)正被用来大幅加速设计评估过程。

( o, S7 E# @' ~" G7 n. V! ?5 X" F' v

tqkzaa2rfij64034884329.png

9 U# Z$ c9 s8 ?1 }- o( b

9 U# Z$ c9 s8 ?1 }- o( b

图15演示了GCNs如何将设计探索速度提高500多倍,相较于传统方法。- P5 S$ |) W! l. Y$ i1 A

3 A: e, J3 q& X$ ~结论

9 x$ W' M& h- D& I" V5 o. `AI辅助芯片设计代表着半导体行业的范式转变。通过利用强化学习和生成式AI,设计人员可以更高效地探索广阔的设计空间,跨多个抽象层次进行优化,并加速整个设计过程。

1 d9 T5 \7 H3 Y4 ~. ^, I4 j$ G. O/ W( H+ t2 u+ Y& B3 t

随着AI技术的不断进步,可以期待更深远的影响。RL优化与生成式AI快速设计空间探索的结合,有望在半导体设计中释放新的创新水平。: \) I( X$ p E( T

' R, ^2 G! ? w

芯片设计的未来可能会看到AI工具在整个设计流程中的更深入集成,从高层架构决策到低层物理实现。这种AI驱动的方法不仅将提高芯片的质量和性能,还将显著缩短上市时间并降低开发成本。

1 L$ L+ Z7 O% H& N- r$ ^9 Z

4 v3 _+ I+ z- _' x; t& A参考文献" f" e7 K1 u' V8 d, C6 O2 x4 g

[1] S. Diamantidis, "AI-Assisted Chip Design Tutorial," in HotChips, Aug. 25, 2025.3 _( A! I7 R; f5 J2 R& l3 L: N

2 d( e' I n$ S/ t- END -2 D% q/ f: V3 v+ S v

& |3 \6 j, o" c0 |0 B+ w软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

0 O- Y3 p% Q1 v3 S: N7 H点击左下角"阅读原文"马上申请% q3 K& E- n% F* Y/ |

5 {! B' S# B3 F

欢迎转载2 o% O$ V. m; C7 j' s

4 Y% p3 A4 f2 | Q转载请注明出处,请勿修改内容和删除作者信息!& V- \+ f# p c# O% d

6 x7 c# `: W2 B7 u; D% X/ l1 g# ?5 J: d0 o: W' N

+ W3 h! I# ?' V- Q* u

ywildxob4dq64034884429.gif

8 q5 M) w, b6 p. N1 h' x5 F2 j% _5 |

关注我们0 ?/ c" ^3 t3 B; v( S& f5 {

+ R/ |/ [2 I* g

" X; ]* n; ~' v: q6 B+ {6 ~

xdet4q0xui264034884529.png

6 R$ ~' }4 g& l7 `( o; n0 H) {4 L

6 R$ ~' }4 g& l7 `( o; n0 H) {4 L

| , t+ T) I) Q# B$ u7 ~

5ftmlwfz2xq64034884630.png

/ w( [; a+ ^' J; i$ w7 S

/ w( [; a+ ^' J; i$ w7 S

|

3 q8 |4 ^5 ]) o% h' r

1nykyram4zi64034884730.png

) `: a$ j" Z! p/ z+ X

) `: a$ j" Z! p/ z+ X

|

/ R4 V' z) m( f+ A' Y3 e4 M! e, o

! r) f, k1 p6 J( U. o

+ w% X0 U+ m5 ^) Q( W

8 e$ A0 h4 S8 s6 v( @$ H, }关于我们:. I/ u4 {9 W4 ? Y6 S' i- [, a" T

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

, s/ J" w, L0 _! c

9 Y/ _- }8 [6 Rhttp://www.latitudeda.com/* K! X& J' T# _/ E7 [

(点击上方名片关注我们,发现更多精彩内容) |

|