引言

2 ]) y W- I5 q! L随着数据需求的持续增长,高性能计算(HPC)在高速以太网领域正在快速发展。这种增长加剧了网络系统芯片(SoC)设计的复杂性,包括交换机、网络接口卡、重定时器和可插拔模块。带宽密集型应用正在从400G向800G,最终向1.6T以太网过渡。就SerDes数据速率而言,这种演进意味着每通道从56G到112G再到224G的飞跃[1]。& D% Z# Q' m* ]; O

" q; H' c! [! g5 l0 C g

在56G SerDes出现之前,非归零(NRZ)信号是主导的信号形式。NRZ使用编码的二进制数据作为一系列高低电平,中间没有返回零电平。NRZ信号通常使用模拟线路,因为具有低延迟,非常适合高速应用。

0 g7 O% X3 F6 g- `, P0 f E4 E" }8 n3 s

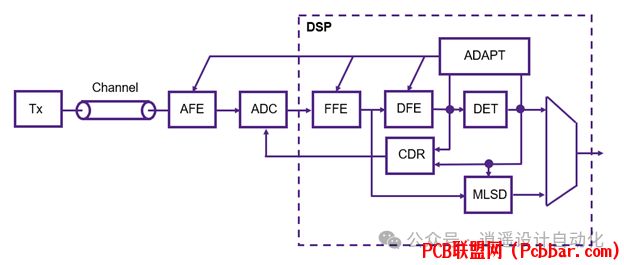

然而,随着数据速率持续上升,对更先进的信号处理能力的需求也随之增加。从56G到112G再到224G的SerDes设计中,数字线路开始占据主导地位。数字信号处理(DSP)线路使先进的信号处理成为可能,如均衡、时钟和数据恢复(CDR)以及自适应均衡,这些技术在确保高速数据传输的可靠性方面发挥了关键作用。此外,对更低功耗和更小尺寸的追求导致数字SerDes线路被广泛采用,因为这些线路消耗更少的功率,可以使用更小的晶体管实现,有利于高密度集成。$ D# s4 l9 u B4 u

0 Z: R9 X4 n6 @/ p3 c/ V四电平脉冲幅度调制(PAM4)已经成为高速通信系统首选的信号方法,因为每个符号可以传输更多数据,并具有更高的能量效率。然而,PAM4信号需要更复杂的信号处理技术来减轻信号退化和噪声的影响,确保在接收端可靠地恢复传输的信号。

+ P& y* ]( s- |; R; C* a

! ^0 R+ Q9 V' @0 A) I D/ k2 X

uu1gbob3tdj64090411052.png

; [/ W8 F% [, ~* `! i" z; C9 g图1:112G及以上PAM4 DSP。说明了高速SerDes的PAM4 DSP系统的各个组成部分。8 a+ \% ]2 t7 \5 l1 n# ~& [. G& U

" z7 F0 H: E( v; B. \% f l2 T

均衡技术

, `1 C8 m/ P$ U* j$ G+ f% R% x+ K均衡在PAM4 SerDes DSP线路中发挥着重要作用。均衡线路补偿由信道损伤如衰减、色散和串扰造成的信号退化。可以采用几种方法实现PAM4均衡:前馈均衡(FFE):这种技术通过放大或衰减信号的特定频率分量来补偿信号退化。FFE使用线性滤波器实现,该滤波器放大或衰减信号的高频分量。FFE线路使用均衡器抽头来调整滤波器系数。抽头数量决定了滤波器的复杂性及其补偿信道损伤的能力。虽然FFE可以有效地补偿衰减、色散和串扰,但在减轻符号间干扰(ISI)方面效果不佳。判决反馈均衡(DFE):这种更先进的均衡形式补偿由ISI引起的信号退化,ISI是指前一个符号的信号能量干扰当前符号而导致的失真现象。DFE通过从接收到的信号中减去估计的信号来消除ISI。DFE线路使用前馈和反馈抽头来估计和消除ISI。反馈抽头补偿前一个符号造成的失真,而前馈抽头补偿当前符号造成的失真。虽然DFE在减轻ISI方面很有效,但需要更复杂的线路。自适应均衡:这种技术根据信道的特性自动调整均衡系数。自适应均衡使用自适应算法来估计信道特性并更新均衡系数,以优化信号质量。自适应均衡线路使用训练序列来估计信道响应并调整均衡器系数。这种方法使线路能够适应变化的信道条件,在减轻各种信道损伤方面非常有效。 t/ ~* C# l5 G0 {/ v' C

[/ol]# g! h* E4 o$ g( A4 U

时钟和数据恢复(CDR)

, s1 M3 }. b; B+ J* q; v9 y时钟和数据恢复(CDR)是PAM4 SerDes DSP线路的另一个关键功能。CDR线路从输入数据流中提取时钟信号,以在接收端同步数据。在PAM4中,由于信号转换次数增加,时钟提取过程变得更具挑战性,使得难以区分时钟和数据。PAM4 CDR可以使用两种主要技术:锁相环(PLL):这种技术将振荡器频率锁定到输入信号的频率。PLL测量输入信号和振荡器之间的相位差,并调整振荡器频率以匹配输入信号的频率。PLL线路使用压控振荡器(VCO)和相位频率检测器(PFD)来生成时钟信号。在PAM4 SerDes中,基于PLL的CDR是更常见的选择,因为与基于DLL的CDR相比,具有更好的噪声鲁棒性和抖动性能。延迟锁定环(DLL):这种技术测量输入信号和参考信号之间的时间差,并调整输入信号的相位以与参考信号对齐。DLL线路使用延迟线和相位检测器(PD)来生成时钟信号。基于DLL的CDR在PAM4 SerDes中较少使用,因为对噪声更敏感,抖动性能也比基于PLL的CDR差。

0 Z9 ^8 k) ` A. I[/ol]4 q) V$ i f: ~2 u+ u; r' H

先进的DSP技术) }% P! r/ e p' a( @* n D

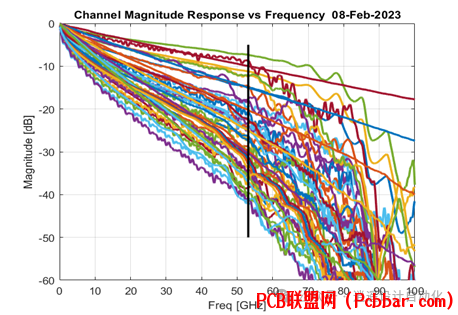

随着数据速率持续增加,需要更先进的DSP技术来维持扩展距离上的信号完整性。最大似然序列检测(MLSD)就是这样一种技术。# v4 W% V' c& ?/ v- t

# k. M2 w3 F7 [% P$ m6 y

MLSD是一种数字信号处理技术,利用统计模型和概率理论从接收到的信号中估计传输的数据序列。通过生成所有可能的数据序列并将其与接收到的信号进行比较,找出最可能的传输序列。MLSD算法使用信号和信道的统计特性来计算每个可能数据序列的似然度,选择似然度最高的序列作为估计的传输数据序列。) q/ j- Y* o8 g

3 {$ ^! Q* @9 ]+ j

g5rwm5ykwz064090411153.png

! g" ]5 f" u) `. V. n) `

! g" ]5 f" u) `. V. n) `

图2:MLSD的需求:40+ dB IL信道库由224G SerDes均衡。此图展示了MLSD在均衡224G SerDes高损耗信道中的重要性。! [* y D. Z2 _3 z7 c

* K) r* H' U+ M" A4 i虽然MLSD计算密集且需要大量处理能力和内存,但在具有高噪声、干扰和色散的信道中,可以显著提高信号质量和传输性能。& P, V( {; \* v5 f1 W: e4 s

! s; Y3 l% q3 q4 c- I$ G/ F' [MLSD有几种变体,包括:

! ? i* J- B6 B [1 H! [Viterbi算法:这种流行的MLSD算法使用格状图生成所有可能的数据序列并找出最可能的序列。在具有中等噪声和ISI的信道中,可以提供出色的性能,但在严重的信道条件下可能会遭受错误传播。判决反馈序列估计(DFSE):这种MLSD算法使用判决输出的反馈来提高序列估计的准确性。DFSE在具有高ISI和串扰的信道中可以提供比Viterbi算法更好的性能,但需要更复杂的线路和更高的处理能力。软输出MLSD:这种变体提供传输数据序列的概率估计。当与前向纠错(FEC)技术(如低密度奇偶校验(LDPC))结合使用时,可以显著提高系统的纠错性能。

0 S, m: ?8 g) O3 o) Z. P9 O% \% e) l5 Y. T

前向纠错技术$ r3 Y+ y* [: t( i9 |) y

除了DSP方法外,前向纠错(FEC)技术在传输信号中添加冗余数据,以在接收端检测和纠正错误。FEC是提高信号质量和确保可靠传输的有效技术。PAM4 SerDes中常用的两种FEC技术是:Reed-Solomon(RS):这种块码FEC技术在传输信号中添加冗余数据以检测和纠正错误。由于其简单性、效率和强大的纠错能力,RS在PAM4 SerDes中被广泛使用。低密度奇偶校验(LDPC):这种更先进的FEC技术使用稀疏奇偶校验矩阵。LDPC可以提供出色的纠错性能,特别是与软输出MLSD结合使用时。, o3 v" l) J' _3 r, o3 V

[/ol]

; Y5 \2 F: J S! w" f7 l% Y224G SerDes的未来

9 o/ l- K x# E G" B( H随着行业向224G SerDes发展,IEEE 802.3df工作组和光互联论坛(OIF)联盟都在关注224G接口的定义。为了实现224G,PAM4的模拟前端带宽增加了2倍,或PAM6增加了1.5倍。这种进步需要具有更高精度和更低噪声的ADC。由于更高的奈奎斯特频率导致额外的损耗,需要更强的均衡,FFE和DFE中需要更多的抽头。* Y6 B% @' x! \' j0 f5 B+ N

% J. m/ ]* k6 G5 f- {. X _

MLSD先进DSP将在224G时为信号质量和传输性能提供显著改进。包括Viterbi算法、DFSE和软输出MLSD在内的MLSD算法可用于提高序列估计的准确性,并减轻噪声、干扰和色散等信道损伤。然而,由于MLSD算法需要大量的处理能力和内存,在选择先进DSP时需要仔细考虑,以在C2M和有线主机应用中在性能、功耗和延迟之间取得平衡。; K3 L: B% ?/ K" ~

. P t& p! B0 V; b+ N结论$ ^" [( x4 \# W) }, V

高速SerDes中均衡技术的演进是由对更高数据速率的需求和克服信道损伤的需要驱动的。从简单的NRZ信号到具有复杂DSP技术的先进PAM4,该领域已经取得了进展。随着向224G SerDes及更高速度发展,先进均衡、CDR、MLSD和FEC技术的集成将在确保扩展距离上的可靠高速数据传输方面发挥关键作用。- m2 N: m2 L n9 H# g$ I+ f

5 ?# v; S- O% R% T! c9 P8 l

参考文献7 r0 A, d4 T0 M7 k2 q$ p. b: {

[1] M. Sanyal, "Evolution Of Equalization Techniques In High-Speed SerDes For Extended Reaches," Semiconductor Engineering, Jul. 20, 2023. [Online]. Available: https://semiengineering.com/evolution-of-equalization-techniques-in-high-speed-serdes-for-extended-reaches/$ ~# K: A$ q* C: [$ B5 v# w

END; {& h% s$ j8 b- j

, U8 y% S% N( m

# L/ h S9 I* W1 R3 ~. H9 e' d) p4 I软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。1 c" p' n3 e# [4 J9 Z- z/ ?6 ?0 i

点击左下角"阅读原文"马上申请, V% r# K t* I/ w, S7 y

8 p. ?1 v& l7 w$ D- K: M# R) ^

欢迎转载; u- T1 q; ^- w3 S8 y

' x" w) i8 m9 }

转载请注明出处,请勿修改内容和删除作者信息!

/ p* \: B# ]2 w L2 q6 U

) v% w$ e& |, Z# O

$ f0 ?, f; \% E5 _+ r0 x5 R6 h- h' W" a* f# A! J+ I A+ N

p21pr105n5o64090411253.gif

/ O0 u2 f* T: z% C2 }: g, u9 X' g; J b/ \

关注我们

1 V# n! E; k& L. z/ @7 ~! ~" E- k. b5 L# E G

5 d, Y: `4 t0 [: S3 X: A

qe15hno3t4y64090411353.png

% r0 E A: B- F4 {8 o4 s | 7 P1 w* X& g1 C! k H

1pcspdmf4ms64090411453.png

; n0 Y# V5 S( d3 `# j

; n0 Y# V5 S( d3 `# j

|

8 G. O0 p1 G' b: p% `7 l% [

q4uch52k5hw64090411553.png

. `) R# a: Z( {8 M |

4 }# B0 N! p* |5 O9 @! @% r: D2 K1 B! e* G1 [% f, M A

' X0 Y I6 Y8 Q3 e y! @; O( n8 X- c0 y3 n" z

关于我们:5 G+ V- Y; G7 \. u$ V7 w/ I

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。; P0 o% d/ V: t# u

% |7 y6 Q8 ]+ j- y( [

http://www.latitudeda.com/

8 V7 H" u2 i6 ^6 L9 i+ H(点击上方名片关注我们,发现更多精彩内容) |