|

|

引言9 U" \: h. q! l. _

; v' `* C7 v: i

随着人工智能领域的快速发展,处理器架构正在经历重大变革。进入2024年下半年,芯片设计的重点已从单纯追求速度转向在性能和效率之间取得微妙平衡。本文介绍AI处理器设计的最新趋势,重点介绍领先芯片制造商为应对可持续计算和异构集成挑战所采取的创新方法[1]。" u; ]+ T: h2 r+ M$ I

9 b4 k. P3 K7 I/ ^可持续AI计算的需求

# `3 j, K/ y3 p( V大型语言模型的爆炸性增长给数据中心和电网带来了压力。政府机构和公用事业公司越来越关注处理这些庞大AI模型所需的能源消耗。因此,芯片制造商被迫重新思考AI处理器设计方法,从"尽可能快的芯片"心态转向更平衡和可持续的策略。4 w. \$ W: m5 z- i% d" i

9 l' f9 y% `, f4 P

fuqoqwkd12s64090412459.png

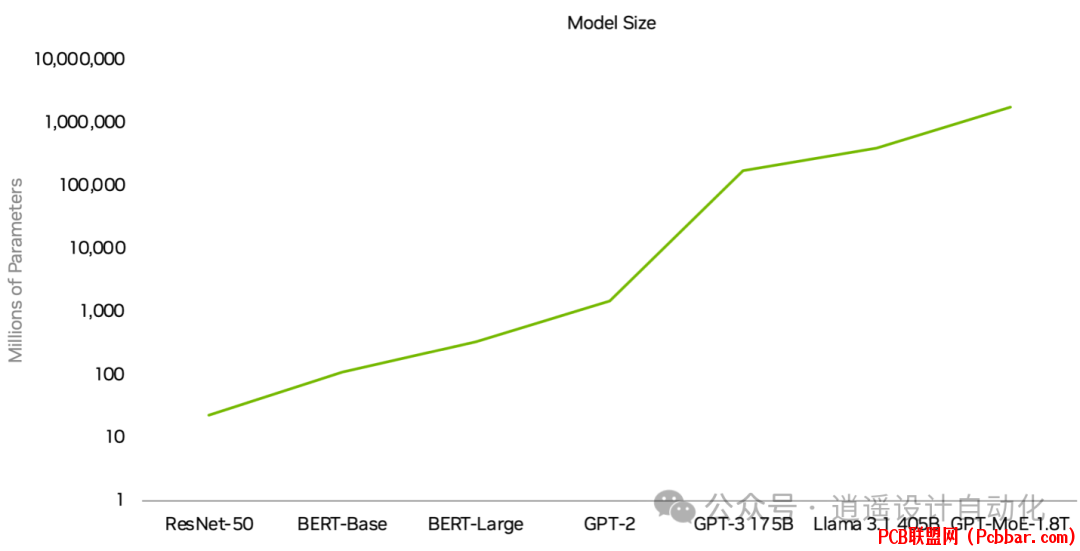

9 N' L# ] H, V, b& r图1:AI模型在十年间的指数级增长,显示模型规模和复杂度增加了70,000倍。

- q+ \# O$ r( Y; S" L" t# t, u* M* B8 |1 \

上图展示了过去十年AI模型规模的惊人增长。随着模型变得越来越复杂,具有数百万甚至数十亿参数,计算需求已经飙升。这一趋势清楚地表明,简单地扩展现有架构不再是可行的解决方案。1 t' k7 c8 @; J3 j8 z @# \/ X5 f) d

+ Z6 ^. i" a2 `( Y p8 k+ y

AI处理器设计的关键趋势5 K' S% p# W! Y2 g' ?

1. 异构集成

# v; Y: j- \& i. z" |" o+ O- f$ bAI处理器设计最显著的转变之一是向异构集成的转移。这种方法涉及在单个封装中结合不同类型的专用处理元素,通常使用2.5D和3.5D集成等先进封装技术。

$ L7 L, ^) n+ N! j( S% b+ a8 T# `

9 \0 k, E0 \; }1 l3 S# I芯片制造商正在利用Chiplet技术创建更可定制和高效的设计。通过将单一芯片分解成更小、更专业的组件,制造商可以针对特定工作负载和数据类型优化每个元素。这种方法不仅提高了每瓦性能,还允许更灵活地应对多样化的AI任务。: e. a* g6 R7 q3 y _8 u0 D" u

) a: D9 N5 s8 }8 b9 @9 L2. 智能数据管理

4 T; x) ?8 a3 E( B) i数据管理已成为现代AI处理器设计的核心焦点。考虑到训练和推理涉及的大量数据,高效的数据移动和存储对性能和能源效率都至关重要。: q1 B" N" o, y; y/ I

: V9 R) N' i# W2 t* X; U& }# U) k处理器现在包含复杂的数据管理系统,包括:

' h# @) Y3 ]7 b$ l/ w3 O7 y5 t0 g智能缓存策略片上暂存器用于临时数据存储统一内存架构近内存计算能力, H9 P" `/ [" P- { W0 \ @# C

7 P1 b, Y* k$ l) v* z. l+ |! I这些功能有助于减少数据移动,而数据移动通常是AI计算中最耗能的方面之一。

& ?+ u; {" f6 x+ @# [ y+ A6 } h/ M1 `0 d

3. 专用计算元素' y0 u4 ?* P' W2 n d/ O

AI处理器越来越多地包含各种专用计算元素,每种元素都针对AI工作负载中常见的特定类型操作进行了优化。这些可能包括:- g3 T) T+ w4 Z9 _+ b2 I3 _

矩阵乘法引擎(MME)张量处理核心深度学习核心矢量处理单元

5 r$ G* b9 H' Z! x; O; @, [1 R7 _6 i2 \% \, b

通过提供针对AI算法独特计算模式量身定制的硬件,这些专用单元可以显著提高性能和能源效率。

* @" j- S8 N: j0 g( ?4 U

! P: [! W- _$ j7 P9 O" |4. 先进的内存解决方案4 ?5 X/ u3 e: {$ k- N; k

内存带宽和容量是AI处理器性能的关键因素。最新设计正在整合先进的内存解决方案,如:

: ^# b' n, |, [9 J, N/ O/ S高带宽内存(HBM)封装上内存配置大型片上缓存+ T, A3 ~; F( p' E8 Q% |

# \, H# y* P6 W1 a" I! u6 @这些内存创新有助于缓解瓶颈并减少处理元素与内存之间数据移动的能源成本。

* Y+ s6 V/ v/ _0 F5 r% M

1 }( t/ ^' b# M! ?案例研究:领先的AI处理器设计

2 t, y: P5 F, d, G) T; r% |2 s我们来看看最近Hot Chips 24会议上展示的一些尖端AI处理器设计,看看这些趋势如何在实践中实施。% B- r* N3 r: g1 `" E: w

. W" B9 [1 n5 y! [IBM Telum处理器

$ L% I! ?# m( Z# O- _4 K8 {, B2 z+ f TIBM的Telum处理器展示了从原始性能到效率的转变,即使在高性能大型机系统中也是如此。主要特点包括:8个核心,运行频率为5.5 GHz10个36兆字节的L2缓存新的加速器Chiplet集成数据处理单元(DPU)用于高效I/O处理. T5 e/ n1 A& \, |* ?

[/ol]7 s( _, \3 F. u& y6 X. U

DPU的包含特别值得注意,因为它充当数据的智能交通控制器,将I/O管理的功耗降低了令人印象深刻的70%。

+ p, G! J8 l- x# r% |7 _4 C2 R. T! V& H

2d5ouyamzie64090412559.png

* y" c1 O# @4 G: G/ O

* y" c1 O# @4 G: G/ O

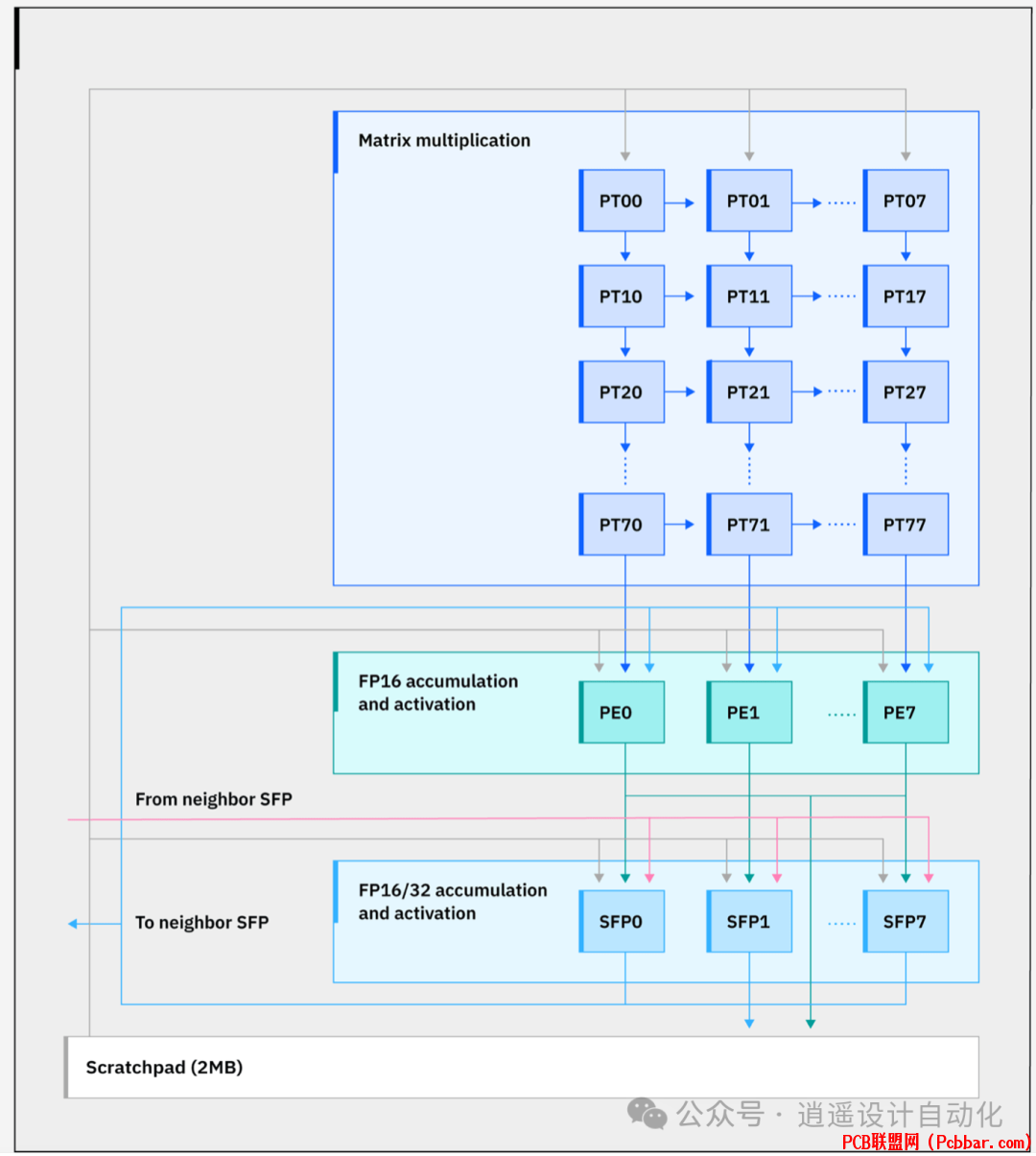

图2:IBM新的Spyre加速器架构,这是Telum处理器设计的一部分。' O# ?( ]' `& _+ s+ ?4 J3 M! q

- ?; {4 p" p9 N5 K: i

Spyre加速器架构展示了IBM在大型机系统中为AI工作负载提供专用硬件的方法。

' h' T. w! o2 p$ p

: d" C2 k3 X$ H" \7 P: z8 K2 Z英特尔Gaudi 32 \" w( v4 N( ?* q

英特尔的Gaudi 3 AI训练加速器芯片展示了向异构集成和专用计算元素的趋势:

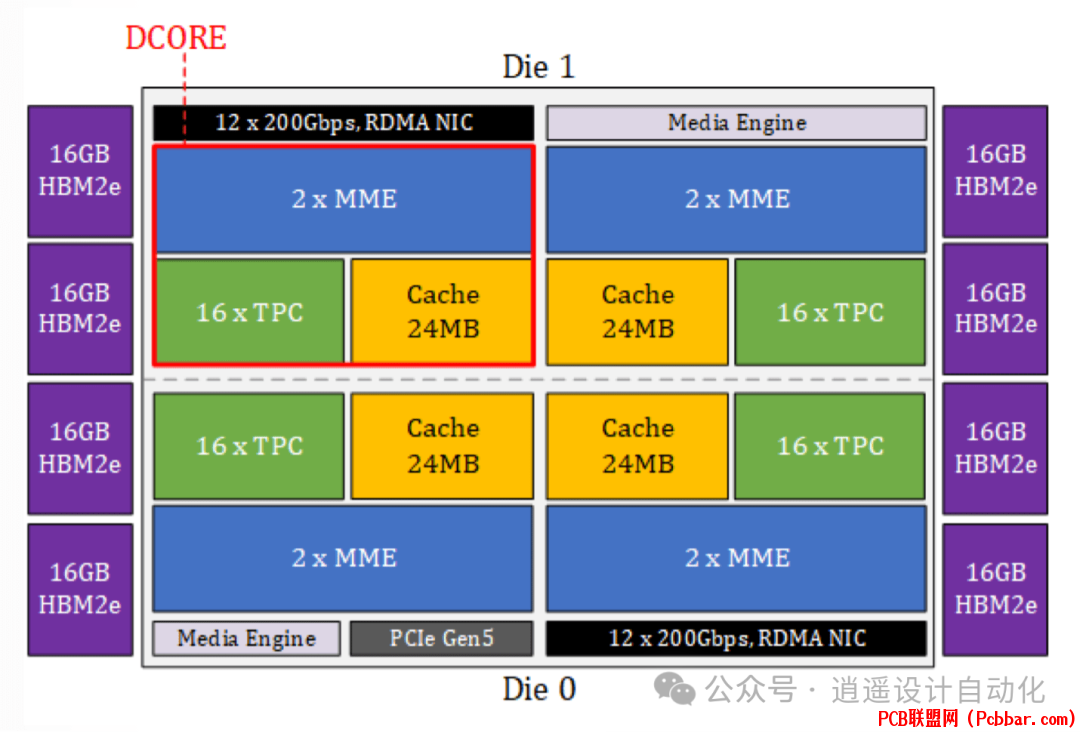

+ K5 j9 j/ p8 H; {. X7 y9 F3 u4个深度学习核心(DCORE)8个HBM2e内存堆栈64个张量处理核心可配置的矩阵乘法引擎统一内存空间,包括L2和L3缓存以及HBM近内存计算能力

/ p S- ^: b' R( k, i9 F, l

* z2 c# N( x/ v+ J

gkucifawczi64090412659.png

/ h# P/ \+ G0 M+ |7 o$ A图3:英特尔Gaudi 3 AI加速器芯片的架构。2 \% X* @* h; w, l; b! ]* f

) v6 {. @+ p% x, wGaudi 3架构展示了英特尔专注于在单个芯片封装中提供各种专用计算元素和高效数据管理。

9 p9 e, Q( U: g5 W' L

# N/ @' X0 d& b& I& F: xAMD MI300X

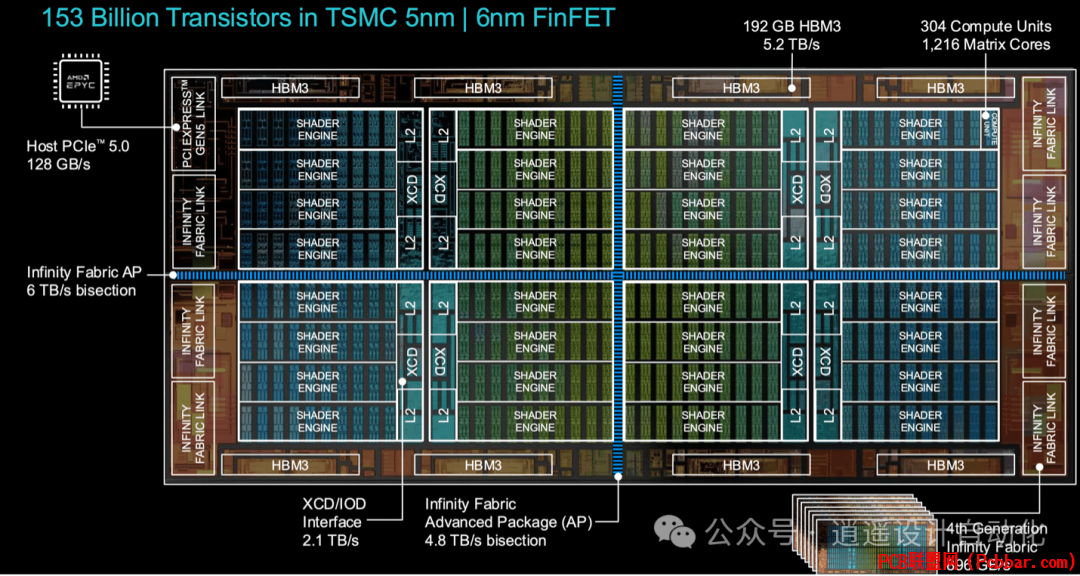

8 O2 M& @ T2 D+ F3 t8 O; ]AMD的MI300X芯片专为大规模AI系统设计,体现了基于Chiplet的方法:6 Q8 [: d) y/ @8 a8 S$ Z

总共12个Chiplet4个I/O裸片8个加速器裸片第四代Infinity架构用于Chiplet间通信HBM3内存提供高带宽

2 m i: q! D5 r3 [! P/ |& I1 Z' p% s3 _# G! q% h

3 A( s9 b% D/ S

nwnmohqewff64090412700.png

* J5 K! n. m' G图4:AMD基于Chiplet的MI300X AI芯片架构。- u# K2 K8 e# b

( ?$ z! n$ U+ N/ w: ]0 z3 {; ~- hMI300X设计展示了如何利用Chiplet技术创建高度集成和可扩展的AI处理器。

+ S# V z! J1 t7 C

" X2 t! M4 J3 x: p- ^9 r; Y8 w边缘AI处理器

3 I/ L0 H$ E2 q1 X1 p! m7 Q虽然很多关注点都集中在数据中心AI上,但边缘计算变得越来越重要。为边缘AI应用设计的处理器必须在性能、功耗效率和尺寸限制之间取得平衡。: [- G) K& I% l9 `0 F! r/ I

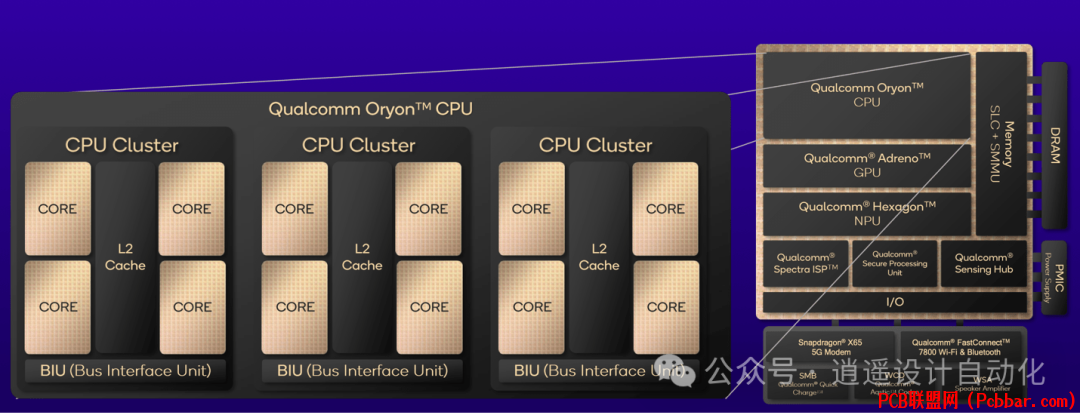

5 T# u1 L- ^; P# y# a3 U4 M0 K+ ~高通的Oryon SoC

0 v( t+ M9 G' |; }/ I6 [高通的Oryon SoC是一个边缘AI处理器的例子,结合了我们讨论过的许多趋势:三个CPU集群,每个包含四个核心两个集群用于性能,一个用于能源效率复杂的微架构,带有8个基本解码器大型统一二级转换缓冲区,用于高效内存管理; b8 I7 k& Y5 @9 V, f2 _

[/ol]0 E8 k6 E0 T0 Z2 f( M4 Q* l

$ n2 c# F* o3 J7 u4 Q7 f& v

ql5szqyrx2m64090412800.png

# H' R, c% i, w( ?2 C1 c0 p

# H' R, c% i, w( ?2 C1 c0 p

图5:高通Oryon SoC架构,强调了边缘AI应用的效率和速度。

8 w) j' X& U/ ~7 h( m* I7 }% t6 Q2 O4 X5 ]: o3 T" x5 a; p m

Oryon SoC展示了如何将异构核心设计和先进的内存管理技术应用于边缘AI处理器。! H' T2 \/ P8 }

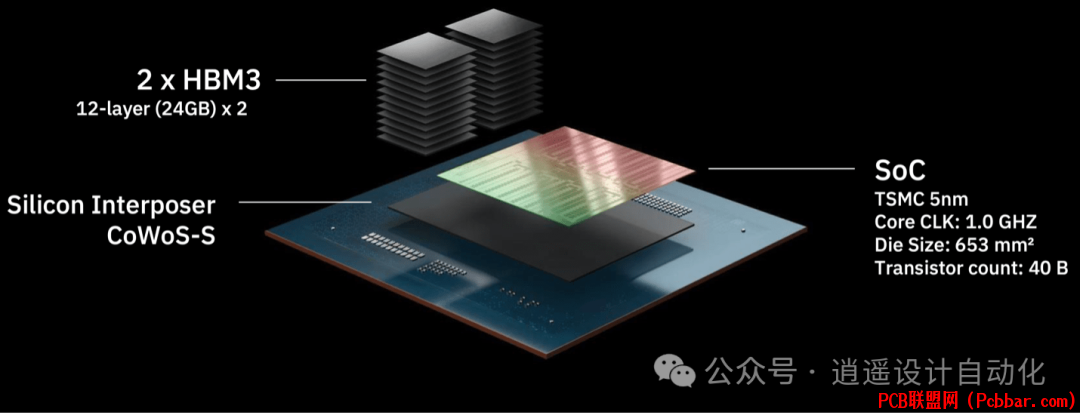

. z' y- l1 G- Z1 t4 {8 q0 G7 XFuriosaAI RNGD: y7 y' T( h6 r( ]& Q8 b% L J' B

韩国初创公司FuriosaAI开发了RNGD(发音为"Renegade")芯片,用于边缘推理:

3 ]& R G3 m# C) v5 T0 ]张量收缩处理器设计1.5 TB/秒的内存带宽两个HBM3堆栈256 MB的SRAM48 GB内存容量

1 c5 X& c. b! x6 ^' p

/ J7 w; G6 F2 g' a3 _5 M! D" D

) }; A9 ]$ O. A) Q6 K- q

feus0hut4i464090412900.png

" ^8 Q& k2 ]: L: H% m

" ^8 Q& k2 ]: L: H% m

图6:FuriosaAI的可持续边缘推理芯片架构RNGD。5 V' A+ f+ q8 i7 E- v$ s7 u: [

$ P* Q5 t9 w5 R0 G/ G* e$ _! ORNGD芯片展示了初创公司如何在边缘AI领域进行创新,专注于推理任务的内存带宽和效率。

0 }- k% \. C; |. t5 j* r) c N

, f- `# L2 D/ u' T& E- O结论

+ l( G) y& b* j7 RAI处理器架构的格局正在快速演变,驱动力是对更可持续和高效计算解决方案的需求。关键趋势包括:

0 y1 K1 `8 _' q3 s" ^使用Chiplet技术的异构集成智能数据管理系统为AI工作负载量身定制的专用计算元素先进的内存解决方案,以提高带宽并减少数据移动

6 ]9 [' |. s+ D: t: E, K: t0 N6 \+ u. G

AI处理器的成功将不仅取决于原始性能,还取决于在速度和能源效率之间取得平衡的能力。这种向可持续AI计算的转变将需要芯片设计的持续创新,以及软件优化和系统级集成的改进。

& V$ u( x0 n$ e p) A4 a

- O% [2 ]3 v+ t& w7 m3 b# _1 c2 v- j我们探讨的来自IBM、英特尔、AMD、高通和FuriosaAI的例子表明,无论是老牌公司还是新入行者都在接受这些趋势。AI继续渗透到我们生活的各个方面,从数据中心到边缘设备,这些架构创新将在塑造人工智能和整个计算领域的未来中发挥关键作用。

* W- D+ w( K+ B5 e

7 q$ Y+ |! `3 a _. ]参考文献

0 m6 F# u. { y. H" A[1] E. Sperling, "New AI Processors Architectures Balance Speed With Efficiency," Semiconductor Engineering, Sep. 4, 2024. [Online]. Available: https://semiengineering.com/new-ai-processors-architectures-balance-speed-with-efficiency/( n8 @: S$ J. R( Q! Q r

END

3 F3 j* I/ v: `8 P( e; G% Z

: {) z0 f: B4 b* S% R3 W3 [" X. e( Y( {, u' f0 n* j' i$ k

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。( K0 W/ i. K$ p/ n

点击左下角"阅读原文"马上申请0 P% I+ e! _4 F& H

/ \% r1 W' p1 s6 s5 g

欢迎转载

$ j0 D& N" j6 B6 A' d! z2 g- X* I$ [- T

转载请注明出处,请勿修改内容和删除作者信息!

$ j9 U( h! P, x9 F/ q% h$ _- n" q% h: P8 S1 Y% t

- Z. `* M6 D2 a

8 d$ l1 y c; m! Z3 W

tstkny3jgab64090413000.gif

# v O0 ]: T) }- _3 C) v" W

6 m5 I8 B( p- o# f9 c关注我们

: n/ y4 H9 a: Y: e! y

) A0 H3 l+ {7 y d- V# ~2 r- V1 ~$ L9 f* Z& | z2 ^8 [5 f

hvscujxequ564090413100.png

5 [, ]7 E- ], l4 ^$ T# }) [' N | * ?6 V* y1 Q% D! j( V2 c

m1o3q4hrem364090413201.png

2 U0 @0 _3 i+ V, L) B' n5 e, T% _ | " a y6 B! M% x5 {( V# Q

5rebgfv1slv64090413301.png

7 n( O- W0 L% Q% E" z( N3 M P |

# ]' x i2 l& K- _% _

7 ]6 g3 ^( v: ]1 v( x+ `4 i% Q( p, l. Y

& e; Q, d4 r( r* p/ K& V

, {! u8 O, T$ c& r

关于我们:

5 F* r. l5 E+ P深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

% y+ x2 M7 r) H, S) O8 z

9 ^# M9 }1 ^5 n. m+ jhttp://www.latitudeda.com/; ^! y/ J. _" k3 H' ?% `

(点击上方名片关注我们,发现更多精彩内容) |

|