|

qopaujsur4r640115517222.gif

: x7 _- o) L& m6 d3 b1 v1 x% c8 W. z点击上方蓝色字体,关注我们% r" t8 s5 W. ` W ?: v# [2 w

来源于小伙伴提问。, f; ^4 A- V6 ^- f

! ?3 w' y3 E' J! |9 {+ U4 m, y

ir5vezrizbo640115517323.png

2 x8 R3 J! u: l# O' V/ C2 W

2 x8 R3 J! u: l# O' V/ C2 W

8 i$ o/ m3 `" ?# E

3akerz5ndyn640115517423.jpg

6 [' D& A: p* w6 `! A

6 [' D& A: p* w6 `! A

9 t! c# {9 _- O9 F5 ~

spffaewpt0q640115517523.jpg

$ c! y, i& d8 @( d* P; w

$ c! y, i& d8 @( d* P; w

% {% ^/ t8 r( c" C* f以下是我的一些看法。! @" g# X t) O' Q$ c0 L

7 S! G2 @+ p; P- ]

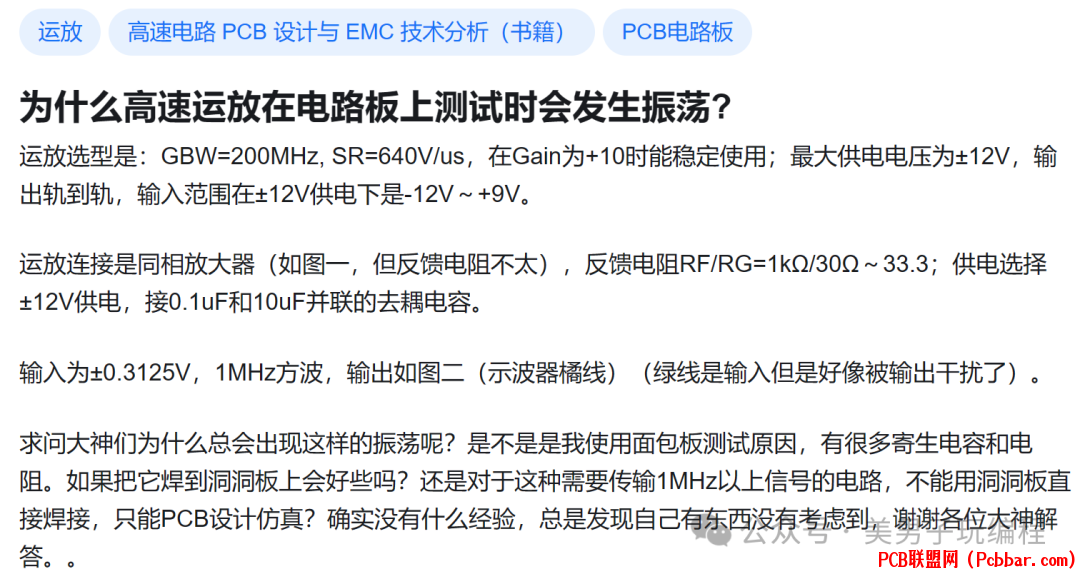

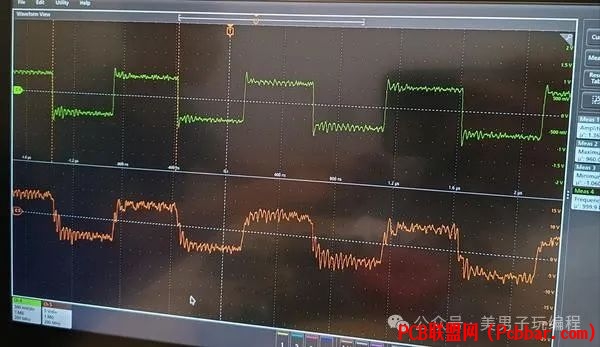

高速运放电路对电路板设计要求极高,在面包板上测试确实难以获得理想效果。

0 {% t( I% b/ a% C7 d* [# b! b }; o

对于传输1MHz以上信号的电路,建议使用pcb设计并进行仿真,以确保信号的完整性和电路的稳定性。

! k2 H% o y. l! S

& c4 S* \' ? l: v* b* q) t& E, K

bmjvweewakv640115517624.png

7 i) V# P) z( |: m* m8 g

/ W, s2 ^+ e1 g8 c# p2 k1

E g' j; m) y( t8 G/ c* k( p' C寄生电容和电感1 j* f, ?4 c: ~8 O/ i8 v

面包板会引入较大的寄生电容(通常几皮法范围)以及寄生电感,高速运放(如AD8067)对这些寄生参数非常敏感,特别是在1MHz以上的信号情况下。

% \' `8 L- e* Y: x

" B7 m( u2 o+ `' l c这些寄生效应会影响信号的相位,使得反馈网络不稳定,从而导致振荡。

" Z) E8 l$ f2 O6 z& R; L5 q: H. z$ V5 }' W, v; k

即便是洞洞板,虽然比面包板稍好,但也无法完全消除这些寄生效应。

, w# V0 S; D3 @9 D4 I1 Y& |22 C# Y# u* { }$ T" H, o2 U

布线布局# D# a% _% Z0 C4 a' G/ C0 {# Y

高速运放电路对布线布局要求很高,任何走线长度、走线方式、地平面设计都会影响稳定性。6 m8 z& S, k. V! a

( x6 m% |9 a2 _+ `" t在面包板和洞洞板上,走线无序、长短不一,这些因素都可能使运放自激振荡。7 V9 ^" f) }1 a8 J! v7 F2 ~4 o+ ~

& H* d% {* a2 d' z* y/ L4 j

而在PCB上可以专门设计短而粗的走线和低阻抗的接地来减少这种影响。

0 ^, H( @9 ^/ a: U4 N3 i6 ^$ P3

& N3 V/ t9 O( A' |3 \, `' `电源去耦

# m; D# [7 W; {+ P5 z* [& J4 j虽然你在电源端加了0.1μF和10μF的去耦电容,但在面包板和洞洞板上,电容可能距离芯片较远,无法有效去除高频干扰。

0 G4 C" v7 V1 Y. ]: J9 Y# t4 L3 ]$ `2 ?2 s: w8 }/ I, }8 S

在高速运放应用中,去耦电容需要尽量靠近运放电源引脚,以确保稳定的电源供电,否则会引起不必要的振荡。 J4 X. W/ X8 L R, H0 l. S8 t* ]9 t

4

3 x- |2 ^& `' J5 y4 g: W2 T反馈网络设计7 j0 V* j+ H( f8 \/ R( E* _

你的反馈电阻为1kΩ/30Ω(增益约为10),在高速运放中,较大的反馈电阻可能会和寄生电容共同作用形成相移网络,导致不稳定。

2 X2 Y( ]) n/ Y8 B& C: T+ F7 D" J/ [- J s% l5 n6 e7 ^

可以尝试减小反馈电阻值,同时适当调整增益,以找到更稳定的工作点。' `* \* J3 y, P H9 m9 D5 {8 f4 O' E, O

54 R1 p W$ m( J( P# k

信号干扰0 w) k: x2 n! X P/ {2 T0 z7 _) W. e

你的输入信号(1MHz方波)在这种环境下很容易受到输出信号的耦合干扰,尤其是在面包板上没有明确的地平面设计。

5 Q2 `: v+ R& l4 H

1 ^1 P5 R( a% g' Z" j这种干扰会引起反馈信号的失真,加剧振荡问题。

8 Z) l3 S/ Q6 L3 [/ R

6 Z5 M" N7 G! q$ `+ n5 |- _建议如下:! a. M4 A( a7 j

PCB设计:对于高速运放电路,最佳的解决方案是设计专门的PCB,确保布线短小、去耦电容紧邻芯片,合理设计地平面,减少寄生效应。使用贴片电容:如果你尝试在洞洞板上焊接,可以使用贴片电容直接焊在运放的电源引脚旁边,尽量减少去耦电容的引线长度,以提高高频去耦效果。降低频率或改用更低速的运放:如果PCB设计不现实,可以考虑降低工作频率或选择GBW较低的运放,尽量避免高速信号在非理想布局下的寄生效应影响。屏蔽外界干扰:尽量减少输入信号与输出信号的干扰,比如使用屏蔽电缆或隔离输入输出走线。7 ]3 S% d" B, x5 A8 G& P. U

) e! h4 R/ ~( e' l) S

illndoyt5jb640115517724.jpg

! v1 {9 q( u$ f) N

4iry2zuj2mo640115517824.gif

" c# ]1 e6 P( [0 {

" c# ]1 e6 P( [0 {

点击阅读原文,更精彩~ |