|

|

引言( v) J9 C& ?# M8 e* y

反向设计(ID)已成为优化光电子集成芯片(PIC)的有力计算方法。然而,使用传统ID方法设计的器件在制造过程中性能往往会显著降低。本文介绍新方法,称为制造感知反向设计(FAID),将光刻模型集成到优化过程中,以减轻制造引起的性能降低[1]。

, N6 `) f$ K: {/ I* O5 J

uji4b14tl4l6401307250.png

. x% t7 u$ H4 N# N

. x% t7 u$ H4 N# N

0 V2 L% D4 h1 a, I9 H# w8 k

制造引起的性能降低挑战/ ?- }$ }% ~/ m5 T

光子器件制造受各种工艺变化的影响,可能改变器件的理想几何形状。这些变化包括角度圆化、邻近效应、线条缩短和侧壁粗糙度。这些工艺变化对具有小特征尺寸的器件特别有问题,如亚波长光栅(SWG)和拓扑优化器件。5 F7 _* P% U0 Z

- P: u8 I6 L- u! m例如,使用193 nm深紫外(DUV)光刻技术制造的集成布拉格光栅常常经历显著的光刻引起的性能降低。设计的10-40 nm宽的波纹在制造过程中严重圆化,导致实验测得的带宽比设计值更窄。. j9 U, {$ _* z9 h' `! M! Q5 b$ z

3 J g- j6 ]4 l' `

传统反向设计优化器通常根据理想几何形状计算性能指标(FOM),未能考虑制造引起的性能降低。这一限制突显了需要将制造考虑因素纳入优化方法的必要性。. C% k/ ~6 y/ P: K- F5 T2 D

5 e! Y9 \3 b4 Z/ H0 {; u介绍制造感知反向设计(FAID) k' \6 t, U$ D. J+ M3 t

FAID是一种新方法,将光刻模型纳入反向设计过程。通过整合制造引起的工艺变化预测,FAID识别可调整这些变化并减轻性能降低的设计参数。 @# ]) p9 @+ P9 @7 c

dh5pq5mt2i56401307350.png

0 i- @) r0 @# |, \

0 i- @) r0 @# |, \

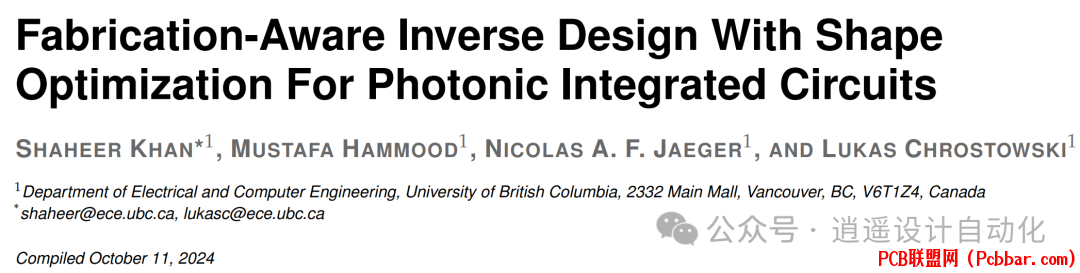

图1:对比标准反向设计与制造感知反向设计中计算形状梯度的数值方法与光刻模型集成的流程图。比较了标准反向设计与制造感知反向设计的工作流程,突出了FAID过程中光刻模型的集成。# s1 R1 K, `7 Z# O

d N2 \1 R- ~& C

FAID工作流程光刻模型集成:FAID利用光刻模型基于光刻预测几何形状而非理想几何形状计算FOM。参数空间转换:FAID不是对设计参数施加约束,而是将参数空间转换为"制造感知"。梯度计算:对于可微分光刻模型,使用伴随方法和光刻预测参数计算灵敏度场。对于不可微分模型,使用有限近似方法计算梯度。优化:优化器识别可减轻光刻模型捕获的确定性工艺变化造成的性能降低的参数。; C5 w4 Q/ s2 ?+ y9 g

[/ol]- z8 Q2 `8 Z7 B. P) }' W. Y

演示FAID:Y分支和SWG到条纹波导转换器

/ n4 Y1 p$ X5 Y; Z0 E9 D" r: ^( h为评估FAID的有效性,选择了两种器件类型:Y分支和亚波长光栅(SWG)到条纹波导转换器。

9 u, _. z- T% D I9 u- y- P* K5 B2 v$ ~: i {1 Z

1. Y分支:

: \2 E' `6 F8 k: {. ]选择Y分支是因为在反向设计研究中广泛使用。虽然应用平滑度惩罚可以减少性能降低,但FAID仍然具有优势。- S, s) W; c) y9 o$ N; p% R$ q

rxmntqfctlw6401307450.png

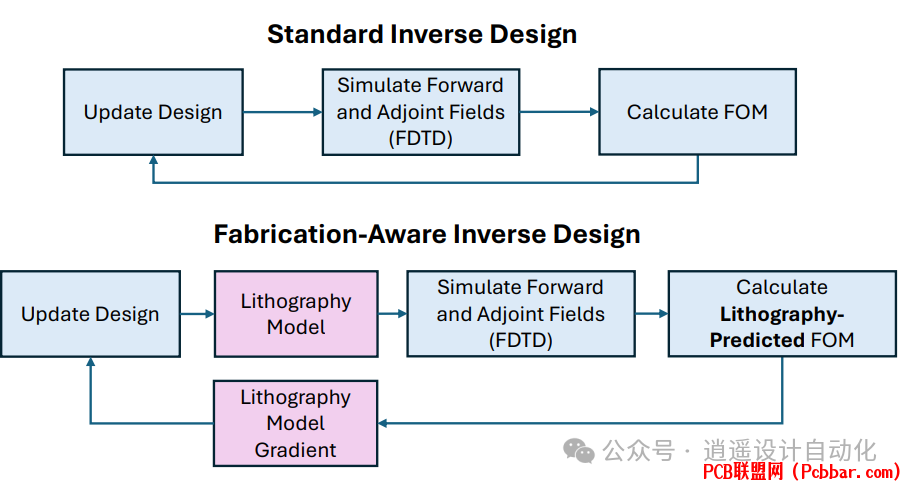

* B& |/ e7 G# X4 b1 _图2:为DUV光刻优化的对称FAID和ID Y分支上半部分比较。说明了FAID如何补偿光刻模型预测的欠蚀刻,并调整Y分支边缘以实现到输出波导的更平滑过渡。 ^/ ?: B; ?6 S' K* T9 R4 Y

& p7 l0 y+ F( B- D: O; i8 K+ n" l2. SWG到条纹波导转换器:

! Q1 d- Z" }9 J+ I$ I% D: d/ H+ T选择SWG到条纹波导转换器是因为其依赖于可达到的最小特征尺寸和较大的参数空间。设计允许单个光栅的宽度和长度以及波导桥的边界变化。

( Q5 {( A4 q8 A( y# d

sqtkdipqjev6401307550.png

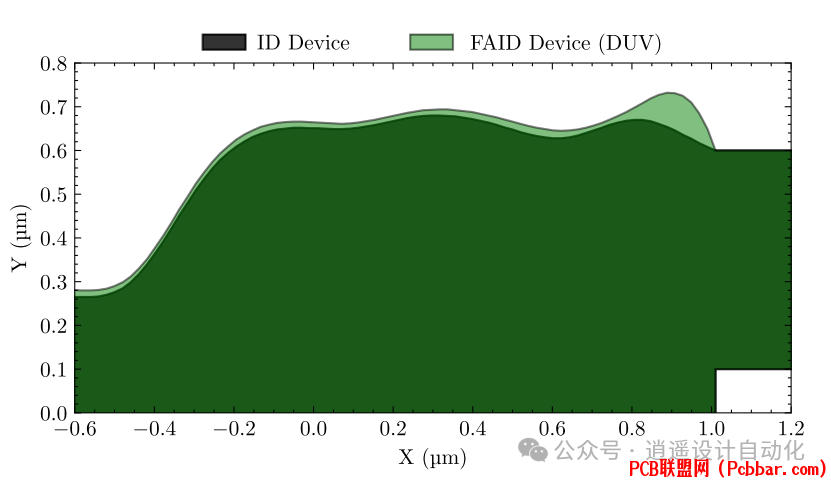

+ J; V! ?2 w' C图3:为DUV光刻优化的FAID和ID SWG到条纹波导转换器比较。显示了FAID为优化DUV光刻的SWG到条纹波导转换器所做的直观调整。# O0 f5 c0 Q6 }; B) r( p

5 S4 \" |- l3 F% {( M; o

优化过程和结果

6 @) n' b" Y' V使用SWG到条纹波导转换器作为示例,比较了标准ID和FAID的优化过程。

9 G9 W5 L0 B0 t2 x9 i# p" U4 T; |

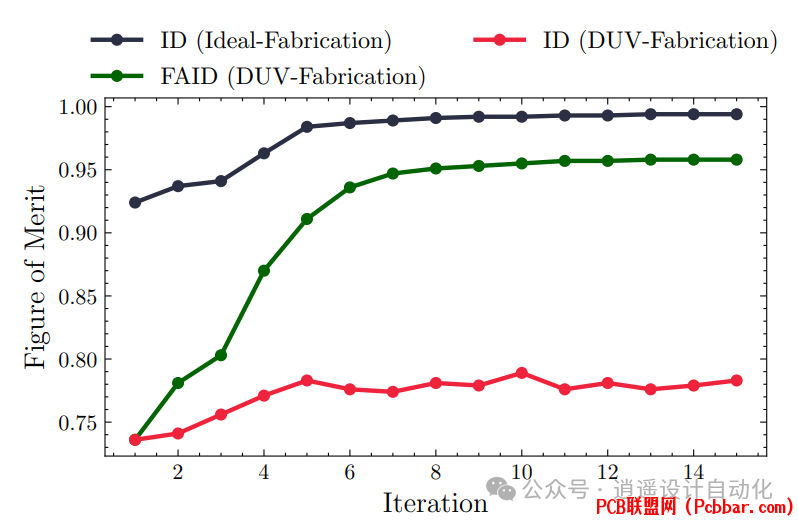

o20uzgatjzb6401307650.png

3 ?: f$ n6 A8 H图4:SWG到条纹波导转换器优化过程中每次迭代的性能指标(FOM)。说明了FAID如何在每次迭代中持续改善性能,最终接近理想ID几何形状的性能。; m/ X& x# \, P+ W0 c

3 Z) ^6 _) Z0 W2 Y+ w. A' X* M" w

优化过程的主要观察结果:

/ D5 c% q; y- W3 |4 H, W标准ID:理想性能(深蓝线)迅速改善,但考虑制造效应时未能转化为性能改善(红线)。FAID:DUV预测的FAID器件(绿线)在每次迭代中都显示持续改善,最终接近理想ID几何形状的性能。

8 B# J9 D/ Y K) `! ~

* B( l2 R; b O, q5 W! t& r3 T模拟结果4 Y% U& @& ? t9 G. f

进行了模拟以比较电子束光刻(EBL)和DUV光刻过程的标准ID和FAID器件性能。) E3 b' `3 K7 g2 c" v5 b

% J! X! u" {3 M: D9 Y

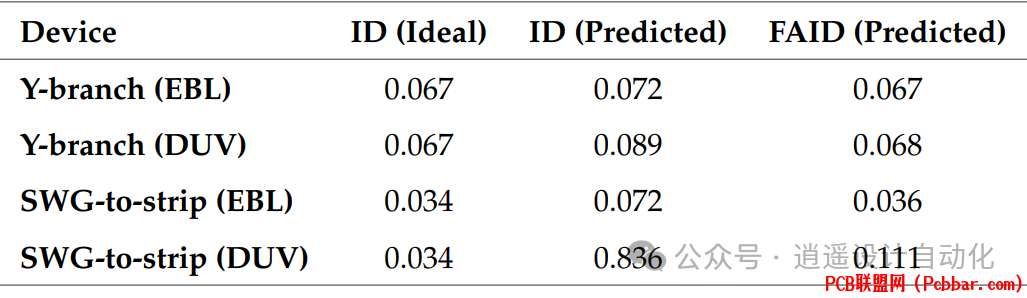

表1数据,描述各种器件在1320 nm处的模拟插入损耗:

0 O% F6 Q% g6 u$ V* f j2 F

eq1wh0weiie6401307750.png

+ j$ D8 Q8 [7 e$ U

3 K& S2 o: W8 m8 I& X4 A2 ?( _模拟的主要发现:考虑制造效应时,标准ID器件显示显著的性能降低,特别是对于具有较小特征尺寸的器件。FAID器件展示了对制造引起的性能降低的实质性缓解。DUV预测的FAID SWG到条纹波导转换器相比DUV预测的ID器件显示出显著的0.7 dB改善。" [4 ~& {+ [" b4 I0 I

[/ol]" v4 o6 _8 J' ^; r) c ^+ C

实验验证( i: {5 u; ]+ F, }

为验证FAID方法,使用EBL制造了器件并进行了测量。通过在EBL制造前对设计应用DUV光刻模型来模拟DUV制造。

4 |+ w0 ~: w6 _7 _) F0 O* d( f- ^- }* A

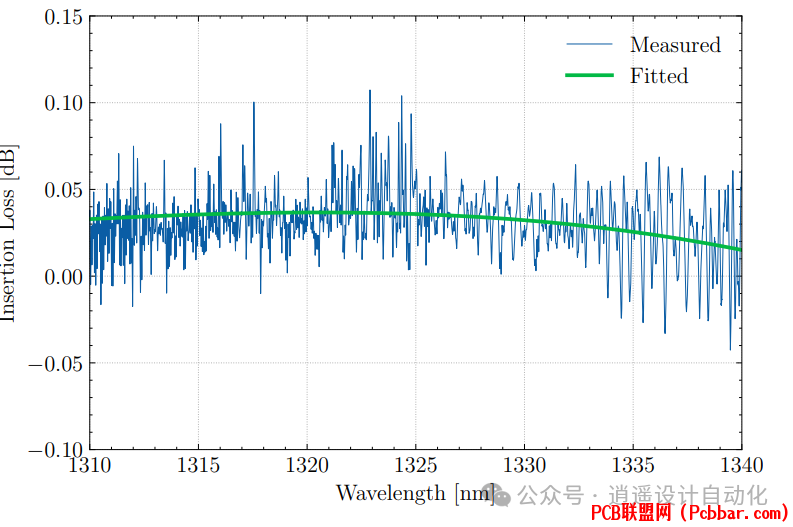

dyokbow3zyt6401307850.png

3 Y$ [: e# } f' O) j" c

3 Y$ [: e# } f' O) j" c

图5:EBL优化的SWG到条纹波导转换器的插入损耗提取。显示了EBL优化的SWG到条纹波导转换器的测量插入损耗,展示了FAID的有效性。' l* `# K5 v5 W& ~

; y/ y2 m! d+ F% K7 I4 l8 W

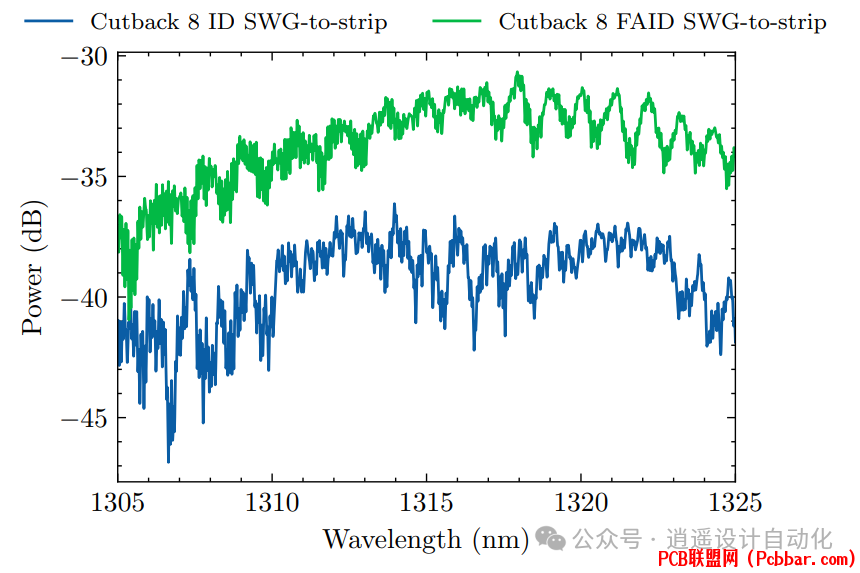

emumvdxlnom6401307951.png

; c! Q8 K) L$ |/ i D/ D图6:显示8个DUV模拟FAID SWG到条纹波导转换器与相同数量ID器件的测量损耗的传输谱。说明了为DUV光刻优化的FAID器件相比标准ID器件的优越性能。) S: d6 E9 s4 u" u9 X, o' X6 g

6 a$ c/ |& g2 J6 m j5 N" q

测量结果0 @1 A6 P* P* Y9 r

实验结果确认了FAID的有效性:在所有情况下,FAID器件的性能均与标准ID器件相当或大大超过。为DUV光刻优化的FAID SWG到条纹波导转换器相比其ID对应物实现了0.61 dB的插入损耗减少。EBL优化的FAID SWG到条纹波导转换器相比先前设计显示出异常低的损耗。即使对于具有相对平滑特征的器件(如Y分支),FAID也显著减少了DUV光刻的预期性能降低。

. G$ p. }/ k+ j+ t[/ol], Z1 z2 P6 v( N3 x2 [

结论和未来方向( K* n. F/ @. i) z

FAID代表了利用反向设计实现可扩展、商业化硅基光电子应用的重要进展。通过将光刻模型集成到优化过程中,FAID有效缓解了制造引起的性能降低,特别是对于DUV光刻。6 E. v' F$ B7 o/ C

7 p) V! _7 L; l

未来工作应关注:/ b3 R2 L! i1 s! f5 N7 ]

将FAID扩展到拓扑优化,解决这些器件极小特征尺寸带来的挑战。使用FAID与光刻模型的不确定性预测进行协同优化,以产生对确定性和概率性工艺变化都具有鲁棒性的器件。: j; t$ c) f8 R) ~; S/ `' c

" g8 S: z; P, E+ u4 Q# Z; o, |( _6 R1 ]6 ]

通过采用FAID,光子设计者可以创建不仅在模拟中表现良好,而且在制造时也能保持性能的器件,缩小了硅基光电子领域理论设计与实际实施之间的差距。

3 H. q6 c3 Q. r) s. x$ ^& J; y0 Y& ~8 B

参考文献

/ W `- s* F, P6 B[1] S. Khan, M. Hammood, N. A. F. Jaeger, and L. Chrostowski, "Fabrication-Aware Inverse Design With Shape Optimization for Photonic Integrated Circuits," arXiv:2410.07353v1 [eess.SY], Oct. 2024.

: _* A" E; o$ ]7 d

$ U0 P5 g' }& K* i0 ^* f4 lEND

" i' R9 _# g: W) t% N3 z3 A+ a

4 U! K' O; S# @! ~

$ @# {! l5 d8 ^: l" ]; n" f软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

& U" f& A% G( }) f0 B9 ]1 t( e' x# A点击左下角"阅读原文"马上申请" y0 q2 K* W1 K4 n2 E

! ^/ x. T4 y) y1 x+ ]

欢迎转载6 b# E( a3 Z6 L' w* M. i" q

8 _+ _ p7 m8 `# L: u转载请注明出处,请勿修改内容和删除作者信息!

4 r; x/ S7 |( H2 m4 O7 `. {) Y

$ O1 K, Y% F% C, N3 y. _2 w- e4 R E5 j6 x

8 ^# I+ D& G( d5 f+ x# k3 {, ~

gv05lk1x00u6401308051.gif

3 a+ b, m: a6 S5 C' G3 m

3 a+ b, m: a6 S5 C' G3 m

: B' f1 q9 Q3 s8 g1 f关注我们, o! S; G! y C" j& w# E

3 w9 R& {. ^. L: A$ s) C0 u6 j" S3 F8 E+ Q J( h

x2d2yvrdfah6401308151.png

) [2 S3 G) K/ d* N8 V3 A

) [2 S3 G) K/ d* N8 V3 A

| % D# e& T4 M; s. t, }

fa5pymjhejo6401308251.png

$ Q. ~8 t* r! I x; m: p

$ Q. ~8 t* r! I x; m: p

| + j3 d- \+ s) d$ ^* y* q

0xl1c5kr0gs6401308351.png

& S' X/ `2 Y7 Y4 J3 R0 e

& S' X/ `2 Y7 Y4 J3 R0 e

|

% S2 d5 x# V; L% _* C1 {3 R0 p' n; h" X# m% |1 N

) ?4 Z& c R6 P* C# F

8 L0 x5 d; R/ Q5 n. y+ v; J& w关于我们:* X& n3 \( Q4 G5 g3 f& j( S

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

* ^; ?+ g! F v, b

! V( F7 [/ v- _+ F& T4 g( ?% @3 r5 [. M& ahttp://www.latitudeda.com/

2 x9 }" S N7 y3 ^) p# b(点击上方名片关注我们,发现更多精彩内容) |

|