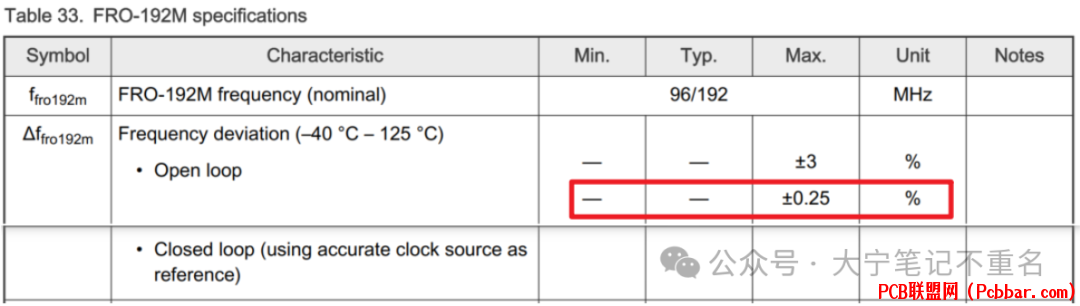

0. 背景 在嵌入式通讯过程中,时钟源精度会影响到数据帧的发送和接收时间的准确性,如果存在较大的偏差可能会导致通信错误。曾在串口通讯到底有没有累积误差及对时钟精度的要求>>一文中探讨过串口通讯对时钟精度的要求。 CAN通讯同样面临着同样的问题,日常实践中通常会选择使用外部晶振或由其产生的PLL作为时钟源(通常外部时钟精度在10-50ppm之间),那内部时钟能否使用呢?最近遇到一个Case芯片内部晶振可以做到全温度范围内0.25%, 对应2500ppm,远远低于外部晶振的精度,那到底能否使用呢?

网上很多资料都只提到CAN对时钟精度很重要,但具体时钟精度要求是多少很难找到一个具体的结论(多少精度容差可以满足稳定通讯要求)和估算依据,在同事引荐下看到一篇20年前的应用笔记AN1798,该文档针对于不同的速度给出了时钟精度要求的计算过程和结论,美中不足的是其仅对Classic CAN做了分析,没有针对CANFD做具体探讨,但是思路基本一致,下面是对该文档的翻译整理。

tqjx1bakgrq6401840555.png

1. 引言 CAN是一种串行、异步、多主通信协议,用于连接汽车和工业应用中的电子控制模块。CAN协议的一个特点是位速率、位采样点和每Bit的样本数量都是可编程的。这为系统工程师提供了优化网络性能的机会,以适应特定应用。本文考察了Bit定时参数、参考振荡器容差以及系统中各种信号传播延迟之间的关系和约束。

2. CAN Bit位定时概述 2.1 CAN Bit位结构CAN的标称频率如下公式,t_nbt对应一个标称的bit时间,一个bit分为SYNC_SEG,PROP_SEG,PHASE_SEG1以及PHASE_SEG2段 。 |