|

|

引言

}3 M; z2 j& M& ^ J/ c4 U! r6 _人工智能(AI)已成为现代技术的基石,推动着各个领域的创新。随着AI模型日益复杂和规模化,对更强大、更高效的计算系统的需求也在不断增加。在这些先进的AI系统中,组件之间的互连性是一个关键方面,尤其是在AI集群中。本文探讨了AI集群中光连接的特殊要求,重点关注下一代AI计算架构的挑战和潜在解决方案[1]。

6 R# L- B' W+ a% v2 v' [

lzyar5xasm264046210415.png

9 P( E9 _: e! e! K, D

9 P( E9 _: e! e! K, D

+ x; W# d! U( A

理解AI计算链路) x/ {& V* ^' T0 D

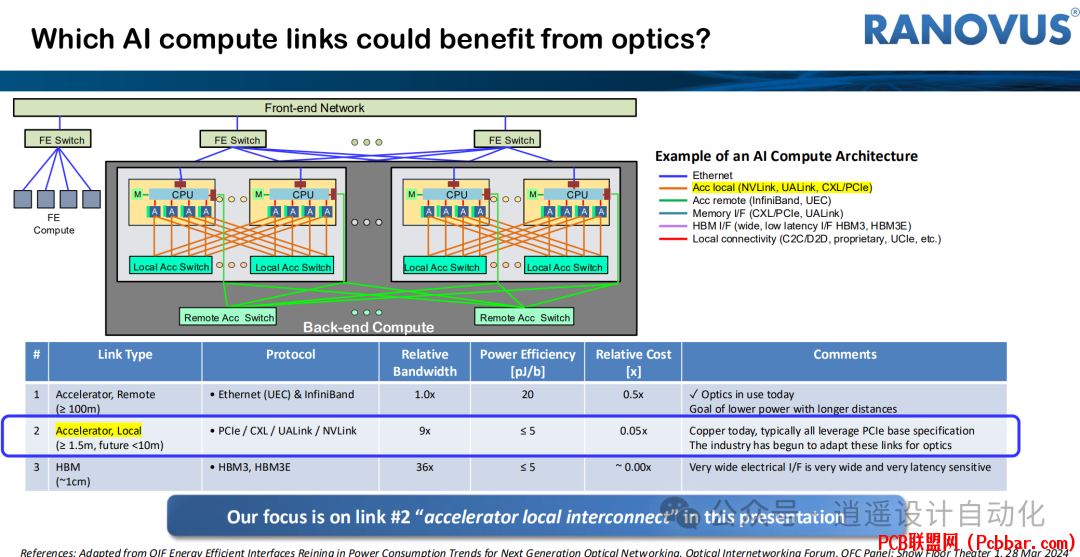

在AI集群中,不同类型的链路连接着系统的各个组件。可以根据功能、距离和性能要求对这些链路进行分类。1 k9 z, y5 V8 v/ Z- i$ N

lfrovmpio1f64046210515.png

. D, [6 @2 K9 [+ E) Q( \8 n

. D, [6 @2 K9 [+ E) Q( \8 n

图1展示了AI计算架构的示例,突出显示了不同类型的链路,包括前端网络、后端计算和本地加速器互连。

4 j( E: F- _2 k& @. ?

4 i% \7 f/ J4 f2 ^AI集群中的关键链路包括:

- M' z( j; M. h5 _" C, n5 m. t n1. 远程加速器链路:这些连接跨越100米或更长的距离,通常使用以太网(UEC)或InfiniBand协议。由于涉及的距离较长,已经在使用光技术。

, X% [, T) g4 Z3 _3 T2. 本地加速器链路:覆盖1.5米或更长的距离(未来可能减少到10米以下),目前使用PCIe、CXL、UALink或NVLink等协议。主要基于铜线,但正在开始向光解决方案过渡。

5 [7 W( t7 S; {3 E! r9 c7 R3. 高带宽内存(HBM)链路:这些是非常短距离的连接(约1厘米),使用HBM3或HBM3E等协议。需要极宽的接口,对延迟非常敏感。. I! R7 \- a" O% z! F% i

0 i) A2 j! g+ U0 V) H

本地加速器链路:创新的焦点% }, c$ C- s9 a S

本文主要关注本地加速器链路,因为在AI集群中,这些链路呈现出独特的挑战和改进机会。

9 c+ M+ q; y5 f/ ]4 E3 k3 I! @9 a/ h2 q' f! d0 o7 _) R

本地加速器链路的现状

- {3 M% j8 r8 j/ N s& V

jmhhmfyhsrf64046210616.png

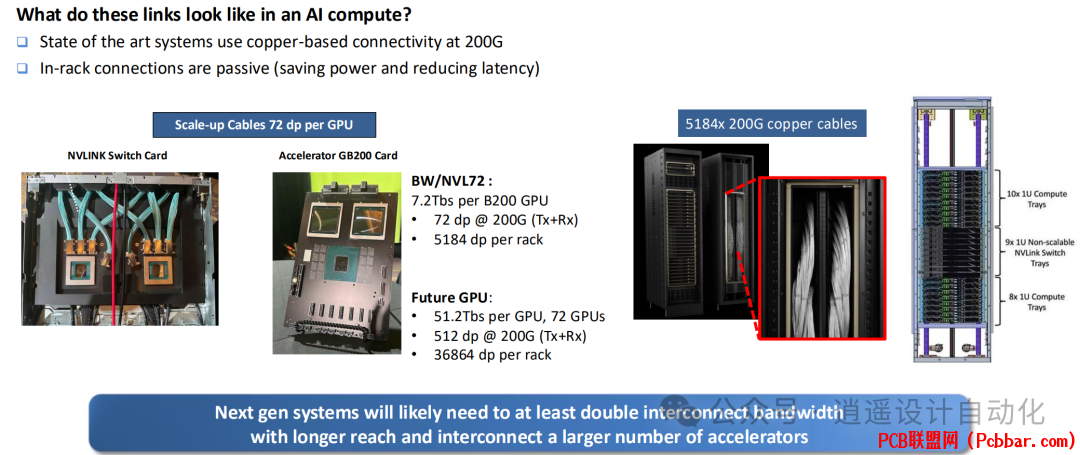

$ y/ T' T( U; W; L+ }图2描绘了当前最先进的系统,使用200G的铜基连接,显示了扩展电缆和NVLINK交换卡。

" ]8 e& c% c% {3 u8 ~5 V4 T# O1 S0 a {) T) R, E

最先进的AI系统目前在本地加速器链路中采用200G的铜基连接。机架内连接是无源的,有助于降低功耗和延迟。然而,随着AI系统的不断发展,需要至少将互连带宽翻倍,同时延长传输距离并连接更多的加速器。

w. f0 k6 _# Q7 D

: g/ a( h# q- f0 M* L例如,当前系统可能具有:0 E' c) H2 ?" z* V- M, J

每个GPU 72个数据路径每个GPU 7.2 Tbps带宽每个机架5,184个数据路径

( k, m; G" M5 P4 C- H$ ~; r8 D2 Z1 |+ b- U: q

未来的GPU预计需要:

: c1 x+ B2 ~ |每个GPU 51.2 Tbps每个系统72个GPU每个GPU 512个数据路径,速率为200G(发送和接收)每个机架36,864个数据路径

; K% F4 q( {0 W/ t% ?, m! Q2 ]9 \4 U' l! D1 j R* `

这种带宽和连接需求的显著增加对铜基解决方案构成了挑战,可能难以高效满足。

$ f$ L& Q4 R& S T7 O9 }) q: i5 u+ A' W/ k

本地加速器链路的特殊特性; x8 X% s2 `6 r1 l4 I' b) l

本地加速器链路具有独特的特性,使其区别于AI集群中的其他类型连接:

- T4 G( l6 C6 y$ b% F! E1 S6 v9 j) |0 m% w m

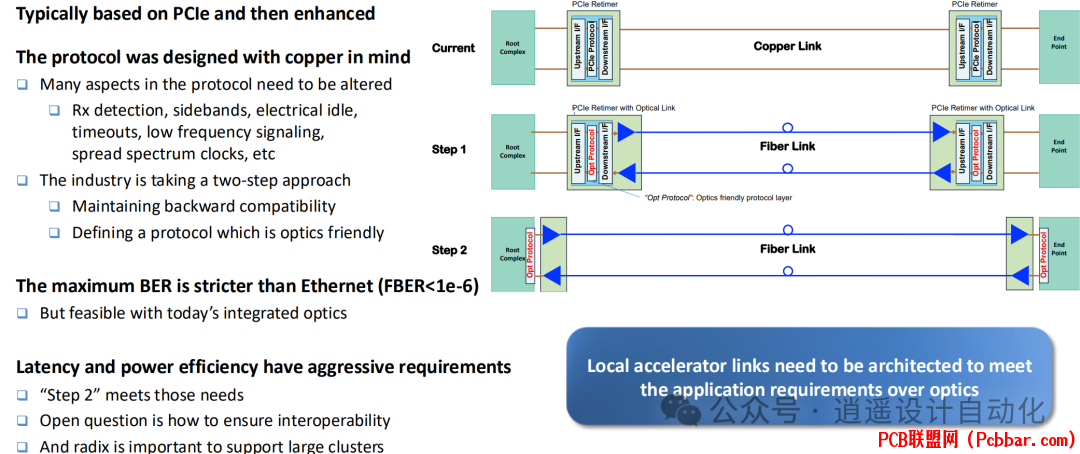

5 }/ }1 ?- h2 a, X, E1. 协议适应:大多数本地加速器链路基于PCIe协议,该协议最初是为铜连接设计的。将此协议适应光链路需要解决几个挑战:" x9 g# P- z- N1 n g

修改接收器检测、侧带、电气空闲、超时、低频信号和扩频时钟等方面。! F7 `4 Q* X( E3 F

业界采取两步法:首先保持向后兼容性,然后定义一个适合光的协议。

. S& J2 p6 m6 `5 h5 `- D7 w3 E+ ?

. m; ~ Y( N4 E9 @0 D3 q2. 更严格的比特错误率(BER)要求:本地加速器链路要求最大帧错误率(FBER)小于1e-6,比典型的以太网要求更严格。然而,这可以通过当今的集成光技术实现。

: o4 c. r+ _. |, s' ~4 ~4 p

) r9 p" _; y1 y' y% ` ]% A) R% C6 b3. 严格的延迟和功耗效率目标:这些链路需要满足非常苛刻的延迟和功耗效率要求。前面提到的"第二步"协议旨在解决这些需求。9 X; z k/ y1 W/ z$ h+ d' @; U. {

0 x; c& O: x9 t, S- T4. 互操作性和可扩展性:确保不同组件之间的互操作性以及支持具有高基数(端口数)的大型集群很重要。

/ E8 I1 v) d8 b% f" ^0 I0 S6 u

4xosdnfmhvq64046210716.png

- U u0 g) w$ ~6 K2 n

- U u0 g) w$ ~6 K2 n

图3显示了PCIe协议向光链路演进的过程,说明了当前的铜基方法和两个步骤朝向适合光的协议发展。

' e& k. [0 H- _; w

* Z7 @) K' P, k: w# m3 w3 t/ P硬件可靠性考虑

) b% U( Y2 b m2 e5 u, M1 N可靠性是AI集群设计中的一个关键因素,特别是对于本地加速器互连。业界通常使用Telcordia SR-322标准作为预测可靠性的基础。

1 } b5 ^- F2 R: M; _8 {

2 y6 z2 y7 G3 g7 ?9 @关于硬件可靠性的要点:& m, U$ D& I' {; [

1. 故障率预测:可靠性通常分为三个阶段:早期故障、随机故障和老化故障。重点是在系统运行寿命期间最小化随机故障。' V# o! ]- ]1 G. [" i( I

$ L* X0 K1 g5 [7 X3 y; e" v

& P) l+ F) K; Z3 i7 v' s2. 集成解决方案:高度集成的IC解决方案预计更可靠。这一原则预计也适用于基于硅的光电集成芯片(SI-EPICs)。) Z0 M, N3 {+ a% Q. ?$ J) _2 h

/ [8 n, W, g$ I9 ~) j4 H" \1 y9 F& |# z5 f5 N1 o s2 c- K) {

3. 激光器可靠性:激光器是光系统中的关键组件。激光器的最佳随机故障率约为1 FIT(每十亿器件小时一次故障)。3 k5 U- Z$ ~: r- A+ g

/ T+ w y* k* Q' }

8 j J6 Y: M# d5 f/ ?

4. 集成策略:激光器可以集成在可插拔模块中(如OIF的ELSFP形状因子)以便于更换,或直接集成冗余以实现极低的故障率。

( \; E5 T z) _- O/ f

9 C# H- j9 h( ]- ?1 c, ]0 \" e关键结论是,只有高度集成的光电子解决方案,通常称为光电共封装(CPO),才可能满足AI计算系统本地光互连的严格硬件可靠性要求。1 C6 a; k6 S9 E7 w4 J+ l

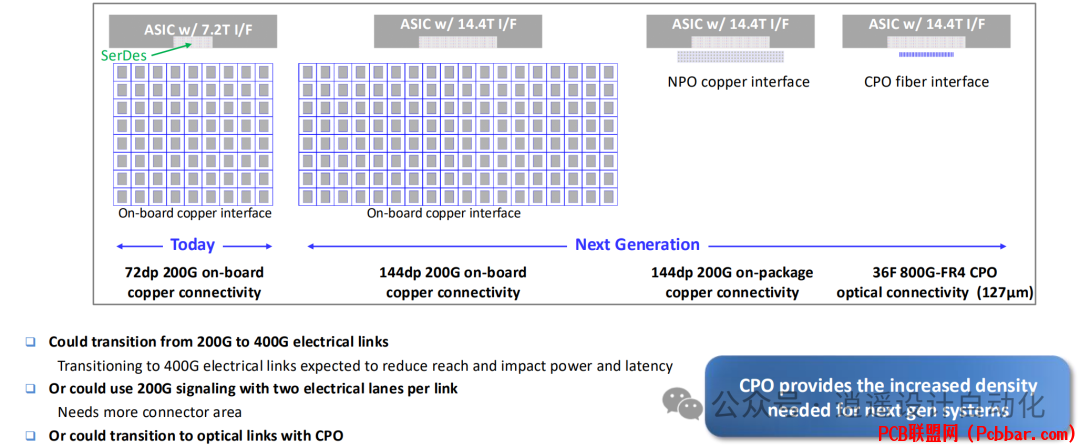

/ q0 P4 C$ Q5 _; u; ?9 Z8 p$ b+ d向更高容量过渡

6 F' e7 F2 |5 ^; p' p: p4 ]随着AI系统对带宽的需求不断增加,有几种潜在的路径可以实现容量翻倍:7 V/ R1 H: k2 W4 o

* o, R" B, H$ G. M8 W2 v( r) P

1 f9 w) D3 D# U5 m- C# H1. 升级到400G电气链路:这种方法涉及从200G转移到400G电气链路。然而,这种转变预计会减少传输距离,并对功耗和延迟产生负面影响。, ?2 O, V9 X' ?

8 i9 _) o- M3 B5 ?, l/ e& @( z4 X. f% C+ q7 E7 A) P9 `" m

2. 双通道200G链路:另一种选择是继续使用200G信号,但每个链路使用两个电气通道。这种方法需要更多的连接器面积,在密集封装的系统中可能成为限制因素。

; T9 s) [# l& C9 h9 s

! v" @ e8 m6 k/ e9 t( M1 i5 u" U3 _3 b7 [

3. 过渡到使用CPO的光链路:光电共封装为下一代系统提供了所需的更高密度,是一个有希望的解决方案。1 O q- |; \! L7 b9 o0 B

chfeln5c2bt64046210816.png

- l4 p# b T$ b0 w

- l4 p# b T$ b0 w

图4说明了从当前200G板载铜连接到未来解决方案的过渡可能性,包括CPO光纤接口。+ m: E, B: V" e9 s

6 y& M% Q1 Z4 i' q/ [0 V! ^比较解决方案:CPO vs 铜

* q! v: k9 [8 h7 x9 B在比较光电共封装(CPO)解决方案与传统铜缆解决方案时,需要考虑几个关键因素:7 @) F- c7 L, z+ @. x& A

" w) @8 q+ u* c. X0 p/ d$ ~( g7 r+ O7 X; |* x5 {4 P. n4 d; u

1. 密度:

, }9 X+ |5 }7 T铜解决方案目前限于2D排列,通道间距为400微米。硅基光电子可以实现3D排列,通道间距小于50微米,使互连密度潜在地比铜高8倍。光电子技术还允许通过CWDM/DWDM等技术在每根光纤中传输多个通道,而铜线限于每根线一个通道。

: h& g1 b$ U d/ a; v+ o. ]* ~2 Q5 r* I, b( a2 L

2. 传输距离:

* Q8 }/ y7 b8 ~& ^, j铜链路在200 Gbps时限制在约1米,在400 Gbps时更短(约0.7米)。硅基光电子可以在800 Gbps的速率下实现高达500米的传输距离。& R4 T: u+ g, C' h$ w

" A9 |: p( q2 ^: ~

3. 机械和热挑战:

/ V9 n. }8 q0 H- p& ?铜解决方案通常需要垂直逃逸布线,可能限制散热器面积。铜缆通常更硬更厚,使安装和维护更具挑战性。

" H3 ]% f/ g( g

8 k& F9 T: H1 ^9 t* v' b4 o$ b

apid12vokew64046210916.png

8 s; ^' w7 Q, z# ?9 z2 S- m( J7 D

8 s; ^' w7 Q, z# ?9 z2 S- m( J7 D

图5展示了铜缆解决方案与CPO的比较,突出显示了在传输距离、密度和能源效率方面的差异。

/ d, g7 s3 v" M. G4 }! N5 ^9 n2 O# ^$ X. Z4 C$ i

结论( ] {* ^" ]% c# K& U D

随着AI集群继续增加复杂性和规模,互连技术面临的需求变得越来越具有挑战性。传统的铜基解决方案在带宽、密度和能源效率方面正接近极限。光电共封装(CPO)作为一种有希望的解决方案出现,能够满足下一代AI计算系统的严格要求。! H3 L0 j9 o+ u

! q) z$ L' C/ P' @2 [

CPO在传输距离、密度、可靠性和能源效率方面具有显著优势。可以实现最终用户针对未来AI系统所追求的高带宽密度(>1T/mm)和低功耗(

2 W2 d( n) h5 _) @7 d; ~: q; o% {$ a9 b5 q$ L

随着AI行业继续推动计算能力的边界,向光互连的过渡,特别是以CPO的形式,似乎不仅有益,而且必要。这种转变将使更强大、更高效和更可扩展的AI集群成为现实,为下一代人工智能应用和突破奠定基础。" n/ ^* F* b+ H5 k0 o2 e

9 k' } n$ d( M: C% h: [( D参考文献

( i% t2 B! R3 I7 {; B7 d[1] J. Hutchins, "Special Requirements for Optical Connectivity in AI Clusters," LightCounting Webinar, Jul. 30, 2024.& H3 R. ]/ |( f# x+ u3 y0 p

' k) z2 ?. f8 s# G I

END

4 p" Z- o' c7 O5 i/ K9 f% [: g4 n3 C4 @' _4 C& f

c4 v; _+ q n, A: B+ v软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。4 m" E) _0 T- S: D; |3 O0 I6 k

点击左下角"阅读原文"马上申请4 P, `, `9 P% _6 M7 z: n* l

- ]& L# T; G& a

欢迎转载

) x7 H9 Z0 g6 N% O& n! E/ S0 @- v( Q0 l: I

转载请注明出处,请勿修改内容和删除作者信息!

- [+ A2 ]# @3 r" w6 y7 m' H. F

- H8 [3 D: z6 u- [$ c) a4 @* k

, J* a& s# Z e7 a2 `% p$ c

M, v2 J0 w7 |7 L( G7 ]: [( U1 O0 a

k1s0z335ifo64046211016.gif

0 h" I, Q" ?; l) ~ p

0 h" I, Q" ?; l) ~ p

: w" ? ~7 h: p. G9 M8 l关注我们1 C1 w( d1 T1 f1 d: ?: ` p

0 c( E7 K. t# I

6 w5 U- c! L0 U" i! R& h

5ugombznhs064046211116.png

8 i$ J% }; m3 b

8 i$ J% }; m3 b

| + t3 s: p0 {; v9 G& ]) M4 j: Z

ytllk0cvjok64046211216.png

* I# A( ~- ?" h* N7 h. E |

" Y* Z2 G' t. q( D1 b& `

gps5vugazuy64046211316.png

& D0 z. m" ` u# M. u0 }5 v I

& D0 z. m" ` u# M. u0 }5 v I

|

8 g3 Q0 u/ J h

! E! N7 S2 \" {$ R# L/ Y/ \

5 X- x: Q3 F- o& k7 n. r6 D- x

0 S7 q* \9 ^& S

关于我们:

# }8 A3 K" ~1 M' t# a: j深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。; O2 o' ^% G- r( v! }

/ Z: j$ |: o8 V. w# [, L

http://www.latitudeda.com/

" ^, G! G" b1 i5 W( `(点击上方名片关注我们,发现更多精彩内容) |

|