引言6 o1 ]; s C6 C; W$ d9 T% T# r

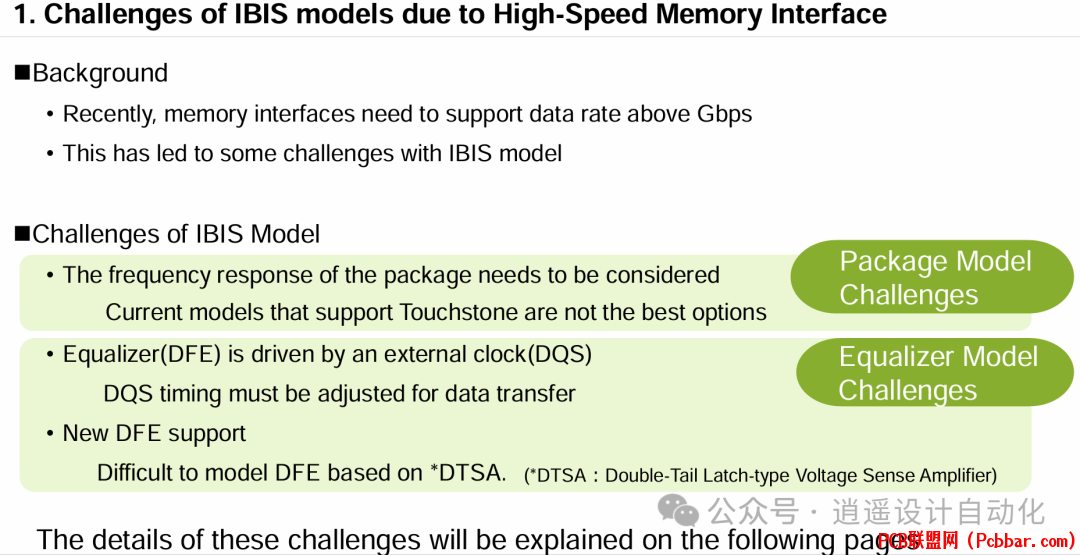

高速存储器接口已发展到支持数千兆比特每秒(Gbps)的数据传输率。这种发展为存储器接口的有效建模带来了多种挑战,特别是在IBIS(输入/输出缓冲信息规范)模型方面。本文探讨了高速存储器接口模型开发中的主要挑战和相应解决方案,重点关注封装建模和均衡器实现。

3 x. v5 q4 k; ^8 U$ |2 f

4ie2r2dniph64084692040.png

1 b# ~. D7 j% c- F! T

1 b# ~. D7 j% c- F! T

图1:展示了高速存储器接口中IBIS模型的主要挑战,突出显示了封装模型和均衡器模型的挑战。

$ E; n. B! f; |# o3 I3 }: q, d" x" |2 T2 p! W0 M

封装模型的挑战与解决方案8 B+ P+ x' X, b; H# D' o7 S' _! g7 j

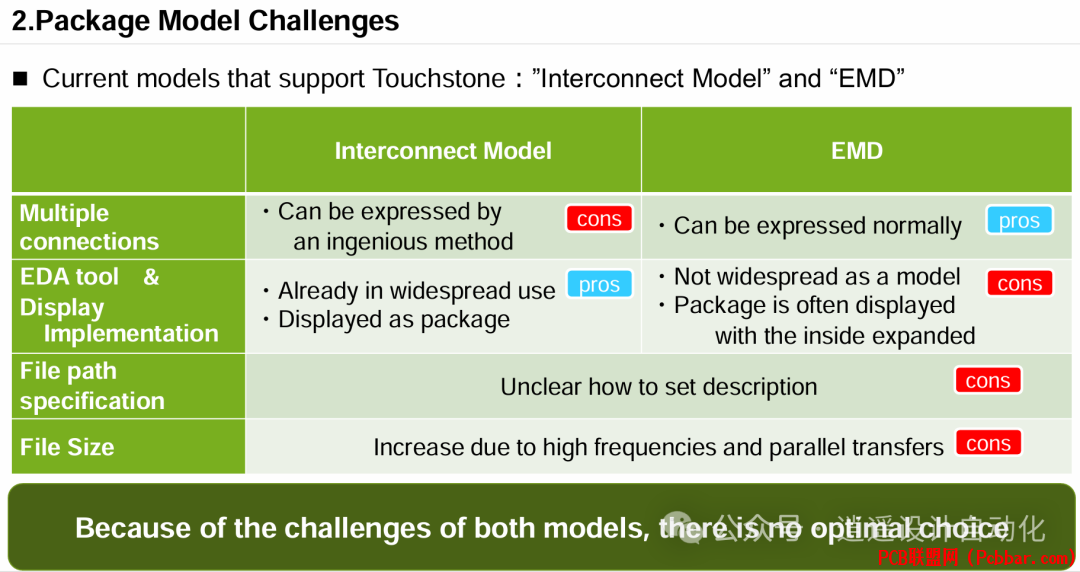

存储器接口日益复杂,在封装建模方面引发了多个挑战。目前支持Touchstone格式的模型主要分为两类:互连模型和EMD(电气模型数据)。每种方法都有各自的优势和局限性,需要仔细权衡。

7 a6 ?) X n6 |% {+ C

gavxpemgrkt64084692140.png

2 z' K# A' e3 w1 z/ i2 D6 B

2 z' K# A' e3 w1 z/ i2 D6 B

图2:互连模型和EMD的比较表,显示了在多重连接、EDA工具支持、显示实现和文件路径规范方面的优势和限制。

9 D. }! v& K; [. g1 O3 G2 W- o6 z; ?2 s4 B& {

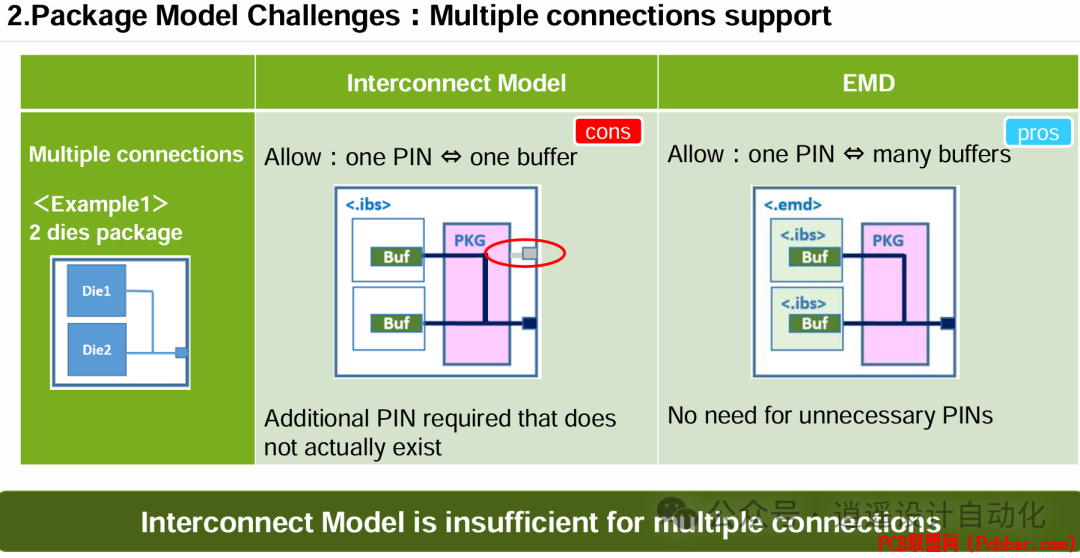

封装建模中的主要挑战之一是有效支持多重连接。这在涉及多芯片封装的情况下尤为明显。虽然互连模型使用广泛,但在处理多重连接方面存在局限性。

: c* t% F* z* y; A; i* h- Y, ~( V

b0oz4jr03bj64084692240.png

: N& O3 o; _( y: |图3:互连模型和EMD在多重连接支持方面的对比图,展示了各自在处理多芯片封装时的优势和局限性。

- i0 z- I, P% A2 F0 i- i8 c4 L E# c/ W4 S. w1 m

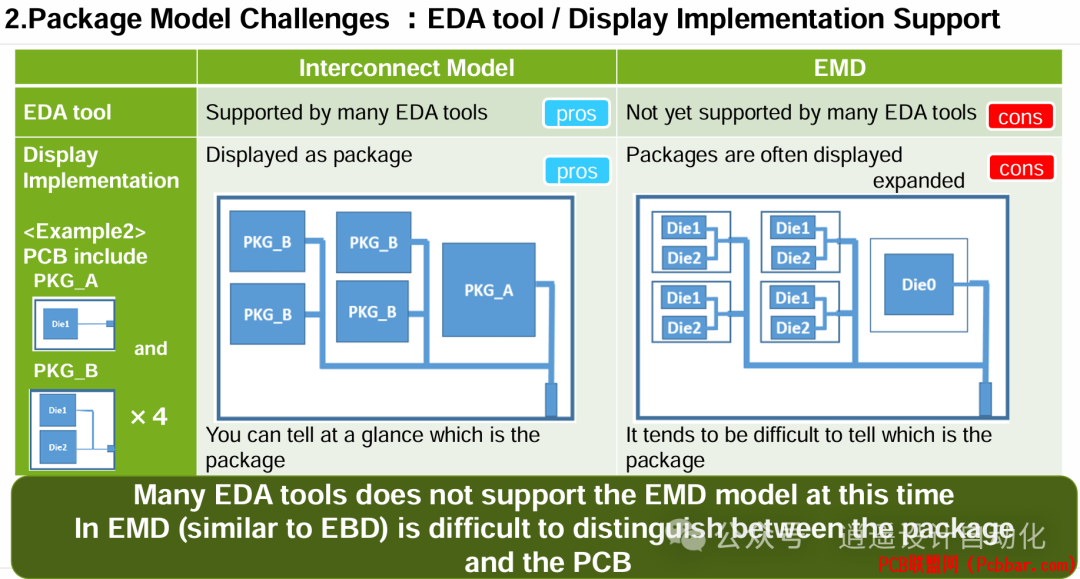

封装模型的实现和可视化也是一个重要挑战。这些模型在EDA工具中的显示和处理方式会显著影响设计过程中的可用性和有效性。, p* r) p/ W/ h* f

5wgctq1otrs64084692341.png

) m# W4 y9 U+ Q: Q$ t' Z1 F2 B图4:互连模型和EMD的显示实现对比,展示了在具有多个封装实例的pcb设计中封装的可视化方式。. Z& k; k U1 r/ a2 ]) {

: X) l U' `1 ?% M0 |: z均衡器模型的挑战

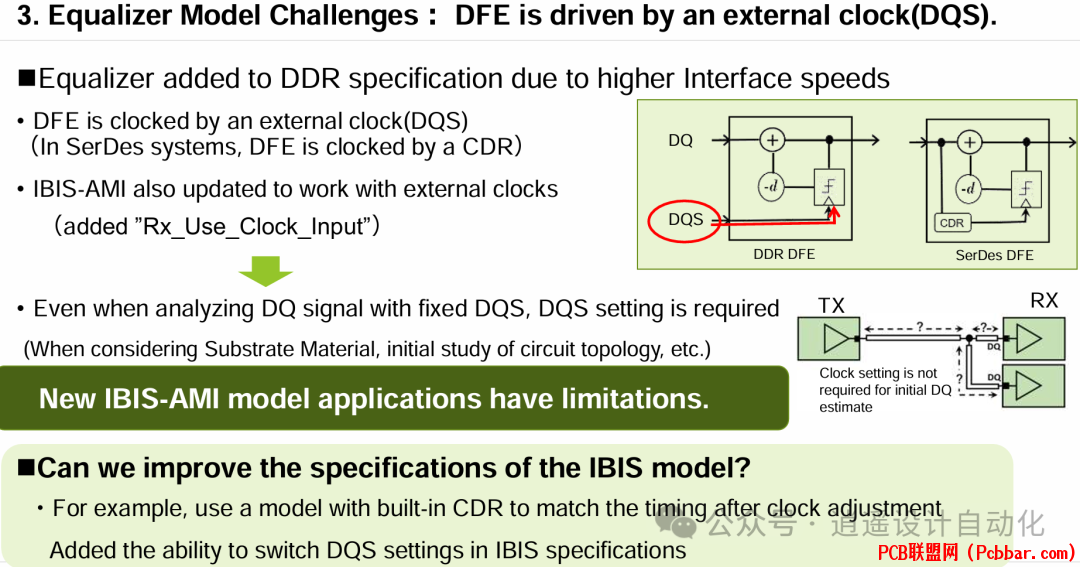

, C9 a% F7 o8 a& L8 iDDR规范中引入均衡器带来了新的建模复杂性。特别关注的是判决反馈均衡器(DFE),其使用外部时钟信号(DQS)运作,而非SerDes实现中使用的时钟和数据恢复(CDR)系统。4 z0 L8 ^+ i- ~8 U+ o

2rsbwechgmz64084692441.png

" |- Y, n3 r* R/ X: K6 d图5:DDR DFE和SerDes DFE架构的对比图,突出显示了时钟实现的差异。( l2 {4 C( R* z/ a, G

' e+ y- F4 u5 b0 A/ G

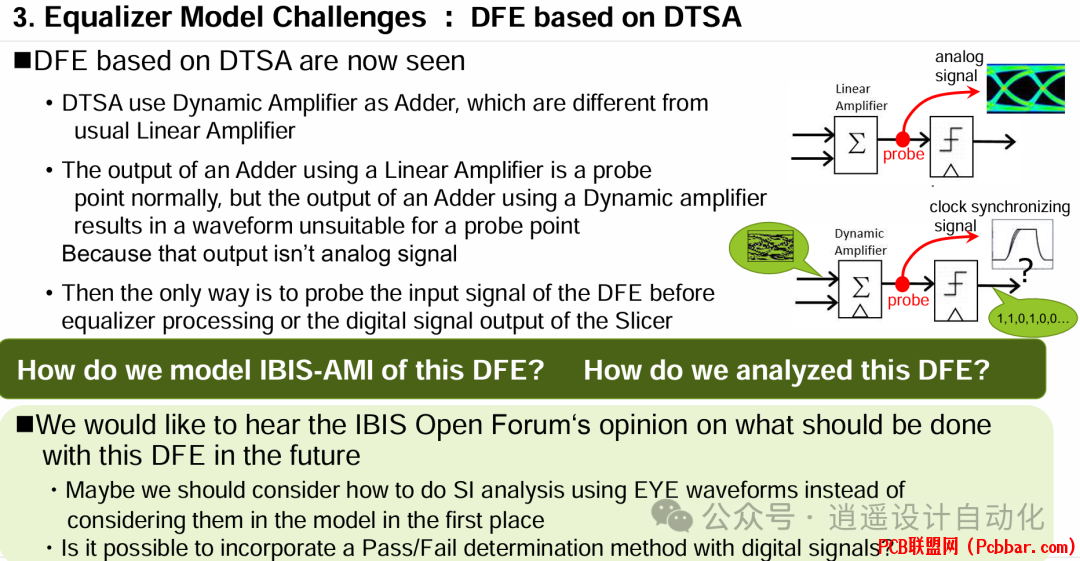

基于双尾锁存型电压感应放大器(DTSA)的DFE实现引入了额外的建模挑战。这些实现使用动态放大器作为加法器,在信号处理和分析方面与传统线性放大器有显著差异。

4 |8 { g" q7 x* [; ?

n1c21dooymb64084692541.png

1 F G8 }- Z- q8 @& |

1 F G8 }- Z- q8 @& |

图6:展示DTSA基础DFE架构和探测点挑战的技术图。- g$ f, Y* Y- c$ ], s' {

/ N' H2 F( S: m" k2 U随着存储器接口的复杂性增加,S参数模型的文件大小管理也面临挑战。随着数据速率提高和并行接口变得更加复杂,提取的S参数文件大小显著增长。这种增长需要仔细考虑磁盘使用、分析时间以及模型精度与文件大小之间的权衡。5 d3 o' G8 |, i' R K. {

1 u9 C; w `7 }) c3 ^, z% K3 ]/ W当前建模环境中,Touchstone和IBIS-ISS文件的路径规范也是一个挑战。虽然IBIS规范提供了文件位置规则,但由于缺乏明确的路径设置描述,导致在不同EDA工具中的实现不一致。这种不一致可能导致兼容性问题,使模型集成过程变得复杂。' ~2 ~$ C e- V/ ?, r1 J

" b; l& t. y2 }! j2 S$ A针对这些挑战,提出了以下解决方案:提升互连模型以支持与EMD相当的多重连接能力,为复杂封装配置建模提供更大灵活性。制定清晰的封装模型指南并促进行业采用,确保实现一致性和更广泛的工具支持。建立统一的文件路径描述规范,消除歧义并提高不同EDA工具间的兼容性。为基于DTSA的DFE实现开发新的建模方法,可能包括数字信号的通过/失败判定方法。

4 T7 N" k2 r" ~% z[/ol]

, M! w$ q7 J3 q7 \0 K- t基于DTSA的DFE建模提出了独特的挑战,需要创新解决方案。在处理动态放大器时,传统的模拟信号探测方法变得问题重重,因为输出可能不提供适合分析的探测点。这种限制要求在均衡化之前探测输入信号,或者处理切片器的数字信号输出。

1 c( f# {7 v1 A R6 s, `

) Z" G5 ~( O4 S) r% @8 n, MIBIS开放论坛和EDA模型专业委员会继续致力于解决这些挑战。未来的发展可能包括处理外部时钟驱动均衡器的新规范,以及改进的大型S参数文件管理方法。行业重点仍然是开发更高效、更准确的模型,同时保持与现有工具和工作流程的兼容性。

: u4 u- i+ m+ m6 y$ I

: `6 G# A- D7 @$ o( k参考文献3 A0 j* N2 Z( B9 I2 O

[1] M. Yoshitomi, "Challenges and Proposals in Developing Models for High-Speed Memory Interface," KIOXIA Corporation, Design Technology Innovation Div., 2024.4 Q! `: e. L/ Y7 N) R! ]& j8 J' _1 Q

* i+ ^* w# n" n1 U( |0 G6 [END/ M$ O$ `; F- a) H

& h6 j% s3 O4 J( `/ W5 g6 @

. g: L% y4 Y6 Z3 P- V

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

7 F/ h: E+ L b点击左下角"阅读原文"马上申请- a+ `3 c; I9 o

1 y5 C# f2 y' A0 Y欢迎转载& B1 [. k7 v4 |+ |5 ]

" r" R/ ?$ ?9 H. S/ S9 Y转载请注明出处,请勿修改内容和删除作者信息!

* K0 g; ?6 m" E% b, y! o: J# P; t

- \! R0 O* }: ?$ w% E/ B

) `+ _% j; g: n0 N0 [

3btwet2maic64084692641.gif

& ]& Q) Q3 r0 q6 g& D* a3 V) P. Z' T& x% r' O; \

关注我们

. W8 H& ]7 F4 ]% M6 v* Z' D6 }6 v, N6 b/ c4 m! w

% l' ^2 H& c3 x6 y: h3 P

aztrzpvcvet64084692741.png

9 ?6 v$ F% F5 [$ p

9 ?6 v$ F% F5 [$ p

| # B( z% X+ D) U, `4 F2 h/ u3 I |

oeovn4hrmex64084692841.png

. Q7 d* c6 }* w; r |

; B% C0 a" ^; w& d% f% S

dlyj0fg0ejf64084692941.png

; M! C: j8 b, [$ a, d

; M! C: j8 b, [$ a, d

|

1 q; f, p$ W' K+ R, W; A

/ `9 E3 K9 c1 u. J- q$ \

8 Z4 ~' a$ n3 m, v* K+ k& M/ |# u/ a5 E) r+ A

关于我们:

9 ]3 u6 K; M ]6 s! c. B深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。; y( x" `: k. O% r# W/ q' H- j

- }2 L- F* F% d' d/ A) shttp://www.latitudeda.com/

: I9 F( R! J( l* j(点击上方名片关注我们,发现更多精彩内容) |