|

|

引言

. F8 }& v- @3 w在半导体设计的快速发展中,电子设计自动化(EDA)在开发现代可扩展分离式系统中发挥着核心作用。本文探讨3DIC和系统技术协同优化(STCO)的挑战、方法和解决方案[1]。) W2 @: l, ?+ O7 u9 m2 |% n/ Y9 ^% g5 y

wqcew2cl1bw64046307736.png

2 F$ q3 @' J# H9 @4 e+ J# v

2 F$ q3 @' J# H9 @4 e+ J# v

# Y2 V M( H n1 O8 i5 g

1 j7 r5 K: K% s# F2 z

EDA和系统架构的演进0 x- U; V7 ^+ n U: v, e7 x

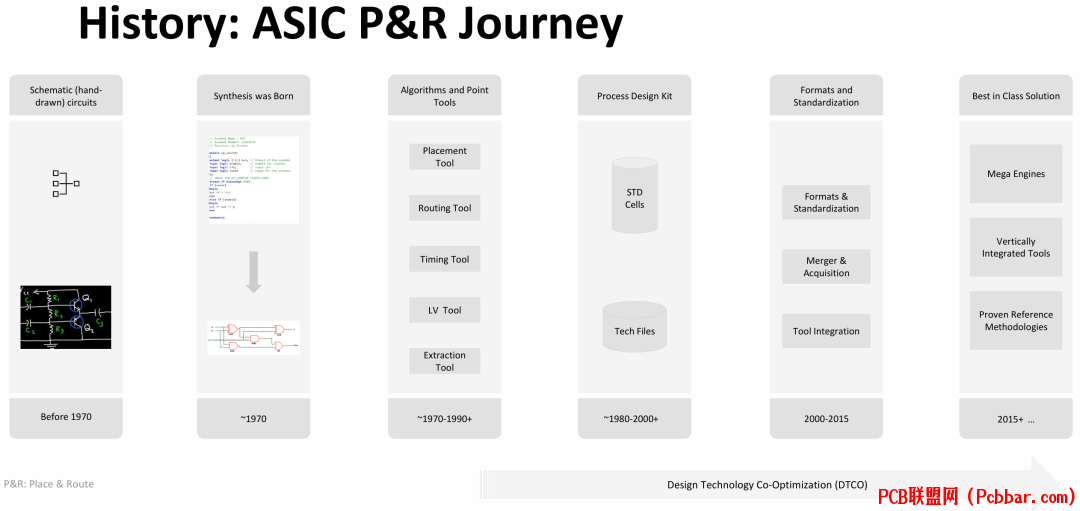

半导体行业已经从传统的专用集成电路(ASIC)设计方法发展到更复杂的分离式系统。从图1可以看出,自1970年之前的手绘示意图到现在的设计技术协同优化(DTCO),ASIC布局布线(P&R)经历了显著的发展历程。这种演进显示了EDA工具如何适应日益复杂的设计要求。

$ y |) N! V! v& t% J

gunlacj0du564046307836.png

. ]0 s% w! C5 S' z5 b图1:从1970年之前到2015年以后ASIC设计工具和方法的演进,突显了从手动设计到自动化流程的进展。

0 }, k9 E3 s% {7 y& I8 h" g% g8 `( J4 m

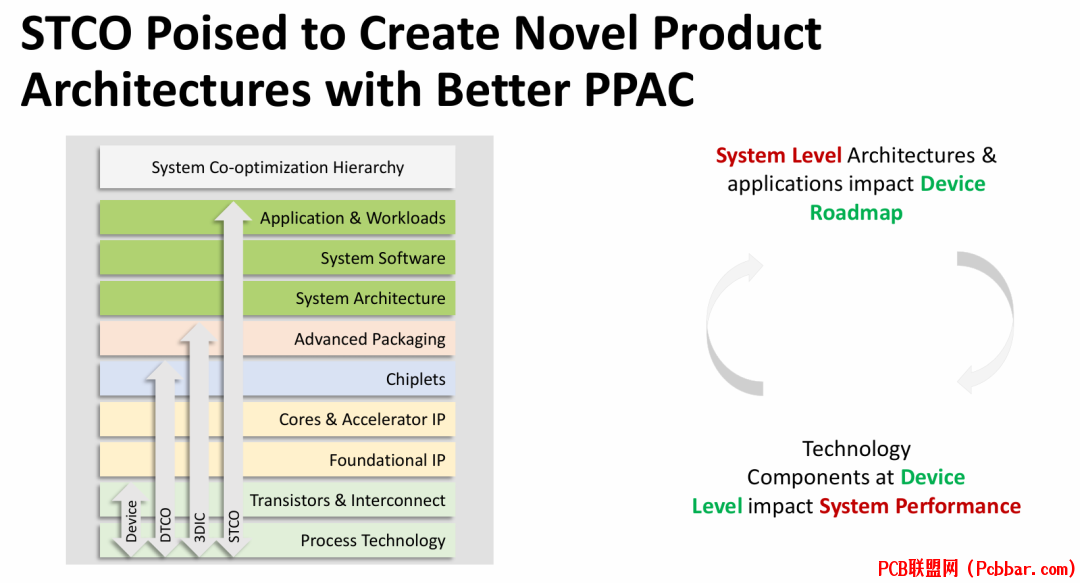

系统架构已经发展到能够适应新的市场需求和技术能力。图2展示了STCO层次结构,说明了从工艺技术到应用工作负载等不同系统层级之间的复杂关系。1 U8 U$ z( o: {5 [1 ?. K. d' Q! g

zm0jhw4c1tc64046307937.png

% C9 L0 d) D1 g* W# r5 A图2:系统协同优化层次结构及其对性能、功耗、面积和成本(PPAC)的影响。; p; R9 t0 q, }9 W" f/ v

8 j2 p$ f/ `( o1 h( c28 C4 I( q/ n j( I' Z" o0 P

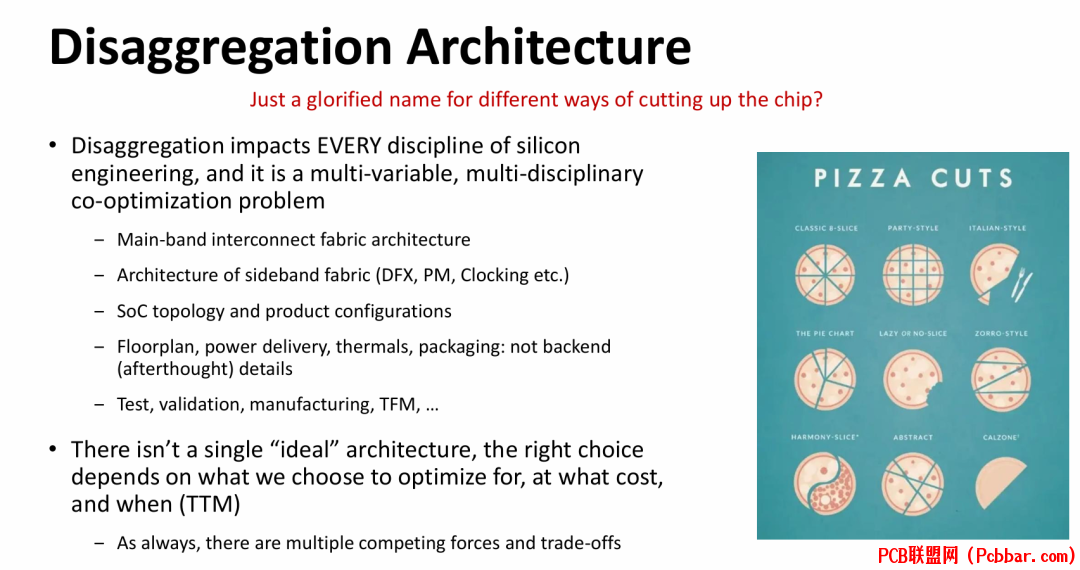

分离式架构及挑战

) m: Y% R! z8 I6 G# z" x+ d分离式架构代表了系统设计的根本转变。这不仅仅是芯片分区方式的改变,而是影响到硅工程的每个学科。主要挑战包括:

" I( J, y( {+ ?4 Z J6 D主带互连Fabric架构

$ s" M/ d* D% X0 l' [, a6 Z侧带Fabric架构(DFX、PM、时钟)3 W" @, R3 F( F' w! s9 z5 e' s

SoC拓扑和产品配置

2 X9 q9 V: e' a' e集成平面图、供电和热量考虑

8 z: M& F+ H! |# Q" i& ?测试、验证和制造要求8 x2 O/ E2 C' Z7 z+ m7 C0 B. Q$ S: R

[/ol]/ t5 s! E! e7 }+ q( V* t# ^/ v

4sq1hvbw2yw64046308037.png

+ r3 T4 s2 Y' Q3 x4 L8 n

+ r3 T4 s2 Y' Q3 x4 L8 n

图3:分离式架构的概念和各种实现考虑因素,包括比喻性的披萨切割风格。4 _7 Y9 e, S; z+ j# t; N

3 Z" X% J, D4 q4 N. H33 N$ O1 g/ ^! _* O3 n1 |. T6 ]5 }4 }

三维互连类型和实现: [( ]& O, f( r: [

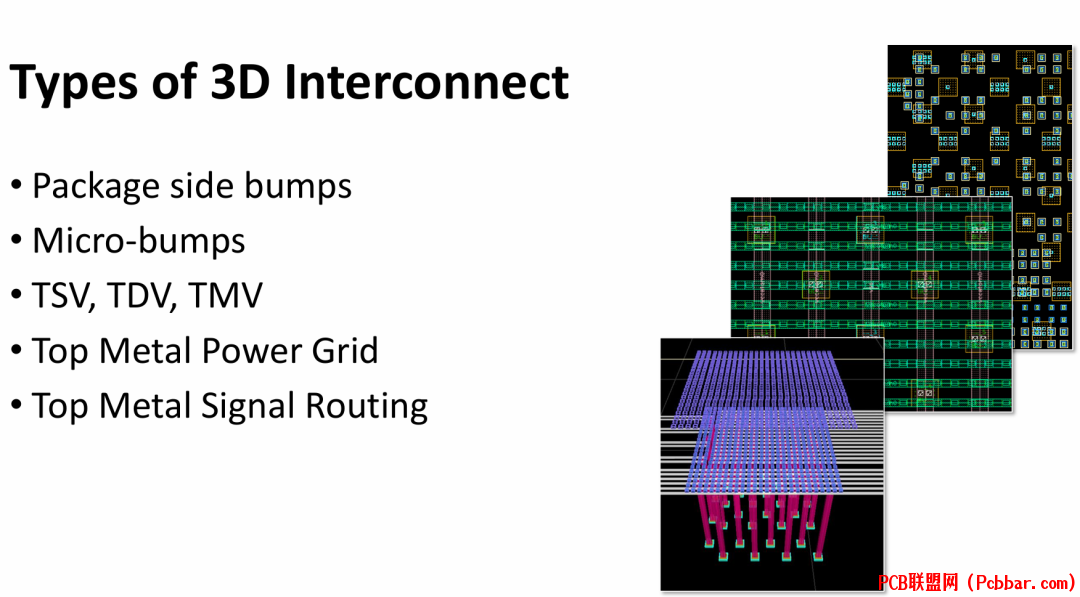

现代三维系统采用各种互连技术:

' D! R& G' r( O+ J6 e/ `/ R封装侧凸点! v: O5 Y1 W1 Q {

微凸点

8 \0 Y! w, i. r9 s" u4 p6 S0 Y& C硅通孔(TSV)、介质通孔(TDV)和模塑通孔(TMV)

( ?: P7 K% Y6 w' f6 u/ Q6 u顶部金属电源网格: ^$ a, @& B2 B

顶部金属信号布线

, p7 M. e* y/ _! N- X" C% `[/ol]

% ` w8 \" d1 E, B5 e4 a2 ^

lql1brcgplt64046308137.png

, f6 x& \2 b" M4 h4 o9 B

, f6 x& \2 b" M4 h4 o9 B

图4:不同类型的三维互连技术及其在现代半导体设计中的实现。

( R8 Q) s+ ]4 L% ]) U

6 k2 k2 ?: Z9 [) N. }42 { }- e; d! `5 @( B9 j3 ]

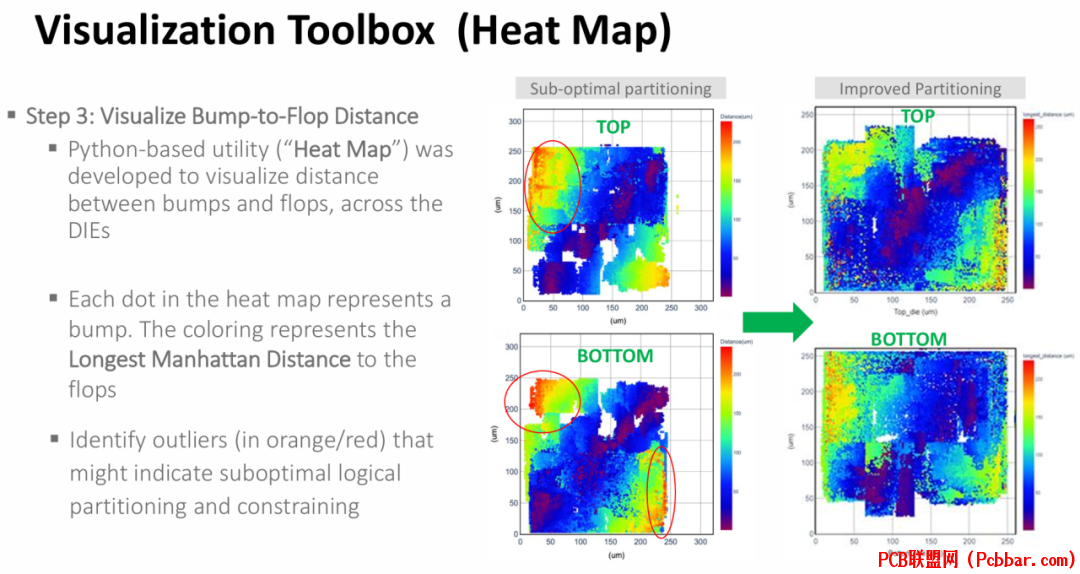

优化和分析技术

6 R. o( {, i- E- Y三维设计优化的系统方法包括几个关键步骤:* \' \8 h: K6 n7 y, D6 s

早期设计空间探索

1 J6 \2 h6 e' P( x2 b初始凸点放置

+ N% Q, n3 g# r0 b: k6 [ |凸点到触发器距离分析% y9 L- g x, O$ |. G+ l( e( v

模块对齐优化

. f! r+ m0 `* Y, T2 N- b[/ol]

1 q3 E; E" b) ^, m' w

2dh0pzkfju564046308237.png

" [3 \& l3 k a* q/ S1 X

" [3 \& l3 k a* q/ S1 X

图5:使用热力图来可视化和优化三维设计中凸点到触发器的距离。$ {. B) F+ Z7 l, w( W

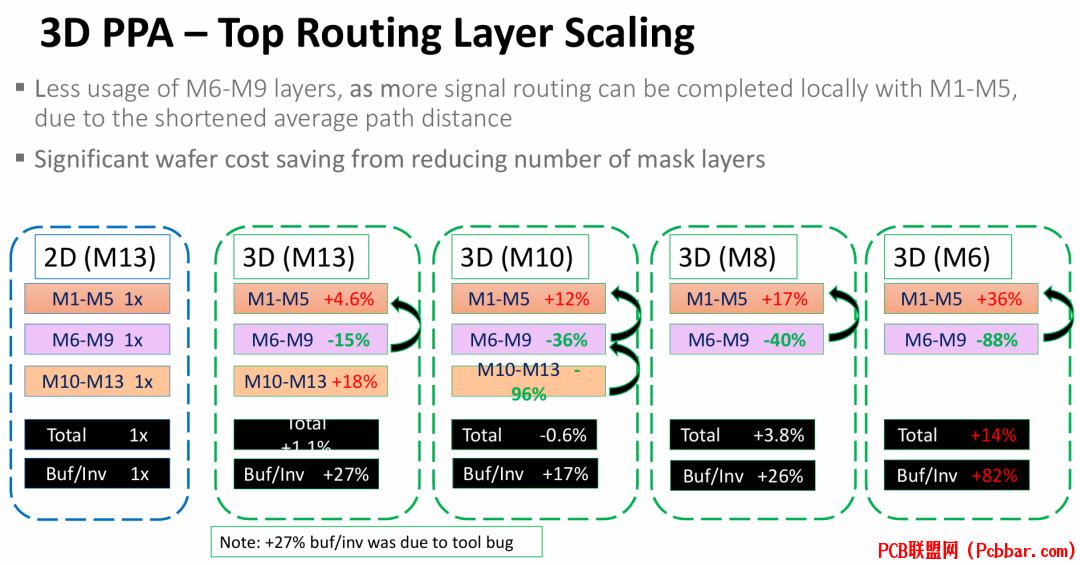

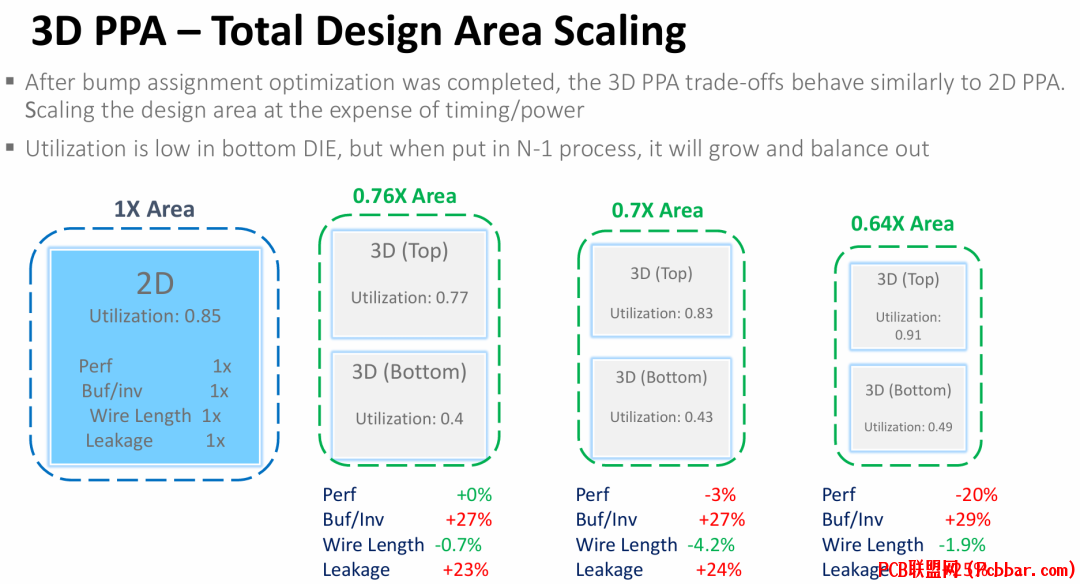

- I6 O* c$ C" |: I; X优化过程包括对金属层缩放和面积利用率的仔细考虑。图6显示了不同金属层配置对性能和功耗指标的影响。

' |( x8 k' @2 W

m4iw3wqclw164046308338.png

. ^; t; g3 W2 ~" E1 r5 X图6:在三维实现中设计面积缩放与各种性能指标之间的关系。

- v a: J& p9 g9 N8 L# Q5 W; a0 W! R8 _: e. p; @3 _7 \7 O6 B1 T$ l

57 f! ?9 P% f* K" m( N5 H

性能、功耗和面积(PPA)分析! U2 |: {+ c; s' l2 @! s6 @9 s5 I

PPA分析对评估三维实现的效果很关键。BZM测试芯片研究的主要发现包括:

' Z- v" z4 Z% s4 B在100,000多个寄存器到寄存器路径上平均路径延迟减少9%3 V( }2 n% O. s

顶部和底部晶圆的金属堆栈各减少两层

# H' a0 i8 {5 L) i1 C/ J面积利用率和功耗效率显著提升

1 E. \: y4 ]0 Z$ Z[/ol]

3 A$ k( i4 H. A4 \! `3 T

djt4i332csa64046308438.png

U3 O2 T+ i2 z" P( K图7:三维实现中各种PPA权衡及其对整体系统性能的影响。. W, O* `; c |' t$ ]

. Q% S% H: @' l. F1 B6

( ]3 L. d& ` x( X9 J未来方向和挑战

& U1 j2 g9 |3 E/ D% m [' G分离式系统EDA的未来发展集中在以下几个关键领域:

$ Z0 V+ Z7 ^ D9 B. A- b5 X自动化凸点规划和优化9 k3 N1 J5 p" u+ k$ r9 z

改进的TSV放置和校准2 s. z! y, d3 g8 j3 {% w

增强的顶部金属布线,用于电源网格和信号网络

3 v" q0 O+ |8 l支持早期原型的先进签核工具

% F# L, x& ?) E- g; w+ L/ Y g( r! }多物理场分析能力的集成

+ m P3 g) Q+ s5 ?+ x# ^& r

, R9 t0 f+ }: J7 S

2c4g0wbag5x64046308538.png

3 L/ y& t0 [% Q# ?5 \# o( K/ i

3 L/ y& t0 [% Q# ?5 \# o( K/ i

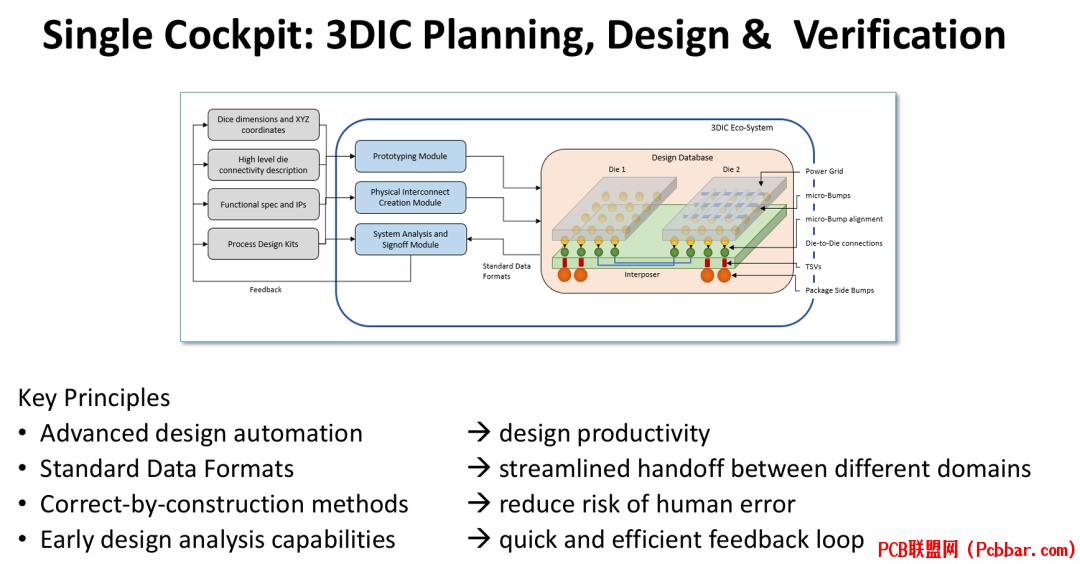

图8:三维IC设计和验证的集成方法,强调了统一设计环境的重要性。

: I* \' C( m. }7 P' H9 W( T# {# y' m/ I7 R" k8 o0 P, g1 X

随着系统复杂性的增加,对复杂自动化和优化技术的需求变得更加重要。重点仍然是在日益复杂的三维集成系统中实现最佳性能,同时管理功耗和面积利用率。3 T5 U) E! `1 G& K. `/ Z. ?

1 q7 n$ |- ?! ^

从架构规划到物理实现的各个设计方面的集成需要一个全面的方法来考虑所有系统层级。这种综合方法确保最终的设计满足现代应用的严格要求,同时保持可制造性和可靠性。

4 o9 W; n7 r2 B8 C' u3 [6 y. [4 u, L* n! {2 L* A. Y6 _2 b

参考文献

$ b! D/ y+ z5 Y3 H) v[1] V. Rajan, "EDA for Developing Modern Scalable Disaggregated Systems," in IEDM 2024 Short Course on AI Systems and the Next Leap Forward, SC2.5, 2024.

: _" q. A: q1 G3 d/ PEND3 q; h: Z' f8 z8 ]: y# t

1 p" m. {. d/ I! s

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

1 f2 }; |, p* L7 X点击左下角"阅读原文"马上申请

. {9 D: p {* M2 P2 ?7 Q: U

7 l1 J G: j3 G* ]4 f' }欢迎转载

$ a" G8 _- }( T, q

% X4 [+ e, z7 U$ F转载请注明出处,请勿修改内容和删除作者信息!) M+ r- ~: {0 Y4 g& D5 X( S

) x5 A% F6 d7 Q/ S: p

8 i9 i F& f/ F. Q! E. Q

$ H% d. C5 S4 l- Z" M2 a7 S* ~7 K

0il41fic4cv64046308638.gif

( U1 U% Z; f G% q: u+ _& L

( U1 U% Z; f G% q: u+ _& L

' [; a3 s: U' Y" K( _, J8 h

关注我们

& o: v+ Z) ~9 G: ^( X

0 B$ `1 W3 b( F) v$ Z

6 k( e* x+ t( ?8 f3 d! w2 {8 y

fzvupcx0mcj64046308738.png

@! l" O6 L0 H T7 [) |4 e | 1 {) u8 [% S& w: E" |

dcmgfvyyw4364046308838.png

8 T, O1 l- x6 X |

2 c. R: p! ^2 _4 K. N! r

uxfw0sflwos64046308938.png

' k% c1 S6 v" {% B4 U7 k/ f |

( N& O: T( e# u& r7 Y

8 x* q9 z9 T R* X8 ?

3 T: q1 Z0 }7 N) W5 e. H. Q) r

$ i9 `9 C- a: ^* `0 c关于我们: ^2 `0 ^; z! Z c5 Z* w/ j

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。- \1 F1 T+ |7 m' I$ a

0 u* v1 S; r* X

http://www.latitudeda.com/2 p* Y9 J3 [0 `4 z+ T

(点击上方名片关注我们,发现更多精彩内容) |

|