引言/ Q: u0 B; Y F1 _' L, D" A: N5 m

半导体行业在晶体管架构方面经历了显著的演变。从传统平面设计到FinFET,再到更先进的架构,每一次转变都源于对更好性能和持续缩放的追求。本文探讨这一发展历程中的突破——互补型场效应晶体管(CFET)技术。

, i3 e9 p2 P4 I+ ^/ I5 |

loju3g41fle64046309945.png

4 T' p3 i" r6 b0 u7 g( Q7 @

4 T' p3 i" r6 b0 u7 g( Q7 @

vhyijjaqyhv64046310046.png

# P5 O: M" o% l- R# f' U# c

# P5 O: M" o% l- R# f' U# c

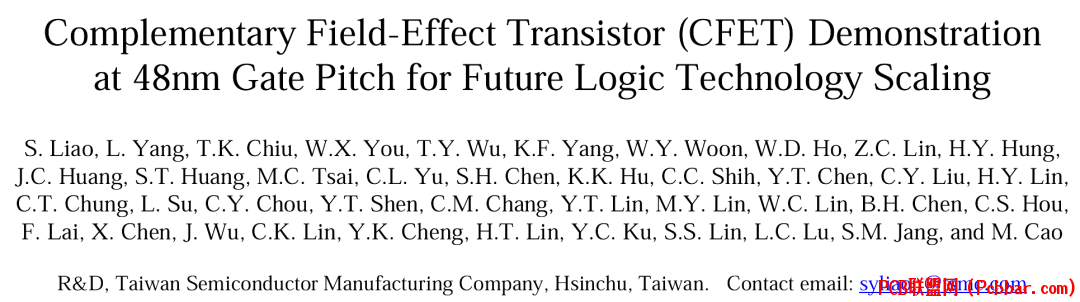

图1:展示了从FinFET到NSFET最后到CFET的晶体管架构演变,显示了工艺复杂度随架构进步而增加。- \5 y2 T" U% h: A! J

# k& t) p+ m( ?- f% [. x# T6 o1$ ?# M0 F$ [9 S4 {5 k

走向CFET的发展历程

9 t* L% Q, {3 t: b大约十年前,半导体工业从平面晶体管转向FinFET架构。这一转变是由FinFET器件优异的静电完整性和可扩展性推动的,使栅极间距和单元高度的持续缩放成为可能。行业已经成功运用了多代FinFET技术,但在推进半导体缩放极限的过程中,出现了新的架构——纳米片场效应晶体管(NSFET),也称为环栅(GAA)技术。0 R8 x- v- D. D7 P9 |

p5dxflo23my64046310146.png

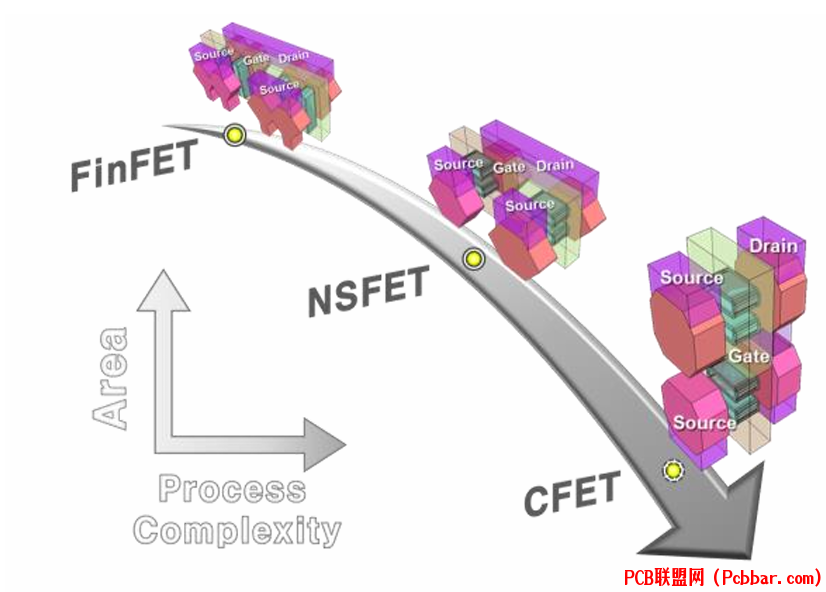

9 d" A/ g( t4 N' _7 P6 h6 ^) G图2:说明了CFET如何通过nFET和pFET的垂直堆叠实现1.5-2倍密度缩放,比较了传统CMOS架构与CFET在反相器和SRAM配置中的实现。0 ~9 ~# G! h: m

; |2 l p8 J5 l2

9 s3 q- ?0 ]* N7 H' w+ l9 eCFET:新一代架构1 Z) x7 D5 u" s& d

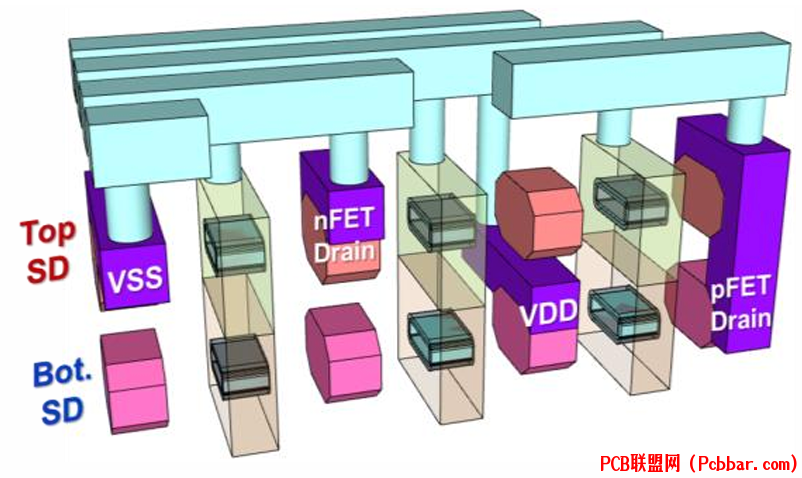

CFET代表了晶体管设计的重大进步。通过垂直堆叠nFET和pFET器件,CFET在相同栅极间距下提供了比传统CMOS架构高约1.5到2倍的密度。这种密度提升来自创新的垂直排列,但垂直局部互连所需的空间在一定程度上限制了缩放效益。

9 J6 y6 ^0 Q$ g1 I+ _

4iq1jh3hq0o64046310246.png

, k j: e7 I7 h: Q4 R4 o4 q. X5 W

, k j: e7 I7 h: Q4 R4 o4 q. X5 W

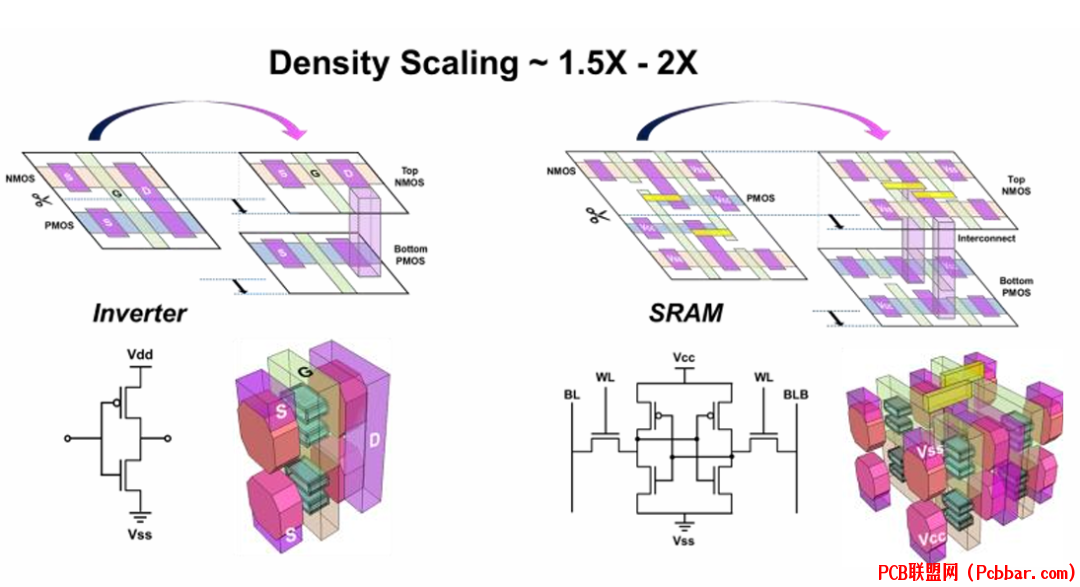

图3:详细的工艺流程图,显示了顶部nFET和底部pFET器件单片3D堆叠CFET制造的关键步骤。

% d) K" E: p- o0 f& Y6 U. l1 r

' V2 m5 R# t( D# B3 }% V5 K3* U! C0 i7 `9 r: y) {

技术实现和制造/ |' O4 g; }4 K$ l6 l% s+ i

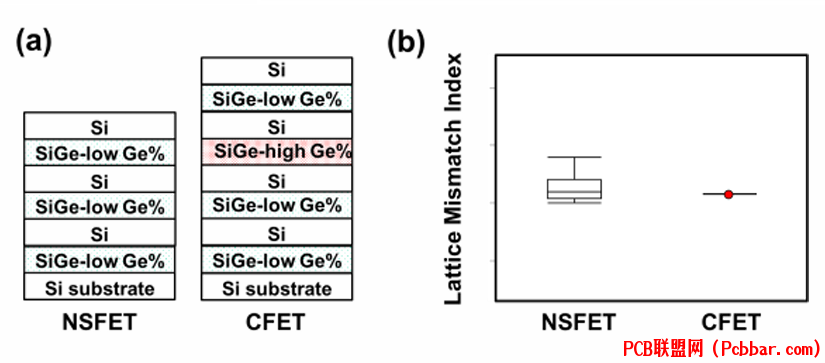

CFET器件的制造涉及复杂的工艺,始于SiGe/Si超晶格堆栈的制作。CFET设计的独特之处在于包含了高锗含量的SiGe层,作为中间电介质隔离(MDI)形成的占位符。

8 u7 k- a/ \% I8 \6 w3 r

yn4utg15wts64046310346.png

2 R5 t, }2 J; e- c/ n* @/ S% v# T

2 R5 t, }2 J; e- c/ n* @/ S% v# T

图4:比较传统NSFET和CFET的SiGe/Si超晶格堆叠方案,显示晶格失配指数作为质量指标。. p' K' M5 ~7 I o

C6 P( ?2 m2 F/ J3 ]

制造工艺采用最先进的技术,包括:, l' Z6 H% Y. n# F- M

用于纳米片堆栈图形化的极紫外光刻; E0 v7 ~# ]: Q/ E

浅沟槽隔离(STI)形成

. `' ]* x1 `0 S; _, `栅极间隔物沉积

0 z9 M( \/ n9 m' m源极-漏极外延生长

. D+ l/ {, ~7 S; q# \8 M1 V. u/ U }3 h9 d( U

3xkeelgmzhr64046310446.png

/ C$ Q- ?" S9 z# c e

/ C$ Q- ?" S9 z# c e

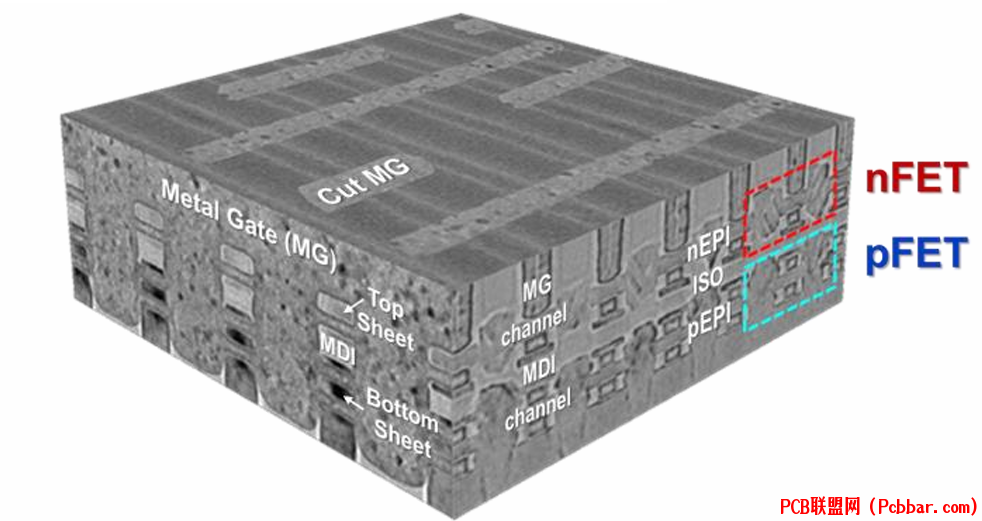

图5:48nm栅极间距单片CFET的TEM演示,显示了具有共享金属栅极结构的nFET在pFET上方的垂直集成。- A0 X% S& X! @2 o8 Q6 f

) }6 u! w' H% Y/ D3 F3 T% g4

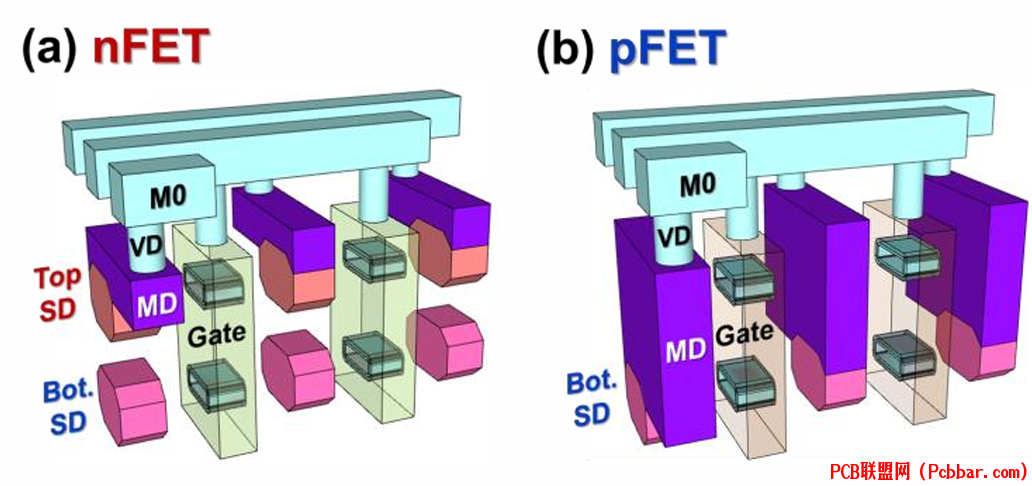

+ n, `) u4 u. q n器件结构和集成9 [$ ~: L0 L0 Y- s' ?+ \

CFET结构包含多个创新特征以确保最佳性能。关键要素是中间电介质隔离(MDI)和内部间隔物(INSP)的实现,基于锗含量实现SiGe的选择性刻蚀。 w1 D7 W7 I1 r* l& M

s2bkurildk264046310547.png

, m4 i5 @+ |. K* N* n9 w4 q图6:详细示意图显示了3D堆叠CFET结构,分别用于nFET和pFET电气表征的独立配置。- |+ \' |* G- m+ _3 {. J q$ k

: [9 o3 T- Y1 Q) {& @

42zhnounlho64046310647.png

$ J/ I5 F/ \) U; j

$ J/ I5 F/ \) U; j

图7:完整3D堆叠CFET结构的示意图,显示同一晶圆上的nFET和pFET触点。* {; H2 R9 y6 V5 r" F

% [3 B9 r2 L% r; O/ `+ n/ e% R

5: A3 t- A4 ]3 g1 u/ Q

性能和结果

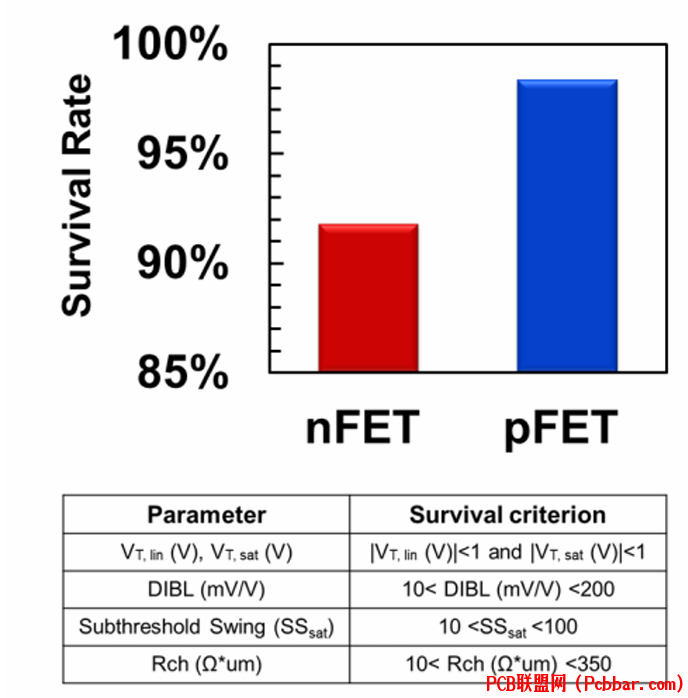

$ \# y% b' n. RCFET器件的电气特性显示出优异的结果。nFET和pFET都展现出优秀的性能指标:

% _9 M' `+ f9 B" h3 d D5 Q

htrwmx2en3m64046310747.png

. [* _$ N1 p N

. [* _$ N1 p N

图8:显示nFET和pFET器件存活率超过90%的图表,以及用于评估的存活标准。

# u) Y7 K, L3 r3 W9 N' q [9 h5 m5 w- A

ofmli1yacjw64046310847.png

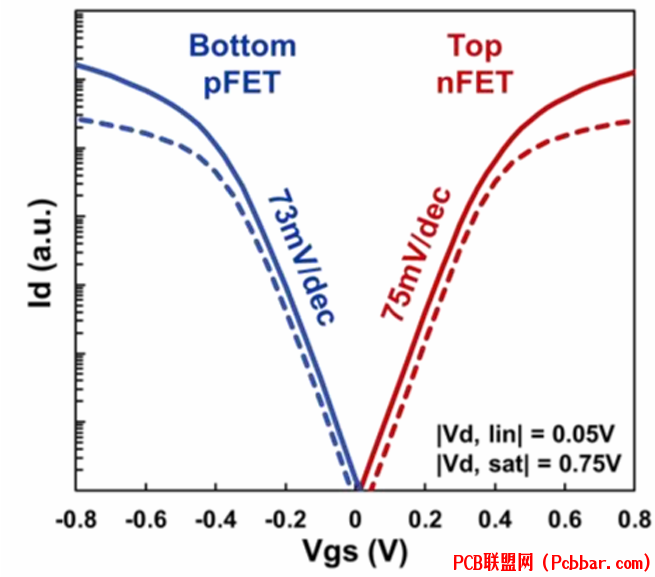

. X L8 \$ Q7 f3 D/ B' T" u图9:Id-Vgs特性曲线,展示nFET和pFET器件优异的亚阈值摆幅性能。

' J. ~0 F/ i5 m* F

F- m0 W$ Q3 I6 x9 [器件实现了nFET为75mV/dec和pFET为73mV/dec的亚阈值摆幅,漏极诱发势垒降低(DIBL)值分别为50mV/V和45mV/V。

0 B" C3 R/ ^2 p9 t$ \6 R

ommdsth2xil64046310947.png

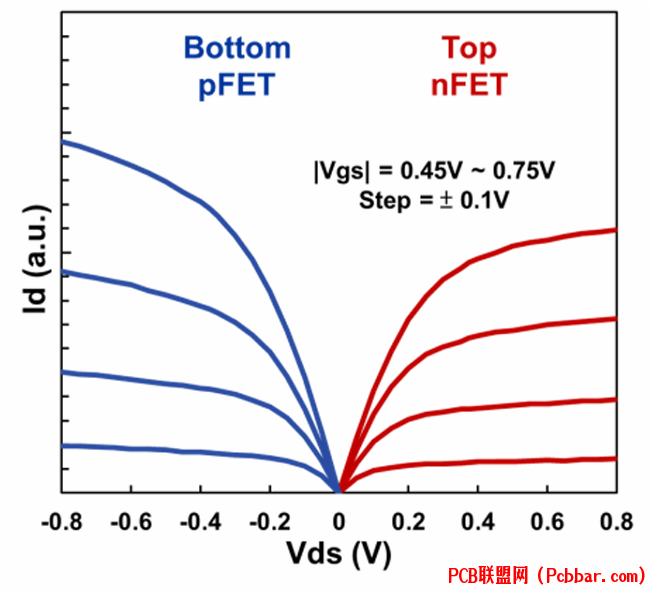

3 Q4 k. k, C7 d# K, C; ?, ~图10:Id-Vds特性曲线,显示两种晶体管类型的高开启状态性能。

4 k! C0 g' T0 b; D$ E$ [# ?' O; d; L- \% F* J% v% k

61 Q/ U9 C8 P& |$ l

未来展望和挑战

& A) v' R+ I' u0 P0 v! N& ?8 UCFET技术虽然展现出优异性能,但仍面临一些挑战。堆叠的nFET和pFET之间的垂直局部连接和隔离集成仍然复杂。然而,48nm栅极间距器件的成功展示为未来发展奠定了基础。 \1 Z; P, J5 h' b) G9 e

' E& y* X( ^. U6 Z0 m9 B通过持续的开发和优化,CFET能够实现逻辑技术的进一步缩放,同时保持或改善器件性能。这些器件在48nm栅极间距上的成功展示为半导体技术的创新指明了方向。

" z2 a. D$ g. `6 K# Z7 H( k

) C+ c/ X7 @9 t5 _4 k+ f5 d" M参考文献9 C2 k3 Y, N; l& k) k+ q2 m* j

[1] S. Liao et al., "Complementary Field-Effect Transistor (CFET) Demonstration at 48nm Gate Pitch for Future Logic Technology Scaling," in 2023 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2023, pp. 979-983.0 k; R0 M1 y* I, @8 C: F

END& y" \1 M8 a8 X' o! A- G6 k& ]# X/ u

3 V9 k7 d( i9 w( h9 O& i

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。5 l/ V5 F2 u1 q8 G* f2 j* O

点击左下角"阅读原文"马上申请1 a8 ?5 m+ k5 Y" H9 x/ b( ?) J

3 ?/ W! |4 B8 |+ F欢迎转载) w( l% F) f( k

8 I% {" R% O6 F

转载请注明出处,请勿修改内容和删除作者信息!' P9 y8 { m* W; D# N3 R( [5 u) E" x

+ V& n L" e" H+ \

3 H+ V' w& J; q& t

$ ^$ i" K4 X" l; C* Q# n9 H

lloosb3blvl64046311048.gif

9 M+ O0 n5 H1 N1 g

9 M+ O0 n5 H1 N1 g

: y9 h9 f" y- F

关注我们 o/ \# `0 ~+ q

( A8 m2 L3 V6 P* b6 P: e4 f

. P1 Y$ n. n" |5 L/ ~- X, R* }

lli3m2by0z364046311148.png

8 k4 v3 `% U% z4 N2 ^- R) ~8 K | 7 [0 V) g2 B2 ^

wakjhnykkca64046311248.png

& O7 e) g4 M: D/ J; I, | | - y+ \6 l0 y( P* Y& ^7 _

nt2cnhapprf64046311348.png

1 H- _% z2 a2 K6 { |

- A$ G* G9 k8 q7 }8 a. H$ a

6 W/ t/ E9 f- a8 I: v1 f. n/ F0 ]$ E

; M; y" X+ h3 j0 p5 ?: }关于我们:3 z7 Z0 {6 [8 ~& T! w; C

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

4 c2 b m6 ?# O

4 A. h. p& M1 `& ]8 }2 n5 Y' k. f$ Fhttp://www.latitudeda.com/' `5 E5 X7 j, z2 F

(点击上方名片关注我们,发现更多精彩内容) |