|

|

|

4y1nveukrur640222410.gif

6 j' V0 e8 v' y5 q# }点击上方名片关注了解更多

( P5 b- |( v. w

% ]! `5 } B1 D( [; y

0 C s+ o# n0 l' z+ K) t( B1 |- y5 N8 f. i+ [$ N2 o+ G

摘要0 k6 u/ W* _2 r: ?

DC-DC BUCK,是硬件工程师工作中使用频率非常高的电路,可以这么说,只要板子不是迷你型的,十有八九都有DC-DC。因此,对它的了解与学习是重中之重,也是考验一个硬件工程师对MOS管,电感,电容这些基本元器件的特性与使用方法的掌握程度。& K+ l7 L ?9 J# S' w4 T. Z

本文将详细对DC-DC BUCK拓扑,进一步到DCDC芯片实际框图的各部分原理与参数选择等进行较为详细的说明,逻辑推论主要以工程推论为主,公式计算为辅,对实践设计有学习意义。" j& Q" V/ z6 q8 U

本文主要做知识记录与学习分享,部分图片源于网上。% n/ z8 R# H' d$ ^# h

BUCK原理+ B& d$ D$ W# v" o, j, [4 s6 P6 j

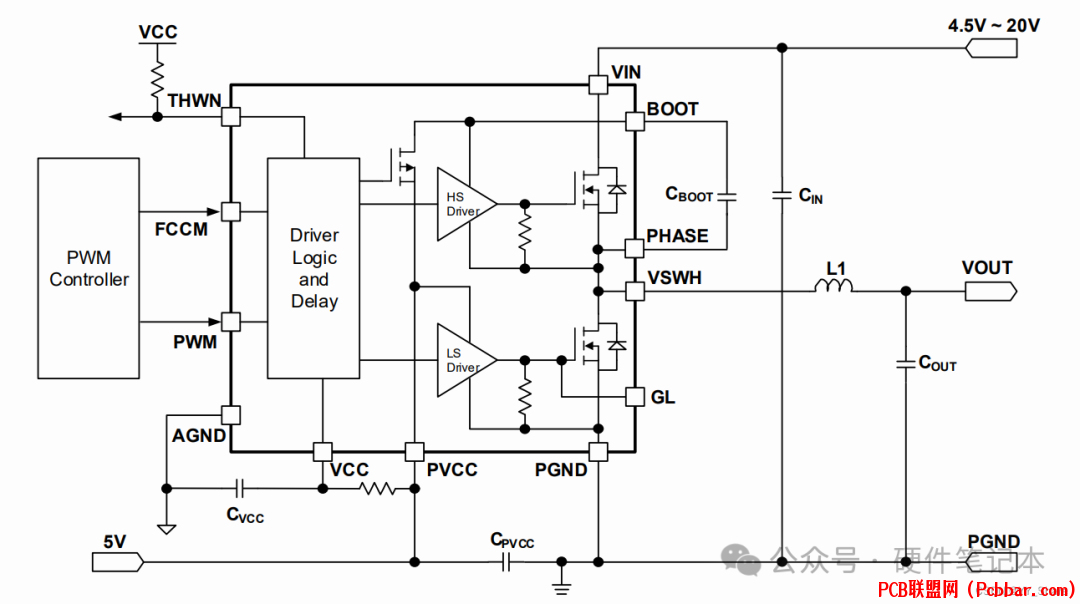

如下图是同步BUCK的拓扑:$ |, Q( I: P b) Z7 M' j

1、当Q1导通,Q2关闭,SW端电压为输入电压VIN,VIN给电感L1充电,电感电流增加,VIN=VL+VOUT,此时电感电压左正右负。电流方向为图示蓝色回路。8 q0 U/ p/ B8 v# @

2、当Q1关闭,Q2打开,由于电感电流不能突变,电流按照下图红线路径形成回路,给负载供电,此时电感电流下降。电感电压左负右正。1 c8 A+ X- ?- s1 \: b& @9 f

根据伏秒法则等推导,同步BUCK得出一个比较重要的公式:# ]0 \; o8 b$ r) d

VIN*D=VOUT0 [; \1 b& y) R, \- ~

简单地说,占空比跟输入输出的电压有直接关系,相对而言,如果输出电压越低,占空比就越低,理解起来就是,因为输出电压低,所以需要打开上MOS管对电感充电的时间就更少了!# J5 d" b7 {- N& F, Z% Z: N: P# E7 ~0 l

(这里要注意,这个只是在完美条件下测出来的理论值,实际会因为有损耗等情况,与理论值有差别)

+ N3 M+ j) _+ H" y, ]3 @

bspg3bde2u4640222510.png

" P) I' [9 W# y3 o根据上图拓扑,得出下图波形 K' U2 o2 q0 `; ]2 S$ }

a、当Q1打开,Q2关闭,Vsw为高,IQ1增加,IQ2为零,电感电流增加。1 y0 N+ [% |$ D) I/ F ?

b‘、当Q1关闭,Q2打开,Vsw为低,IQ1为零,IQ2减小,电感电流减小。

- d0 i& G( V& ]. `c、整个稳态过程,电感电流不断增加减少。

: G7 ], g: O+ g* @! _d、我们常将上管打开的时间称为Ton,其关闭的时间为Toff。两者相加是一个周期。

1 y7 L+ p2 T/ C7 r6 }4 d

ppqtjjna5u5640222610.png

7 C: I t! C1 R* b2 G l这里放一个有意思的仿真波形,绿色为电感左端SW电压信号,红色为输出电压信号。; R. I8 ^' t1 M+ W- ]

当没有输出电容,但是有负载的时候,可以看到输出电压的波动随着SW开关的变化,SW为高时,VIN给电感充能,输出电压增加;SW为低时,电感消耗自身能量,输出电压变低。

# ]1 x# A" |' e6 t( F. z' E! Z! S+ G( \

f2otukyfaj2640222710.png

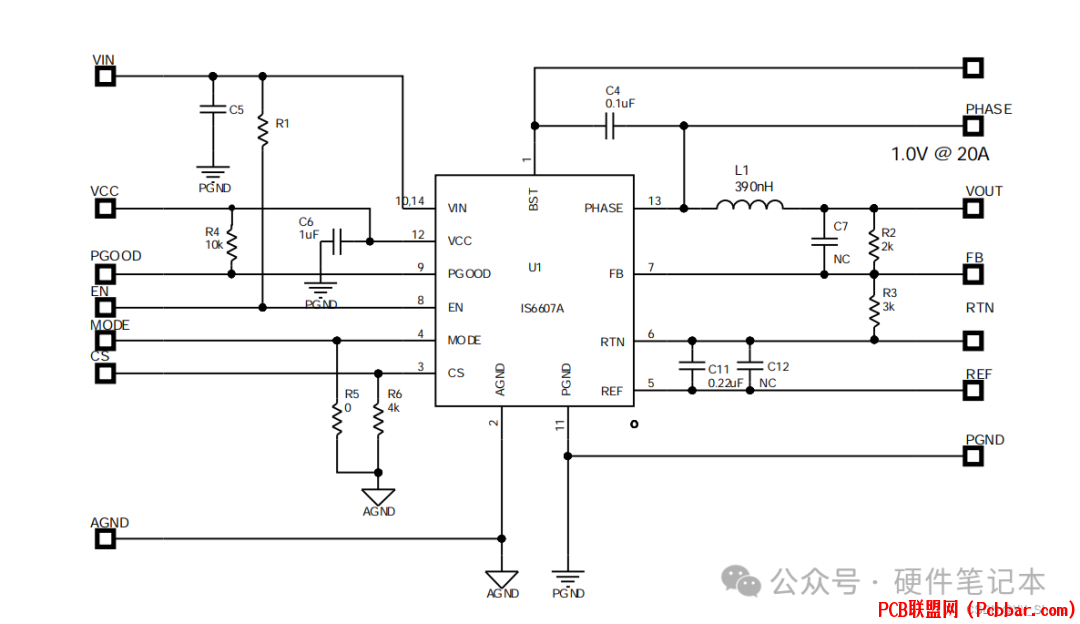

6 A: q4 [: {9 d9 B0 m9 WDC-DC芯片框图

& A- {4 K# s4 ^' N7 n0 y$ Q6 B; l5 NBUCK拓扑图,比较简单,我们结合实际DC-DC芯片框图,进行较为深入的说明。

+ {& q" j# H% W( e在DC-DC芯片框图中,还是有那两个MOS管,电感,电容,多了一些 Driver,Controller等逻辑电路。

$ k1 ^" m" a* O+ Q' E( K3 C- p简单的说,就是利用电感储能,电流不能突变的原理,通过PWM控制 HS Driver和LS Driver进一步控制高边MOS和低边MOS的打开和关闭,调节输出的功能。( F6 b# c' ]7 Y* h

etmtdnayzcp640222810.png

) H p# i0 `$ g( ~$ m h按照功能,分为逻辑驱动、功率转换、负载、电压采样和反馈补偿。

, X! Z) x8 s# |* z

t4pdarjf4uj640222910.png

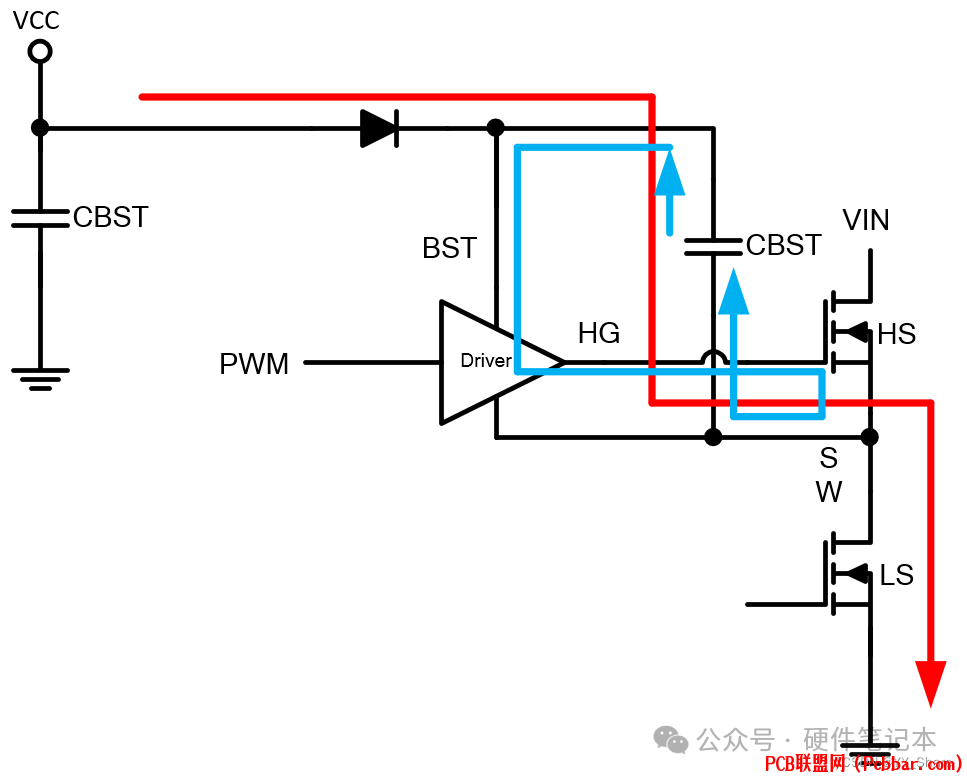

2 ~, Y! c0 B& v ^自举电容

6 M5 y% W+ i" x* i: v描述

1 |; V- w: _, n. bCBOOT,也叫CBST,中文意思是自举电容。

2 ~" m" v2 B5 l作用8 T2 I; \& c$ c- {4 K& P; C* ~4 a

维持High-side MOS的开启状态。(维持这两个字很关键), M/ y! S# ]8 K* o: G

工作过程8 Z# I' \3 \* ~4 J6 a$ b; P' @

1、初始状态,LS导通,HS关闭(HS的 PWM输入为低),SW电压为0V,VCC通过二极管对CBST充电至VCC电压(红色路径)。

' f+ H2 a! y, w! ^2 d2、当PWM为高,HG电压升高过程中,HS开始导通,SW电压上升,由于CBST两端存在压差,会同步抬高BST的电压,而driver内部HG和BST连通,HG电压也会跟随BST升高(蓝色电流路径),从而维持HG-SW的压差足够高,保持HS的导通。

3 W( P% P8 p0 u7 t

ejpgr3p5tpi640223010.png

' D8 m( Z- S8 \8 `5 G选型

! b3 ]$ y! p- ]$ W# }8 c最常见的是0.1uF。2 g3 x( Q$ x* v: T3 J8 x4 | c) t _

1、自举电容不能太小,至少要保证要大于高边MOS所需的导通能量+漏电流+高边Driver消耗电流+自举电容本身的漏电流。+ S' h- r7 [0 H, N ?0 `

2、自举电容不能太大,如果太大,在对自举电容充电的时候,该周期内无法对自举电容充满,导致上电压偏小,无法使高边MOS导通,输出异常。

/ Q b' x5 T9 E: w, ^/ [& J$ }设计角度上,耐压需要超过芯片内部VCC电压即可,为DCDC芯片内部LDO输出电压,常见是3.3V。也有的芯片内部不做LDO,需要外部接入VCC的。7 E' v4 N' k* ?- N$ Q6 e

输出电感

: b1 ?8 D. J$ [0 }5 \ u% R2 K! [DCR,这是电感的直流电阻,这个值越小,在电感上的损耗就越少。但是有的芯片会使用电感的DCR进行电流检测,如果有这个功能,这个值就不是越小越好了。

6 @. }. C# O5 x4 W {有意思的是,如果DCR比较大,这部分损耗会以电感温度上升的形式表达,这样又会降低电感的感值,增大纹波电流和纹波电压。+ C4 `% u5 f3 ~0 U# s

饱和电流,通常指电感量下降百分之30的时候所对应的DC电流。

! V6 l$ E8 D" m f8 @温升电流,通常指电感升温40度时的电流值。

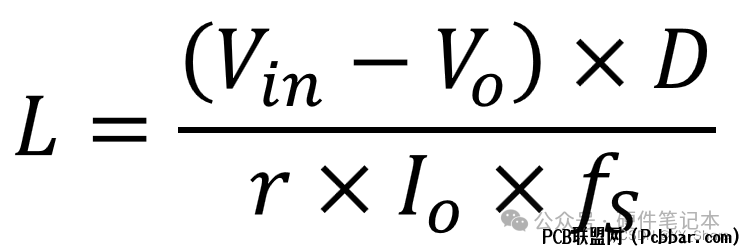

3 C! I/ K/ ?9 k7 b6 b* h7 b逻辑上电感有个最小值,要大于一个量才能够包容得了纹波电流。

$ W% m" m/ [6 N4 c& L根据电感的特性,电感越大,储能能力越强,对电流的抑制作用越明显,所以纹波会更小,但是动态响应降低。同时,一般来说,电感越大,尺寸越大,DCR越大,电感的损耗增加。

5 c1 U0 R& X2 ^% v

xbxai2wq5ul640223110.png

' j D" U8 T" ]流过电感的电流由交流分量和直流分量组成,交流分量频率跟开关频率一样,会通过电容流入到地,产生响应的输出纹波电压跟ESR相关。8 ?6 R# B3 \, w$ Z+ Z! H

选择电感时要确保饱和电流Isat大于电感电流峰值Ipeak,避免电感饱和,感值下降造成MOS和电感损坏。

8 H; H* t5 w, m2 |3 o

a50cnjpzmmy640223210.png

) \+ r2 t# O, @. C9 T. ~' B z' g

) \+ r2 t# O, @. C9 T. ~' B z' g

其中r是电流纹波率,一般选择0.3~0.5左右。$ ~' w' Y( |9 Q+ Y( ]$ S

工作频率

( O0 a$ H4 W' u) O: ]增加频率,会缩短一个周期的时间,纹波电流将减小。5 V+ p6 K" I# i3 K' o1 T/ k- P

输出电容和纹波$ @& H& T- s* r0 a9 `+ H

还是这张波形图,没有输出电容,有负载的情况。简单理解,电源纹波产生的根本原因,就是上MOS管开关的过程中,电感电流的波动,进一步导致输出电压的波动。# I4 \# l% o# c6 @& o6 f

aqjblxwmw4h640223310.png

' m ^# q2 a6 A! a; d作用:% n$ o3 [* } A7 }* Z% f

储能,滤除电源噪声

$ P+ j( ]( e8 b4 B0 T选型:1 F, N3 h) D! x& u! U" I

耐压、容值、ESR等参数。

6 t: X2 B* E9 j M$ Y# F* p4 c. e/ E; L耐压一般需要降额百分之八十;$ D* b6 |8 ~ e" U0 s

理论上容值越大,效果越好,但是不同的电容,对于相同频率的阻抗是不一样的,如下图。电容一般选择混搭的方式,即大容值的固态电解电容跟小容值的MLCC组合,以实现全频段都有较低的阻抗。

4 N3 i; F6 ~4 g- o: E) `- ^- X其他参数相同的情况下,输出电容的ESR越小,输出纹波就越小。从工程应用的角度去理解,就是输出是有纹波电流的,如果ESR越大,在电容这段变化的电压越大,表现出来是纹波的一部分。0 v/ t; R# P; d5 |

pncf3hqng0f640223410.png

$ K& g4 A9 i" B5 l; r" B1 _

$ K& g4 A9 i" B5 l; r" B1 _

前馈电容- F: Q9 Q+ R9 }2 S v/ d- F0 h

前馈电容,为下图中的C7,并联在FB分压电阻的上端。

) p' B! Y7 U% ~0 v4 x) M前馈电容的作用机制,就是利用电容两端电压不能突变的原理,将VOUT的微弱变化及时迅速的反馈到芯片FB引脚,所以其目的是增加芯片的瞬态响应,可以优化纹波。1 o n. {- }: c: y

r02xdpuayny640223510.png

; Z/ _, D! i8 x8 n* L3 B/ X损耗: {7 U7 |1 f6 X1 ~$ c1 ?& l# n [( u5 @

开关损耗- i* {+ w; n: C% p1 f

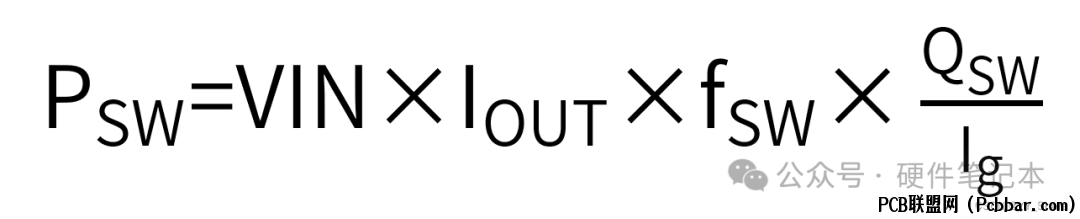

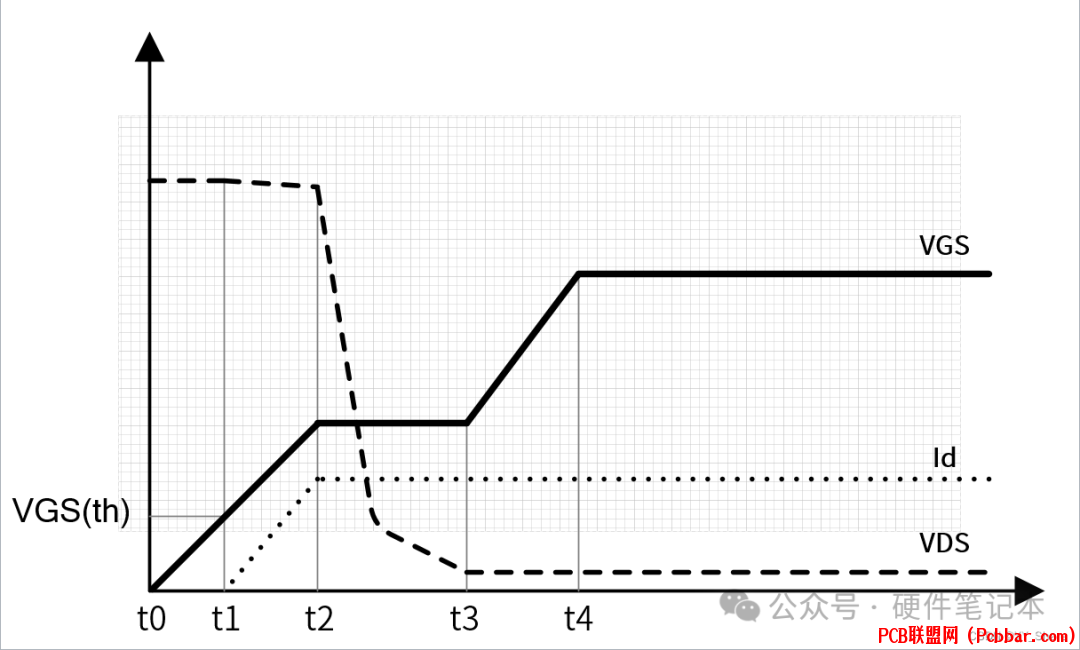

开关损耗主要在高边MOS,在开启和关断的过程中,出现电压和电流的交叠区,此时消耗功率:

5 ?- p9 D3 {* b" v- T

555r0kkwqtb640223610.png

6 J( W, v. Q! \2 N% r* g

6 J( W, v. Q! \2 N% r* g

换句话说就是,MOS管打开是需要时间的,虽然说这个过程对于我们普遍的认知来说很快,但是工程上不能忽略。+ m. G" ^; k& p4 s

nhjsiaoah5n640223711.png

, C+ m' j, d' N开关频率越高,相同时间段内转换的次数就越多,所以开关频率和开关损耗成正比。

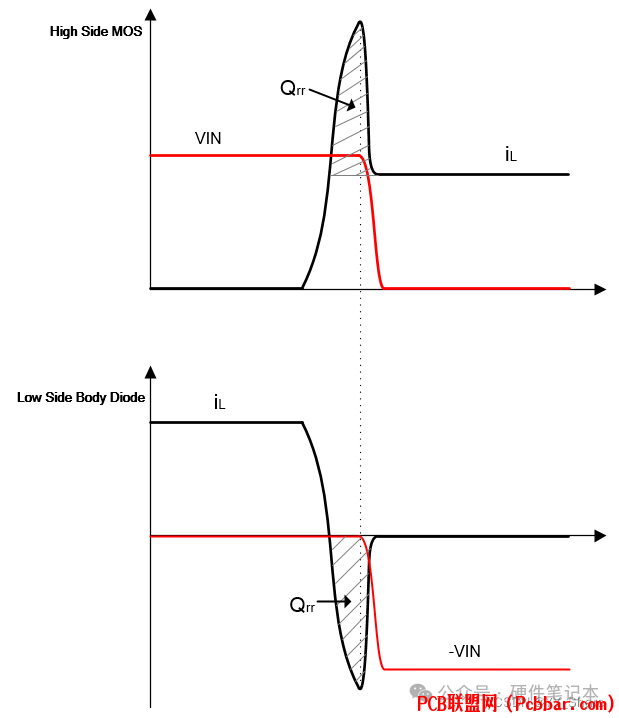

0 J k; Z. H5 d2 v而对于下MOS,这个就有点意思了,需要捋一下过程,首先上MOS打开,给电感充能,然后上MOS关闭,进入dead time,此时由下MOS管的体二极管进行续流,dead time时间结束后,下MOS管打开,由于此时下MOS管打开的过程中,VDS电压非常低,可以认为下MOS管的开关损耗非常少。% F" c, x; ?3 x# s9 M. `

导通损耗

% s# L. g; l: O; `! n上下MOS在导通的时候都会存在导通损耗,这个参数跟Rdson有关,因为MOS在导通时不是绝对的零通过电阻,只要有电阻,通过电流,就会有消耗。

( V% O) g" a& R' i3 r; n

ohz5q44cvae640223811.png

# H; D' w. _! \ d4 \这里需要注意,在稳态连续导通模式的时候,电感充电流和放电流的量是一样的,所以上下管的通过电流一样,所以HS和LS导通损耗比跟PWM的占空比有关。如果占空比D为百分之五十,可以认为上下管的导通损耗一样。

4 c9 C* L8 b5 K; R h6 \# {/ p但是大部分D都小于百分之五十,所以我们说下管的导通损耗比上管的大。同时,上管主要为开关损耗。关注公众号硬件笔记本- h/ s# h d- E d* _; o

dead time2 ]: y8 D4 K+ g

为了不让上下MOS出现同时导通,将VCC短路到地的情况,两个MOS开关之间存在dead time,下管关闭然后经过dead time的时间,再去打开上管。此时下管的体二极管在dead time时间内续流产生的损耗以及反向恢复时产生的损耗。

1 p( z! r# U6 i( b! ?

j2iqub44mwm640223911.png

9 x9 y& y) ]8 [1 Z

9 x9 y& y) ]8 [1 Z

体二极管存在导通压降和电流,这部分会产生损耗:4 H& s. O& V# }2 c+ k9 Z9 B

还有反向恢复损耗:% p* m( m2 O# {$ I6 p5 ?+ U! G& i

jxwtghd4vyw640224011.png

0 m E+ }1 u E7 z6 Z; ?电感损耗, z' Z0 x" ]- d$ e1 g' e

a、线圈损耗

' |* J* ~. W8 K. Y由电感直流电阻DCR产生的,输出电流经过DCR,损耗以热量的形式表达。

X: w1 y1 o. b+ K5 L) i! z& t% s

l1ftunjdadq640224111.png

4 |9 X# \1 e# V# w

4 |9 X# \1 e# V# w

线圈损耗可以用如下公式计算:

; ?2 X9 p! w( k; ?2 N# {$ R3 R

pirun00vgox640224211.png

% s+ d v1 B4 Rb、磁芯损耗" G, C6 D" K6 j+ r

磁芯损耗跟磁芯材料相关,很难计算,需要联系电感厂商获取。一般来说,频率越高,磁损越大。

& y b) U; c' A* ^4 x+ H损耗总结- ^+ X3 K+ a" ~# }( ?- F

在网上找到一个比较好的图。

! K5 R! m" V- k2 E0 E& ^+ i

nccvnvd1fwy640224311.jpg

- a* ~2 d$ ^8 h# X9 C8 L5 V

- a* ~2 d$ ^8 h# X9 C8 L5 V

5 s' x1 E# O4 `0 o9 h 6 v2 c; n; D3 p4 h3 q 6 v2 c; n; D3 p4 h3 q

开关损耗跟开关频率和栅极电荷Qg有关,而导通损耗跟Rdson有关。 Z+ D$ r/ ?' {

一般来说! x3 L+ g# A. ?" \1 w& q

High Side MOS 开关损耗大,导通损耗小

" a* v7 L p' r* D/ ILow Side MOS开关损耗小,导通损耗大。

q1 _; {7 X, I7 r9 Q, e总结' |) o- x& w# ?6 V) a

DC-DC BUCK电路,研究透了发现非常有意思,一开始看山是山,然后看山不是山,最后看山又是山,相同的东西,给自己的感觉完全不一样。( H4 Z! i9 p1 }

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。原文链接:https://blog.csdn.net/weixin_42107954/article/details/131000253写在最后都说硬件工程师越老越吃香,这句话也告诉我们硬件也是需要积累的,王工从事硬件多年,也会不定期分享技术好文,感兴趣的同学可以加微信,或后台回复“加群”,管理员拉你加入同行技术交流群。! e* L' P: e' b5 h% S' U

推荐阅读(点击图片直接进入). h# w7 S+ L* K3 D1 S" {* u

6 M! s* ]- ^+ K' [1 ^, O- q6 o5 } 6 M! s* ]- ^+ K' [1 ^, O- q6 o5 }

# A. Q2 `! Q3 w4 Q! ~5 r # A. Q2 `! Q3 w4 Q! ~5 r

2 A3 }: U0 p6 Q" c3 k

/ `1 r5 c" j" Z% l+ q. ]投稿/招聘/推广/宣传/技术咨询 请加微信:woniu26a声明:+ J& {2 y2 \: ]! C F6 g, C

声明:原创文章,转载请注明出处。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。推荐阅读▼

) F+ }2 |/ V% T# ]! Z& o电路设计-电路分析- }$ {; t D( c/ z+ \8 M) e, B' I

emc相关文章

0 G$ S, Q0 g- ^' S电子元器件

' o, x# m" v5 x' q |

|