之前发了ESD 的仿真模型,应兄弟们的要求,这期来个Surge的仿真吧。 先来第一步,我们如何判断我们的仿真模型是OK的,是符合要求的?显然,这个要想有说服力,那必须查标准。

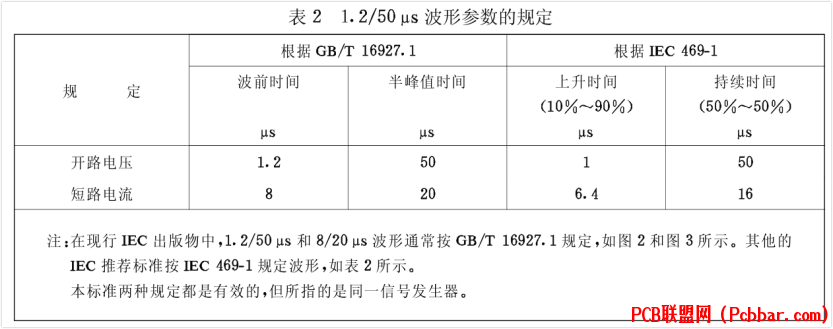

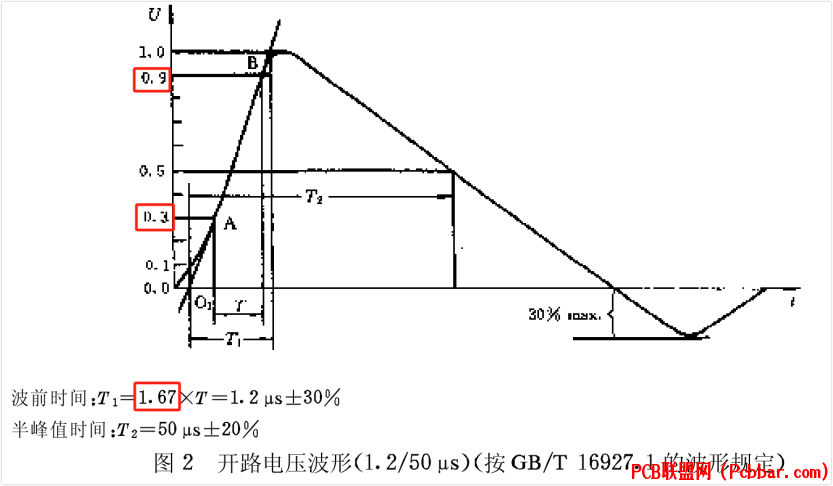

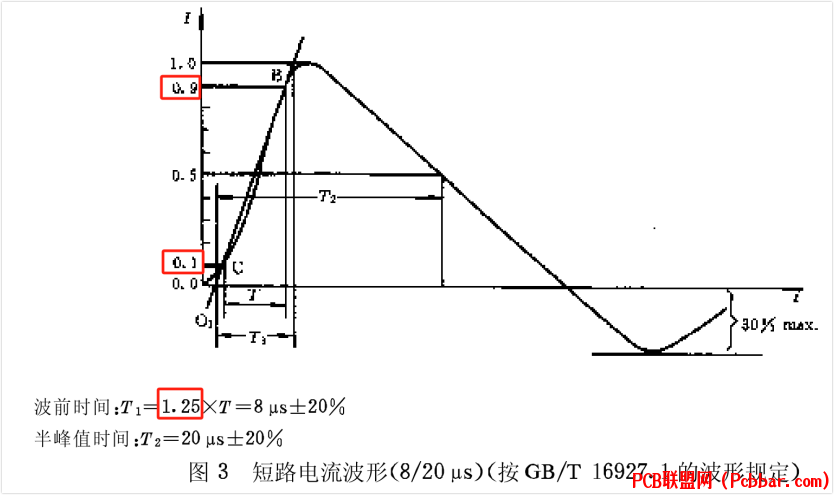

浪涌标准波形 从标准文件《GB-T 17626.5 《电磁兼容试验和测量技术 冲击(浪涌)抗扰度试验》》查询知道,常规的浪涌波形,其开路电压和短路电流波形参数要求如下:

4wdtwtpojc36405858539.png

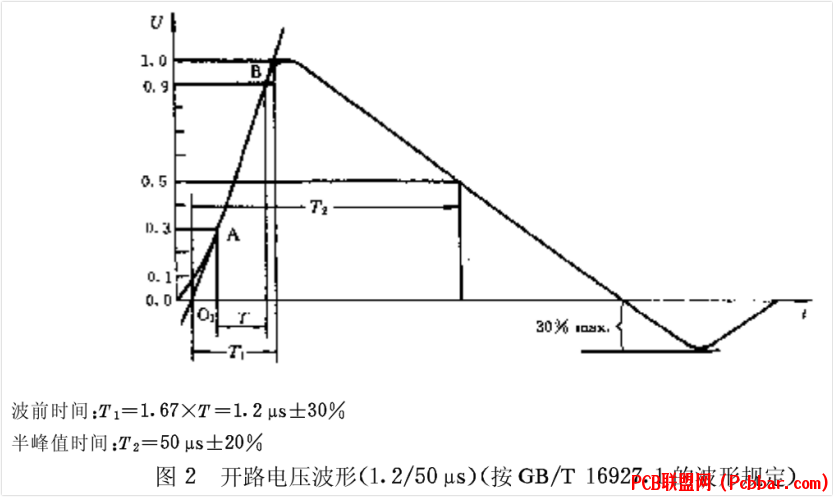

可以看到开路电压波要求波前时间/半峰值时间为:1.2us/50us;短路电流波形要求波前时间/半峰值时间为:8/20us。 开路电压波形:

kew0fjz4wwh6405858639.png

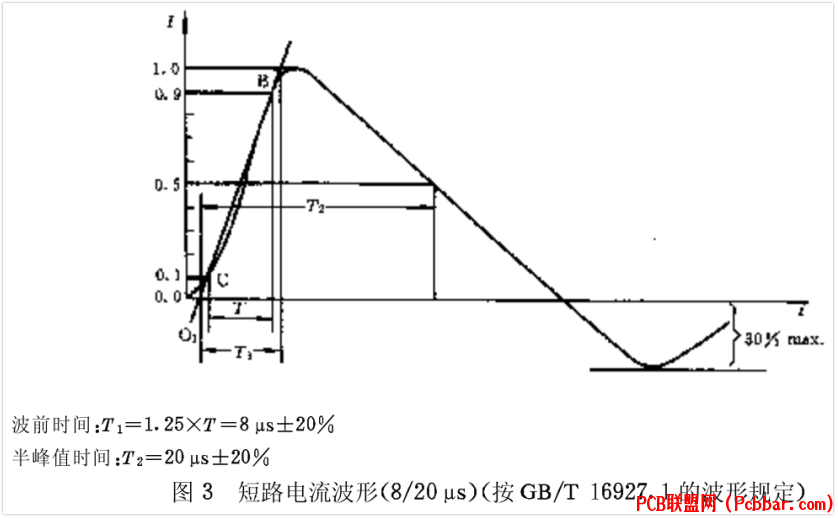

短路电流波形:

21joaxvrp226405858739.png

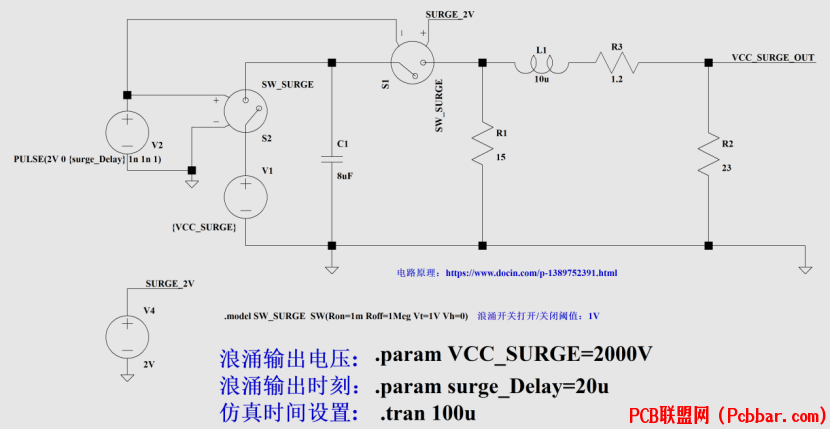

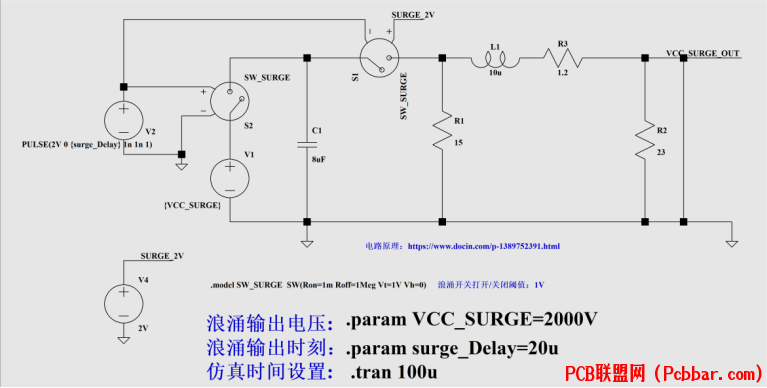

仿真模型 关于仿真模型,我在网上找了一篇论文《2/50μs、8/20μs组合波发生器的研制》,论文原文的链接为:https://www.docin.com/p-1389752391.html 该论文详细介绍了仿真模型各个参数的选择,很详细,因此呢,我就直接套用了。 因为我一直使用LTspice进行仿真,下面就套用论文的参数,使用LTspice进行仿真验证。

仿真电路图如下:

kgdmtdkk4qb6405858839.png

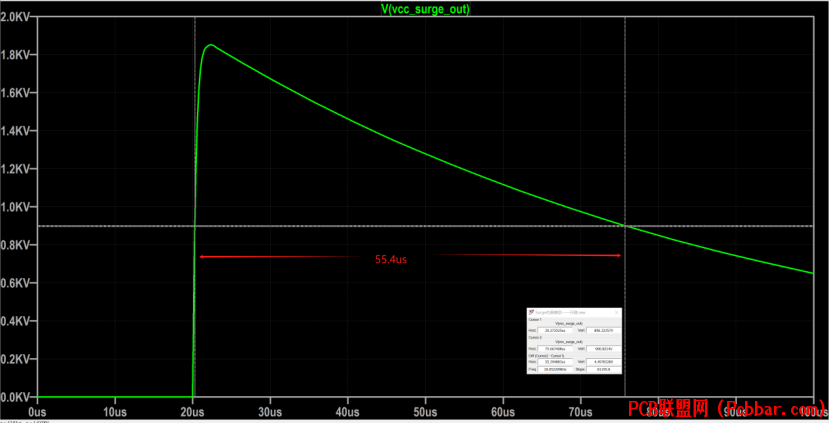

简单说明下,0~20us时开关S2导通,S1不导通,V1=2000V(我设的是2000V,可以修改为自己实际要仿真的电压)给电容C1充电。在第20us这个时刻,开关S2不导通,S1导通,电容C1给后面电路进行放电,即开始打浪涌。 仿真波形验证 开路电压波形 上面电路运行,VCC_SURGE_OUT电压波形峰值为1.85kV

l1v5tugdfhr6405858939.png

从规范图可知,电压波形的波前时间为峰值的30%~90%时间的1.67倍

z3vwh51ckmb6405859039.png

从上图知道,30%~90%的时间是738ns,所以波前时间T1= 738ns*1.67=1.232us,满足规范里面的1.2us±30%的要求。 半峰值时间为55.4us,满足规范50us±20%的要求

q4couthaxli6405859139.png

开路电压波形我们知道符合了规范的要求,下面来看短路电流的波形是否满足要求。 短路电流波形 我们将上面的仿真图的输出端短路

xpu0lv4dw3k6405859239.png

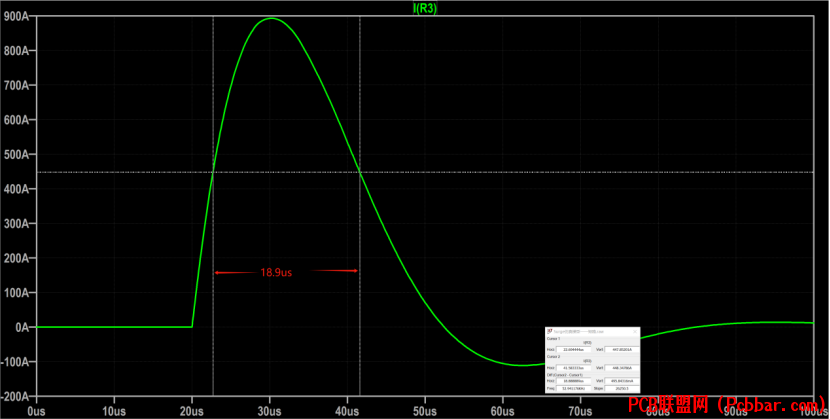

运行下,测量R3的电流,R3的电流即为短路电流波形(因为R2被短路,电流为0) ,如下图:

gulccd3uzuf6405859339.png

同样我们看下短路电流波形的波前时间和半波时间是否满足规范里面的要求:波前时间:8us±20%半峰时间:20us±20% 由规范知,短路电流波形的波前时间为峰值电流的10%~90%时间的1.25倍。

50or0chuvyz6405859439.png

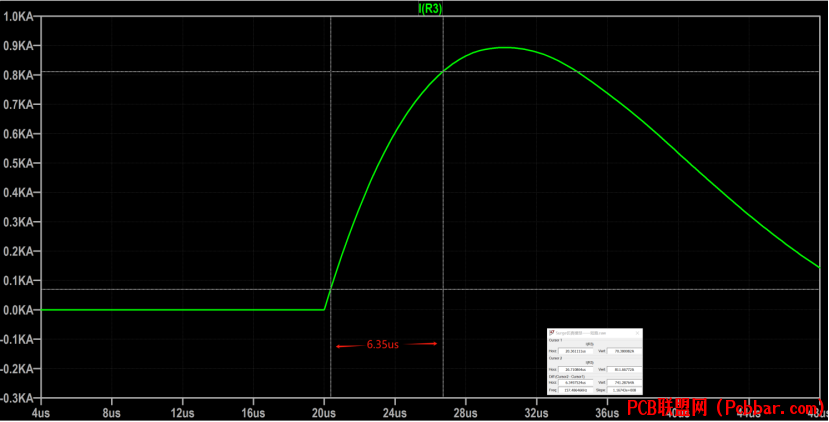

从下图可知,短路电流波形从峰值的10%到90%的时间为6.35us,那么波前时间为:6.35us*1.25=7.93us,满足规范要求的8us±20%的要求

aihdpyuzs546405859540.png

半峰值时间为18.9us,也满足规范20us±20%的要求

yjnb4uibfuk6405859640.png

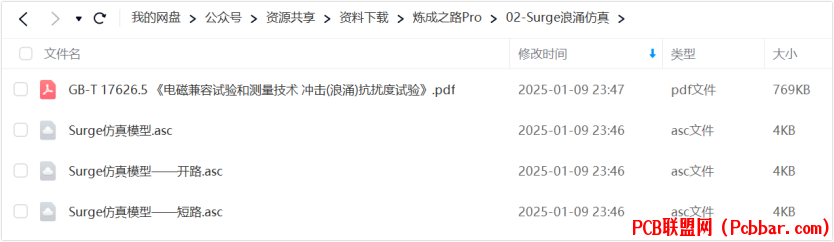

因此,构建的仿真模型整体是满足规范要求的。 仿真源文件下载 仿真文件我放置到了网盘,有需要的自提。下载方法:关注我的微信公众号“硬件工程师炼成之路”,在后台回复“炼成之路Pro”,就可以下载了,放置在目录:炼成之路Pro-->02-Surge浪涌仿真

4vawvqp424v6405859740.png

声明:以上内容仅是个人观点,不保证正确性,如有问题,请留言指出。

推荐阅读:

1、还在用CAM350吗?

2、我写的东西都在这里了

3、没有接地的产品,ESD放电测试时地回路是怎样的?

4、ESD保护layout指南

5、为何Layout时信号走线要先过ESD/TVS管?

6、如何理解虚无缥缈的ESD

7、ESD如何仿真?我找到了ESD仿真的模型 |