|

|

引言

* }# ^9 E- r w* n( r

8 \& M2 K) G! s; R: S随着人工智能技术的快速发展,计算能力需求显著增长,尤其在边缘计算设备的实时处理需求方面。本文探讨异构计算平台的发展历程,着重分析骁龙平台在高效能人工智能处理领域的技术创新[1]。

: j9 m: p; H g/ @7 n) y) g

cud05e1zasl640346214.png

: [" M, B- ~8 L& K' M人工智能计算需求的演进

: n' E: Q; q$ e7 j! K* L% ?6 a& l

( b$ }0 `% U. s" Y5 H8 N' W4 P4 \9 {% N& ~

r1cz2bk32zl640346315.png

, b5 F' {2 [+ b! t. a图1展示实时推理需求(TOPS)与人工智能模型参数数量的关系,显示处理200亿参数需要约100 TOPS的算力。

* L7 G6 }, E# E( u3 P/ P6 m T M. Z, T! B7 k. d& D6 |3 `) J

在当前阶段,设备端人工智能处理每十亿参数需要1到10 TOPS(每秒万亿次运算)的计算能力。随着模型复杂度提升,边缘设备预计需要高达100 TOPS的运算能力,用于支持不超过200亿参数的模型规模。

6 ^3 }- g% {; {- u

rdj245fexes640346415.png

$ `1 i) ?' N' s: V/ a+ R图2呈现自2011年以来,边缘计算在实时推理方面的性能需求增长了500倍,这种增长主要源于各类人工智能应用场景。* g( F6 s, H6 r- h1 ^+ M' s# z

& q1 a& G+ U# F

这种算力需求的显著提升主要来自几个关键应用领域:

" K/ W2 c' C5 N N自然语言处理图像生成语音识别图像分类

# _ y* b& _1 X. I/ E, S异构计算架构的发展" T- H8 g! R$ d2 [; g$ N

8 ~2 a# l: Y. h! j! m

a4gjckc11gj640346515.png

[- }; ]+ c, c# N. L) T, }1 j0 j图3展示骁龙SoC中CPU、GPU和NPU三种不同人工智能引擎的计算性能演进历程。

+ d- }3 ^: r' M1 l- A1 v7 }9 ~9 ^1 q5 r0 ]

移动计算平台经历了重要的技术迭代:从早期的通用CPU,发展到专用GPU,再到2018年引入的NPU(神经网络处理单元)。这个演进过程带来了显著的性能提升:

" N8 _: G, d4 cCPU到GPU的转变实现了10倍能效提升GPU到NPU的升级带来额外10-20倍效率提升1 b' N, D" }# `9 a" m; W

" w s5 C" s$ p6 U5 e# c

gixgptkz3lx640346615.png

/ t6 F/ ]( K$ l" J2 G( z5 }3 E图4描述设备端人工智能引擎的能效发展趋势,以及边缘人工智能不断提升的能效需求。

2 v5 _. B- @ ^

3 D$ k( \+ v2 K

0jkaxf1m1zy640346715.png

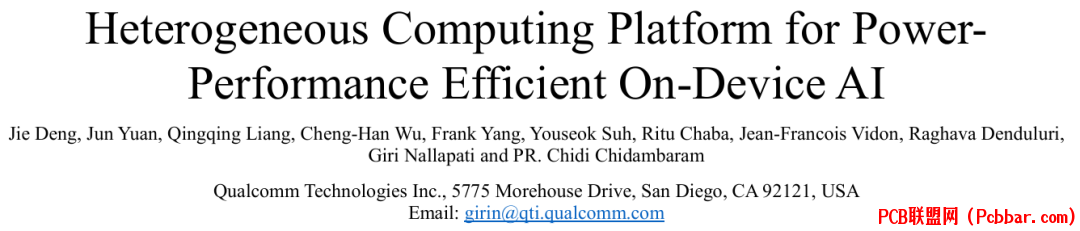

& l6 \4 [8 V8 m7 G图5展现2007年至2024年期间,计算应用多样化与并发执行需求的增长。7 A0 E& B, p; |! U. Y6 }( C

技术创新与系统优化; k' V* b, ~* V4 T+ @ N2 m

! \: z% t( Q" D5 z$ M

22gmuukurxx640346816.png

# d# A$ V- Y3 z: F" A

# d# A$ V- Y3 z: F" A

图6显示骁龙SoC的完整架构,包含NPU、GPU、CPU和传感器集线器等核心模块。

4 r, c' s, q* \- p ]5 v! K- u! J4 ^/ k, `7 l

在提升人工智能处理效率方面,现代移动平台采用了多项创新技术:

5 M6 ?4 f2 b" F2 a! e/ r' U1. Microtile推理技术:将神经网络分割成多个独立执行单元,减少内存访问,提高处理器利用率。

! r1 I1 v- }2 s" ]( H3 v9 Y

gcfe2kreszq640346916.png

% b6 S) ?: R% z. X

% b6 S) ?: R% z. X

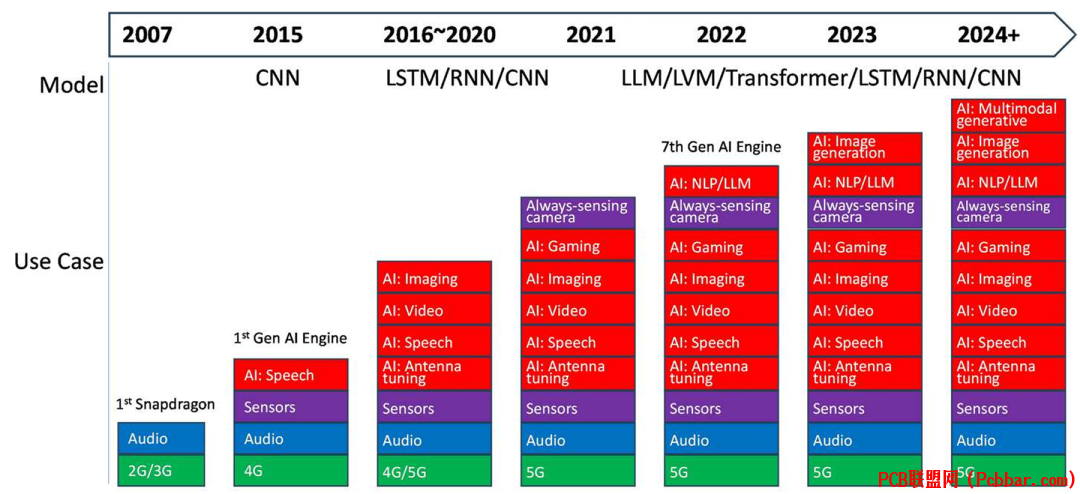

图7展示技术进步过程中器件电容和漏电流的缩放趋势。! p: ~0 N( i9 V+ l! U: \ j4 ^

& t$ O, g# z2 j5 v$ d, A: W/ L

2. 处理单元直接互联:减少对系统内存依赖,提供更高带宽和更低延迟。

" z5 H/ j& x2 \$ L3 B

yegtza3om4v640347016.png

* l* M6 y0 K* a

* l* M6 y0 K* a

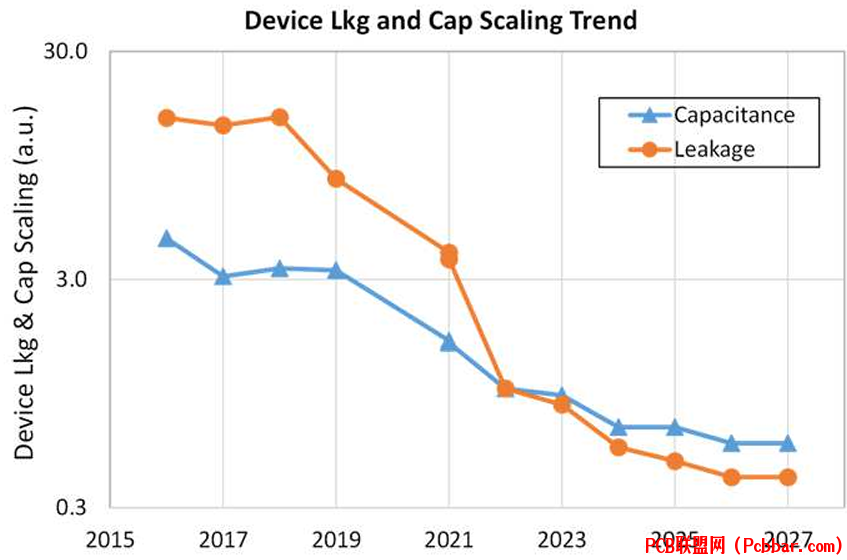

图8展示不同PVT条件下,采用各种阈值电压、结区和沟道微调工艺的器件性能权衡。

* t6 [' ?. V @- h/ D性能突破与能效优化& X6 \) x( `+ o; V2 ~' ~9 [

I& E) ?! V* x+ B" R6 b) `+ S" v$ Y

bvm04fbuz3i640347116.png

3 d6 s. [1 V% L s0 z

3 d6 s. [1 V% L s0 z

图9对比骁龙8 Elite CPU与骁龙8 Gen 3的性能,显示在相同性能水平下可降低44%功耗,或提供45%性能提升。$ x6 M9 k' ^3 v6 T4 l$ a

9 Q" B! o, @' s9 p! ~3 X( |最新的骁龙8 Elite平台展现了显著的性能进步:" h7 G+ u0 E1 B( [7 ~" g

gbm2l4m25o0640347216.png

1 X2 G- _0 z* e4 ?

1 X2 G- _0 z* e4 ?

图10展示骁龙8 Elite CPU在Geekbench 6测试中,单核和多核性能较上代提升约45%。! l! ^# U$ b+ T0 |; S7 i

$ B8 J4 w7 y. P9 B$ {- k) u- ?

5d4oqvvh1gw640347316.png

7 }5 k: P7 M% s3 {0 I图11呈现骁龙8 Elite NPU的计算性能提升45%,同时内存带宽提高超过10%。

, z+ [1 L. m; B6 a8 ?

3 b' k4 y5 B( C# P1 ]' E2 V

xtosq00naq4640347416.png

% v8 o9 V4 A! L/ ]

% v8 o9 V4 A! L/ ]

图12对比AITuTu评分与NPU理论TOPS,显示实际人工智能处理性能较同等理论算力的竞品高出7倍。

+ ~8 \7 o8 ]5 Z- e; G o1 h技术挑战与未来方向

: M1 @6 e" t% l& Y

5 C, h9 F' W% i" I- f) x7 G

zxka4u3qxvc640347516.png

+ u6 V$ {* X% @+ Q9 R8 ^3 ^. D6 v图13描述10nm至1.4nm技术节点间的等成本电池续航时间、性能和功耗变化趋势。

$ v; @* z5 n+ h r- f0 @4 B3 b6 ?, b6 [, I% k0 j$ {

目前面临的主要挑战包括:

- ]9 x- V$ I; a2 B0 n6 b1. 功耗性能成本效率:等设计电池续航时间等成本(BLaC)指标在5nm节点达到最优后开始下降,原因是硅成本上升和每瓦特性能提升放缓。- Z9 }( [2 s0 ^/ x# _" Q0 e/ j: N+ z

xaeycpewe1u640347617.png

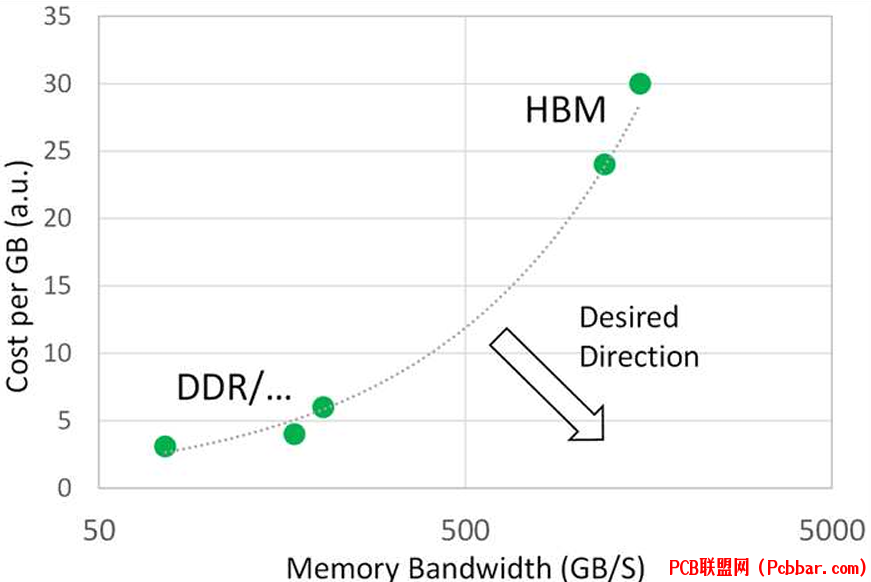

7 P/ i U2 D9 V$ F M% O图14分析标准内存方案(DDR、LPDDR、GDDR、HBM等)的带宽成本关系。/ N' Z) g, b% O; E C- y9 B

7 Y7 U# k0 w5 R+ w! v: Q

2. 内存带宽与成本平衡:生成式人工智能等应用需要高带宽内存,但现有内存方案在高带宽时成本急剧上升,不利于边缘计算部署。0 T5 Q( _! d& Y9 T

) R8 S, i* A! j" |" V$ m这些挑战需要在逻辑和内存chiplet的异构集成方面持续创新,通过先进架构设计和封装技术寻求解决方案。

$ G7 \& Z+ n$ P参考文献

- p. j! I1 c2 l q) H

# \1 y: s8 f7 E7 ~ `3 s[1] J. Deng, J. Yuan, Q. Liang, C.-H. Wu, F. Yang, Y. Suh, R. Chaba, J.-F. Vidon, R. Denduluri, G. Nallapati and P. R. C. Chidambaram, "Heterogeneous Computing Platform for Power-Performance Efficient On-Device AI," in 2024 IEEE International Electron Devices Meeting (IEDM), 2024.

# E* @1 o" d$ }8 ~END, |% u4 {# \8 v

9 _ j [1 f8 T+ t

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。8 h( }3 _- w/ X: O: W' [7 C9 t

点击左下角"阅读原文"马上申请9 T# N. n- ^1 W7 J* c! d

9 x3 S' ?* {3 ]+ i欢迎转载

( j' }* ^* e# H d2 l

% {# f7 I# Z/ y. u8 u' c) j- P4 Z转载请注明出处,请勿修改内容和删除作者信息!

' i: F" _# `7 d, J

' q2 p2 H8 `3 \: d6 r* ~

; p, x# ^1 l& a9 @2 t C" X- z2 f) c% {/ j( }# r+ b2 ?

axgvamt54fw640347717.gif

# T. j0 Y6 M1 A7 |" d3 M {, h/ O- D5 K4 s% M7 I

关注我们8 p! z. b+ U* S2 ^$ W7 T5 X

% s$ h }- _9 d

+ x. q3 C7 y& o8 c* N ~9 q

ru325gfz1bw640347817.png

7 l( U% I, s6 w$ n |

. M; x3 l0 A' @7 Q4 ~

mqs0u5ogke3640347917.png

$ I$ @% o- h, ]6 f" t. U: D | 0 B( ~, `. }5 @7 [, G: _7 r+ |. T

vtzrilusgpl640348017.png

! Y# G. i: w* L& e1 x" A

! Y# G. i: w* L& e1 x" A

|

: l- k* i! O* }, }, a @- D% k, [' ?+ j R

3 ~$ s; [0 b; [/ r( K

" E4 G2 [, c" b! F: q( u# g关于我们:* }6 ~3 ^ E9 C$ t3 t8 ^

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

* a) d* N% f3 P+ ]

$ \6 {9 q' D0 d3 shttp://www.latitudeda.com/

# l2 o0 N6 I" x(点击上方名片关注我们,发现更多精彩内容) |

|