|

|

引言

3 j' O% o. E3 }1 ]" M1 t& r随着人工智能(AI)的快速发展,现代数据中心对光互连组件的需求不断增长。目前,业界正在将SerDes(串行器/解串器)技术推向200Gb/s每通道,以满足这些日益增长的需求。本文探讨了一种创新的异构收发器架构,该架构解决了高速光通信中的关键挑战[1]。

! Z- U2 L+ _& o% z5 H$ o6 L

xse0yvpcgvj6403795348.png

/ X( L* H7 X+ L9 L+ Q# t% o* \+ N, K

/ X( L* H7 X+ L9 L+ Q# t% o* \+ N, K

+ J/ N$ i) F3 D: y) d. G6 m' j

19 w* _8 i) C4 o

可插拔光学解决方案简介

2 _3 g* Y0 [7 A& ]AI技术的快速发展为数据中心的数据传输速度创造了极高需求。当前的光互连解决方案在扩展到200Gb/s每通道时面临重大挑战。目前主要有两种方法:% [$ E7 }) Z" q0 F

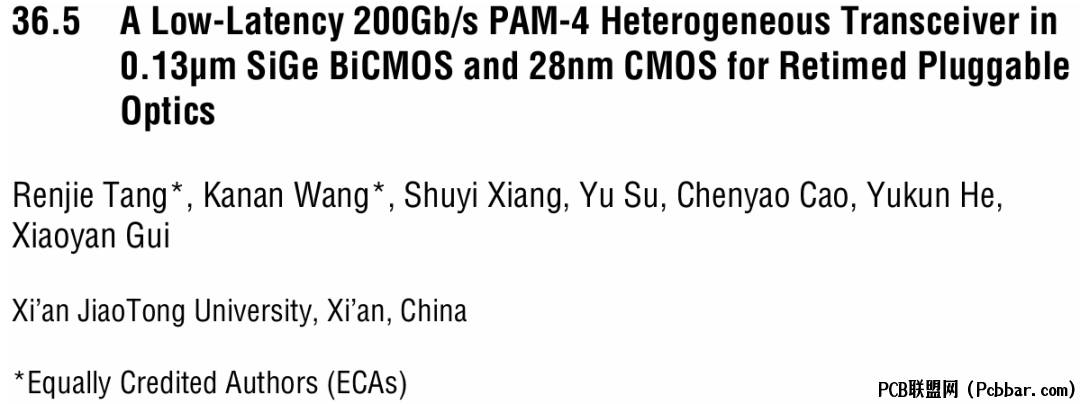

" f# R& G! t( O$ _线性驱动可插拔光学模块(LPO)由于其优越的能源效率,在100G/通道传输中获得了广泛应用。然而,当尝试扩展到200G/通道时,LPO面临可靠性问题,因为极短距离(VSR)电通道的插入损耗(IL)会显着增加——当数据速率翻倍时,大约增加14dB。1 E% E. `3 I( ^$ w0 H

* x" S. [' i. U! Y$ C8 h, z

另一方面,包含数字信号处理器(DSP)的重定时解决方案能够处理更高的插入损耗(约30dB),但会引入显着的延迟。这种延迟与对时间敏感的应用(如AI推理)不兼容,在这些应用中,毫秒级的延迟可能产生关键影响。1 @' f) H8 N+ ~4 ]6 ~

- q' ^6 z' T x; _* G本文探讨的异构架构提出了一种创新方法,使光侧能实现200G传输,同时避免电通道插入损耗加剧的问题。这种解决方案通过非ADC架构实现更低的延迟,同时保持与重定时解决方案相当的能源效率。

1 p% a$ k- w( S

- V. C1 ]! m6 ]( j/ c24 h: v3 d K3 P" }0 ^; K8 w) r* [7 o

异构收发器架构

2 {' n5 N1 e' w, T4 @% @异构收发器代表了一种新颖的方法,结合了两种不同的半导体技术以优化性能:0.13μm SiGe BiCMOS和28nm CMOS。这种混合设计允许在最有益的地方应用每种技术的优势。1 z1 p- c* u- k# G5 U

9 z7 D d- c F2 Q* f

论文中的图36.5.1显示了三种不同的光互连方法:! m4 X: f7 w2 E' T

(a) LPO解决方案,适用于100G但在200G时表现不佳 1 T7 V$ e, m% W+ B( o

(b) 带DSP的重定时解决方案,增加了延迟

) U, Z' S; j; {# M6 v: |(c) 提出的异构解决方案,结合了两者的优点

# h- o$ A, z, H( b0 _+ d+ E

qxpfecxailb6403795449.png

x% c& E" V( T7 T1 r; V图1:(a) LPO解决方案;(b) 重定时解决方案;(c) 提出的解决方案

/ T3 ?* ^, R% _2 J; V

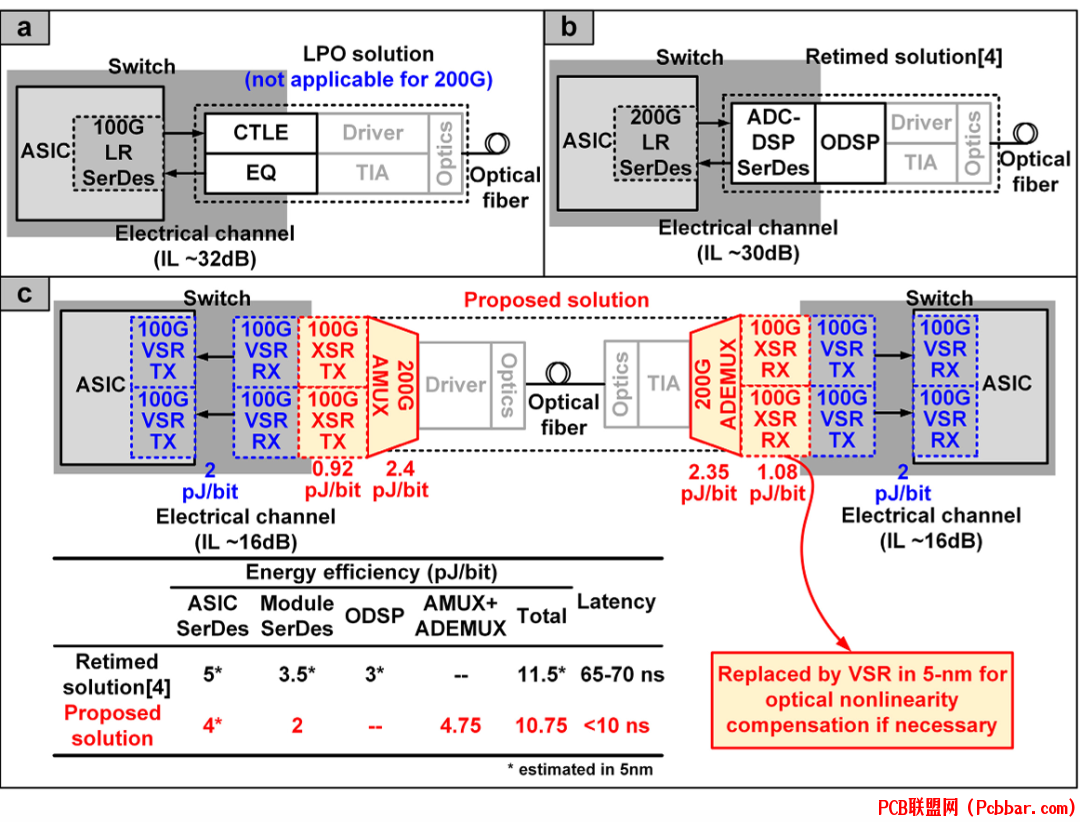

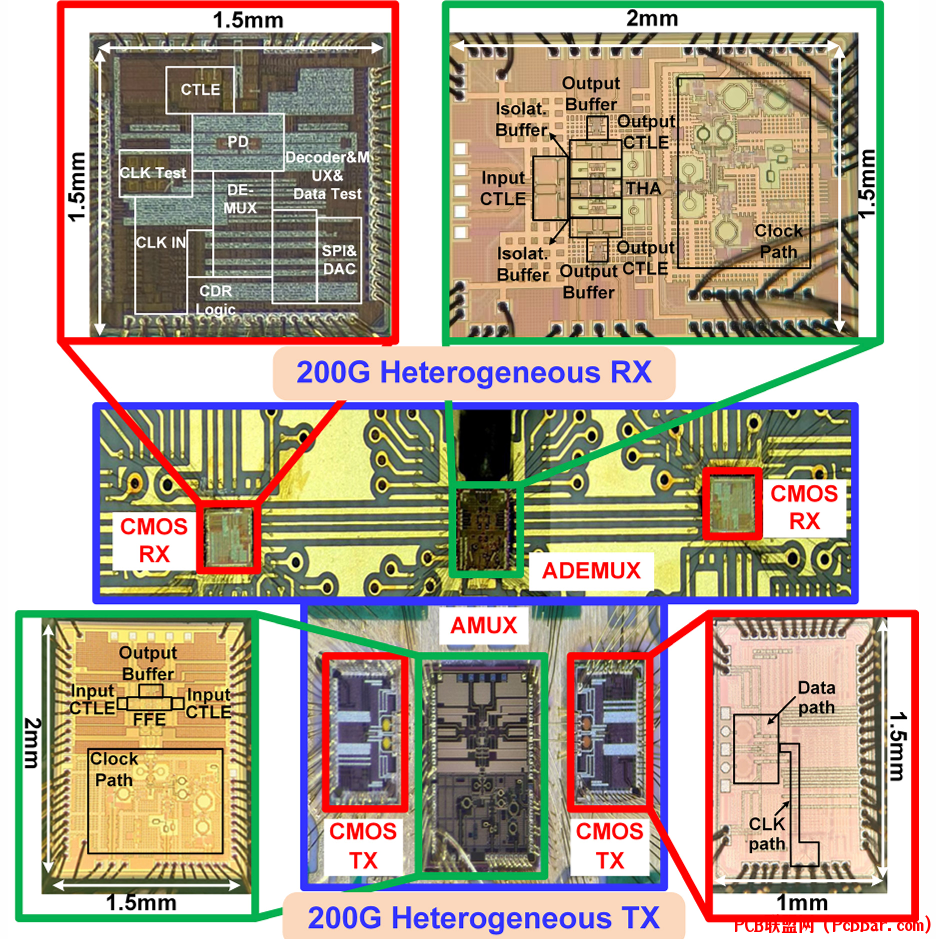

4 i. j( {! L% B: ]该架构包括200Gb/s发射器(TX)和200Gb/s接收器(RX),每个都采用两种半导体技术。" S' l6 E. J9 W; _

eqkdjzxl4n06403795549.png

, V: \/ L) Y. n" L图2:200Gb/s收发器的发射器和接收器部分的框图。左侧显示了发射器架构,右侧显示了接收器设计。

' K$ k* [0 B- e$ R$ J- Z7 R: a0 L' `5 \4 r& \' D: f& F# N, w

3( r% J- z& i* W' [$ i; J( t t

发射器设计与实现

Y# v: I9 Y" {) r5 y H200G发射器由130nm SiGe BiCMOS制造的200Gb/s模拟多路复用器(AMUX)和28nm CMOS实现的两个100Gb/s PAM-4发射器组成。这种异构方法充分利用了每种技术的优势。

; T$ Z$ [5 `- X0 g/ i4 K( y9 ?) Y, l# ^! \1 E

% _6 b6 f4 q. y9 ? w' l在100G TX中,设计包含:3 j, ?! U- L; R7 s7 D/ g) S

PRBS-Gen用于测试模式生成9 S% P6 C- G# Y) |

8:4多路复用器和重定时线路

/ e& V7 |$ ^. N% _- d8 Y10段前馈均衡器(FFE) w: Q, I8 \3 R x+ L1 g. h

精细调整的低功耗准电压模式(QVM)驱动器' f* M6 w- L% R/ q9 a- b h( _

$ g4 z7 `+ O: H; O! ?一项关键创新是采用3抽头分数间隔FFE方案,用于锐化眼图,同时为200G应用提供50GHz带宽补偿。从TX传来的两路100Gb/s数据(延迟0.5UI,即10ps)通过传输线和CTLE,然后由带有2抽头FFE的MUX核心聚合为200Gb/s。

. {% S/ w+ U' d4 D' I# r3 w0 h, d& p6 p1 f! u6 g2 x8 R3 u

设计在CMOS TX的时钟路径中集成了4级可变延迟缓冲器,使100Gb/s数据的相位可变化,覆盖超过0.5UI延迟(12ps),通过每级3位可变电容阵列实现亚皮秒分辨率。- ]" q V7 W, z+ I; z

nxvggcyg5kw6403795649.png

" i/ M" A9 b1 Z5 Y

" i/ M" A9 b1 Z5 Y

图3:200Gb/s发射器中采用的设计技术。该图说明了各种方面,包括QVM驱动器设计、RZ数据生成和输出缓冲器实现。$ t# n& g; b* B) q/ p4 J5 O

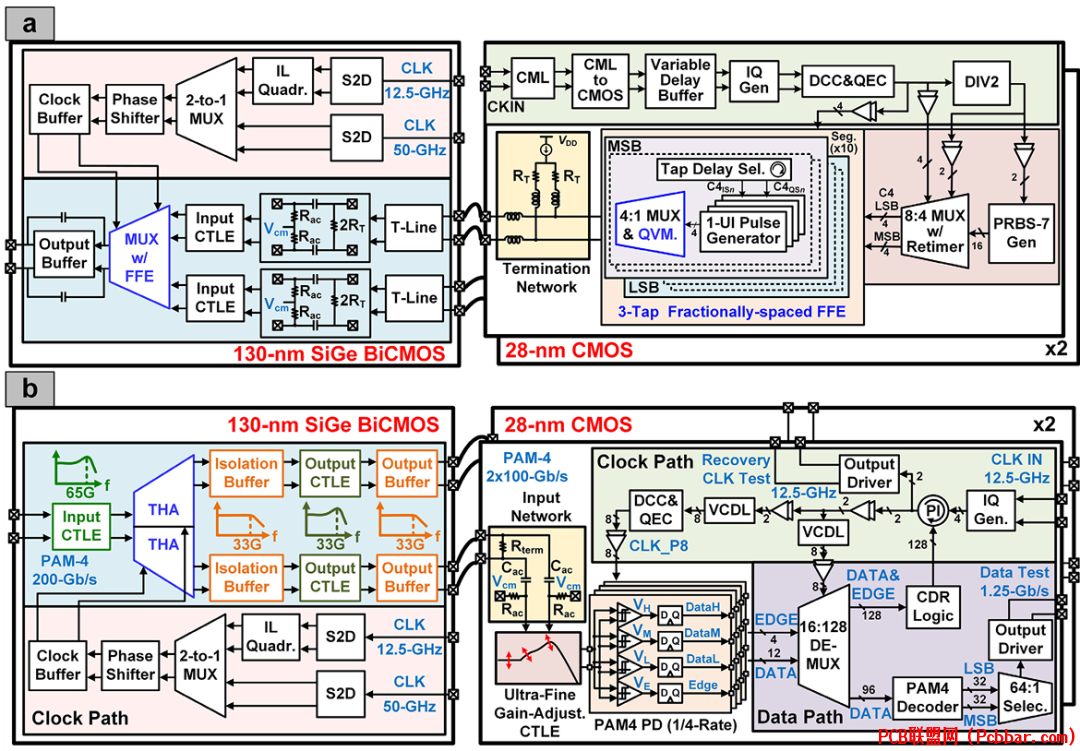

: s+ f3 y. N: x+ o" C8 u5 jCMOS QVM驱动器相比传统方法提供多项优势:

- \, s' B/ V- A# s2 e比CML设计减少30%功耗

8 G# i- q+ U1 {* l/ H9 e5 l高电压效率

1 [- y+ J- f* N, W& N超精细线性度调整,分辨率优于0.5%

: R2 R* C% n% y% }( e! XRLM(相对电平不匹配)调整范围从84%到100%" `% m7 V; y! ~ a8 b; M

& g7 l- w# G# e3 y- `' V8 ^1 X- ~

这种精细的线性度控制对补偿调制器驱动器和光调制器在实际应用中引入的非线性至为重要。

- O" v6 [0 v9 A7 M1 W" F- t. o) d

: z5 N9 `- `8 Y$ ]4* V9 D# E' G( O" t$ A! C! X

模拟多路复用器设计

" Y2 W0 g5 A+ z! ^8 A" c基于归零(RZ)数据生成和求和的新型AMUX架构构成了发射器设计的核心。当RZ单元中CKP/CKN为高/低时,VOP/VON跟踪输入数据信号VIP/VIN;当CKP/CKN为低/高时,VOP/VON返回共模电压,产生零差分电压。! T, @- a* Q3 Y- |

6 V0 F4 r4 ]3 ]8 V& O0 H采用并联电感峰化技术加速RZ稳定,并将零宽度从2.83ps扩展到4.96ps,增幅达75%。通过这种方法,主抽头RZ数据D1M和D2M分别通过采样时钟的相反相位从RZ1和RZ3提取。类似地,通过在RZ2和RZ4中反转采样时钟的极性,获得具有1-UI延迟的post1抽头RZ信号D1P和D2P。' P0 K+ M% g5 u

# u6 r' b7 l( P4 Q- ^7 b; s9 B具有0到11.2ps(>1UI)可调节延迟的相移器通过将时钟边沿与数据边沿对齐实现FFE抽头生成。两个Gm单元从四路RZ数据产生全速率主抽头和post1抽头数据,抽头系数由Vbp和Vbn之间的电压差确定,而20Ω负载电阻作为电流求和器。! I* Z- D4 t" B9 ?" o& G$ P

) E! J1 H, M0 ^7 k V与先前设计相比,具有2抽头FFE的AMUX减少时钟功率需求约12%,同时减轻时钟驱动负载,与替代方法相比,时钟功率减少约35%。

1 z, x, M! A5 l% C: C* D$ t: e

emwhrzdsksm6403795750.png

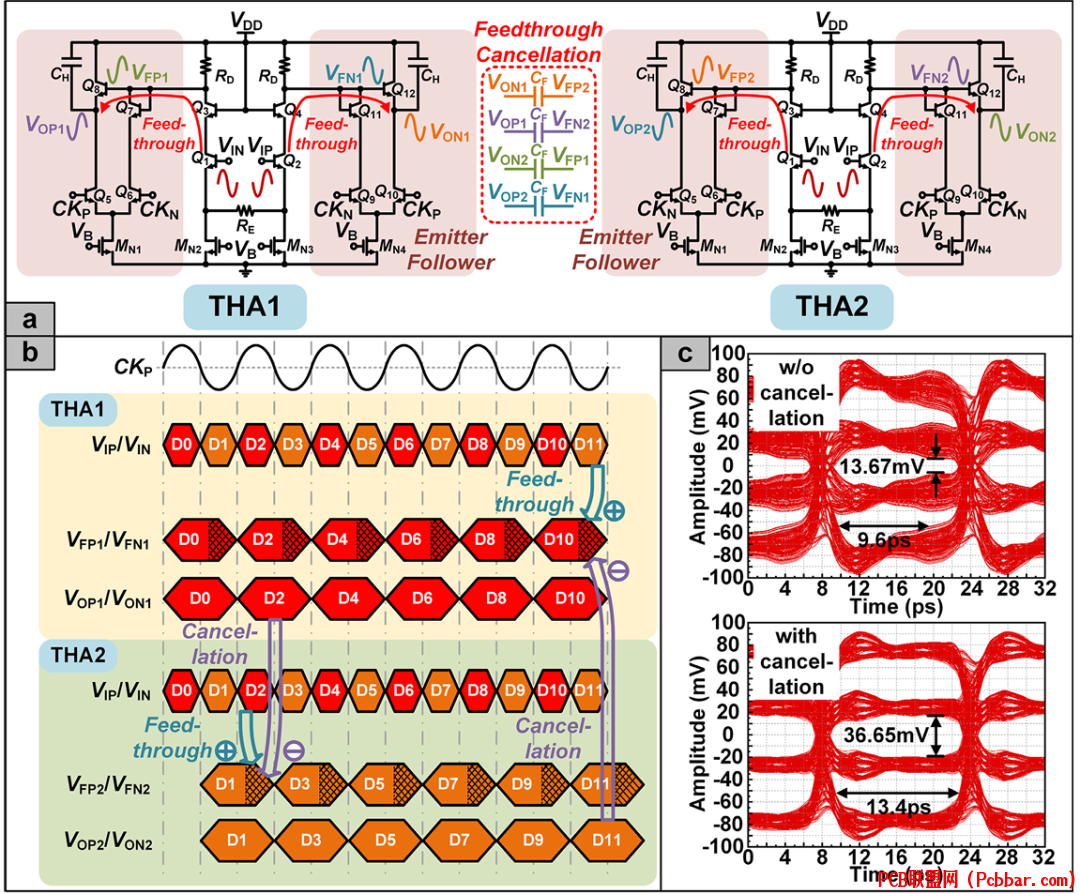

' E3 p7 {8 b. P图4:跟踪保持放大器(THA)的原理图和时序图。该图显示了模拟解复用线路的详细操作及其交叉馈通消除技术。

2 I4 z' H! b2 t5 }1 u7 b+ C2 ?- I, A: W

5. D4 b* d; A) N# ?+ K0 T

接收器架构

8 O3 H7 S. o- z0 s5 [3 S异构200G接收器由130nm SiGe BiCMOS制造的200Gb/s模拟解复用器(ADEMUX)和28nm CMOS实现的两个100Gb/s PAM-4 RX组成。ADEMUX将200Gb/s PAM-4输入数据下转换为两路100Gb/s PAM-4数据。

. g! x4 Y; Z( M" A) k

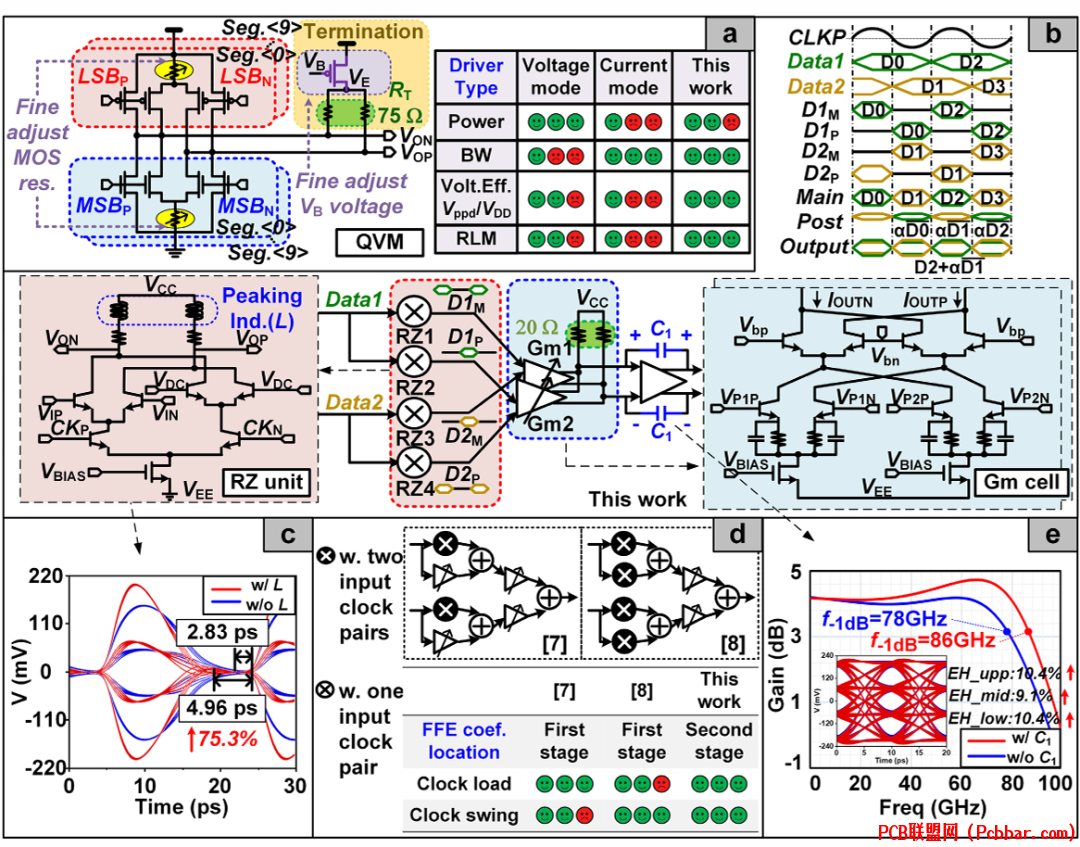

5 B5 y; Z- [1 @ADEMUX的核心线路采用两个跟踪保持放大器(THA)。当CKP为高时,THA1在跟踪阶段运行,Q5/Q10开启,Q6/Q9关闭。当CKP转为低时,VFP1/VFN1被拉低,保持电容CH在保持阶段保持VOP1/VON1的电压。

8 r9 _+ w0 S9 L: A8 Q1 t0 m7 X) A6 V; J6 }; B0 b

此设计的一个重大挑战是馈通路径,在VOP1/VON1引入不需要的数据。例如,在THA1中,D11影响VFP1/VFN1处D10的保持阶段电压,从而影响解复用输出数据。为解决这个问题,引入了馈通消除路径,通过从THA2的输出向VFP1/VFN1提供负极性的D11来抑制馈通噪声。4 ?( O3 i$ I, K/ _ B3 a1 F

8 K7 }/ A3 V# C$ P; D这种交叉馈通消除(CFC)技术显着提高了性能,如测量结果所示,眼图高度提高了2.68倍,眼图宽度提高了39.6%。

f3 m) d0 g: @& v6 N

. g9 f& X( Q" u: l9 kADEMUX接收50GHz外部采样时钟,也可通过片上注入锁定四分频器从12.5GHz恢复时钟生成,由2选1时钟多路复用器选择。如需要,系统可配备50GHz片上低抖动清洁锁相环。可调节延迟超过1UI的相移器确保THA中数据和采样时钟正确对齐。" ?( P* a: g2 G& q L3 K

2 m: [, l1 n% C% y, ^# p: @* uTHA前后的输入和输出CTLE提供约6dB的中等通道损耗补偿。100Gb/s PAM-4解复用数据由1/4速率混合信号RX恢复,具有2ns低延迟和1.08pJ/b的最小功率效率。* q" ^& S4 U+ _' F: |. f

5 v3 W1 t& d$ P

6

( [0 Q& F+ G1 W& ?性能结果和测量

& e$ H6 l9 P& |0 G2 X) j% ~2 [

obz1xbj34su6403795850.png

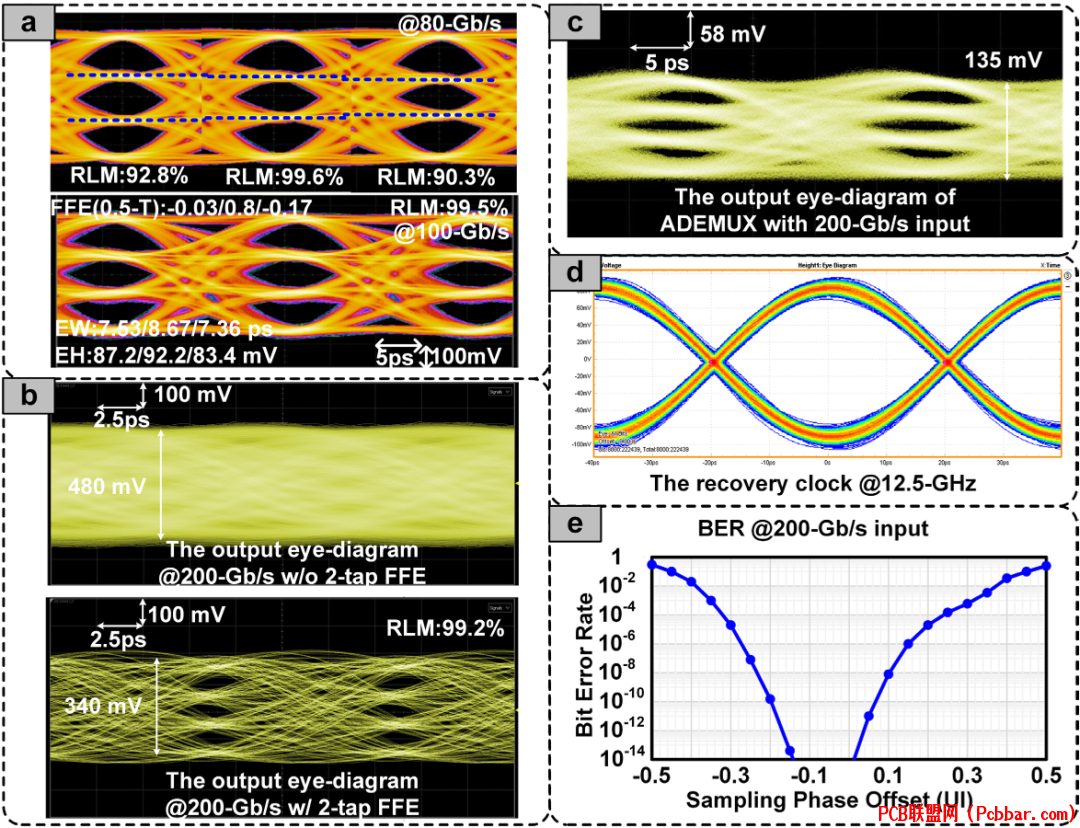

' e0 ?3 j: ?* g0 h% k [图5:200Gb/s收发器的全面测量结果。该图显示了眼图、恢复时钟抖动测量和BER曲线,展示了系统的性能。' m. O' e8 i# a, j! W8 I

! i: f+ X; I! n' ?8 ~: ^200G收发器总功耗为1350mW(TX:664mW,RX:686mW),28nm CMOS供电0.9V,130nm SiGe BiCMOS供电3.3V。测量结果展示了令人印象深刻的性能: R' z# b5 d& R7 V

独立100G CMOS TX在80Gb/s时展示RLM线性度优化从90.3%到99.6%,证明了光链路线性预失真能力

$ U& V* s" ]) R, G8 u. ]使用0.5-T间隔3抽头FFE在约4dB通道损耗后实现了RLM为99.5%的宽开口100Gb/s PAM-4眼图4 _7 }. \9 j0 M* ~" R% V

通过启用2抽头FFE成功打开200Gb/s PAM-4眼图,在约6dB插入损耗后输出摆幅为340mVppd* w8 |/ F3 h6 g3 W8 D# R; K/ Z% g

恢复时钟测量显示出色的抖动性能,随机抖动为328fs,总抖动为5.7ps8 D% M4 T, x; E$ n; ?3 V7 a+ J' J; ~

使用PRBS-7模式的200Gb/s PAM-4输入BER测量显示BER=10^-12时水平开口为0.2UI

0 \0 H1 p9 F5 Q; H# h4 m, N% P ?2 W: O& f

zaj2zdrmq556403795951.png

- g! d5 F5 k! b' ^- S图6:200Gb/s收发器的芯片照片。图像展示了发射器和接收器芯片的物理实现,突出了SiGe BiCMOS和CMOS技术的异构集成。

" V/ j& ^2 F- A0 F3 M# V" x9 N# |

# O' i0 y1 t2 m- |% x7

+ X3 x/ s6 o( ~8 P9 Z7 N" [- p功率效率和延迟优势

* `+ y3 c( D6 \& e8 M* t5 E异构设计的一个特别吸引人的方面是功率效率。提出的解决方案实现了10.75pJ/b的能量效率,优于消耗12.69-13pJ/b的同类重定时解决方案。这代表了约15-17%的能源效率提升。* l& O+ G& { X/ w0 w- V

! w0 ^8 k; U# Q# x更重要的是延迟优势。传统重定时解决方案引入65-70ns的延迟,而异构方法将其减少到10ns以下——对于延迟敏感的应用如AI推理而言,这是至为关键的改进。

) [5 \. V7 a' D) i+ S

: S1 k- U' o. _: o8

$ w/ N0 |. m: I1 p) F结论 ~- _# c. d$ R( b$ G

本文介绍的异构200Gb/s PAM-4收发器展示了一种平衡带宽、功率效率和延迟竞争需求的高速光互连新方法。通过结合0.13μm SiGe BiCMOS和28nm CMOS技术,该设计利用每种技术的优势克服了传统方法中遇到的限制。

* a8 S) C9 ~* t E2 E# a$ w) v8 i

这种创新架构实现了200G传输,避免了基于DSP解决方案的严重延迟损失或线性驱动可插拔光学在如此高数据速率下面临的可靠性挑战。通过全面测量验证了收发器的性能,展示了优异的眼图开口、抖动性能和误码率。

* o$ Q8 F0 p( @0 d% m

- a/ a/ m2 L$ t, B6 L) ]) |随着AI和其他数据密集型应用的持续增长,这种异构方法在满足下一代数据中心的严格要求方面可能变得越来越重要。这项工作代表了实现实用200Gb/s光互连的重要一步,能够支持未来计算基础设施的带宽需求,同时保持时间关键应用所需的低延迟。

A. z# r6 m, R1 G% N( I% D( Z% _2 c0 b" H: n( \ l" i. k

参考文献; v7 w: X% D% c( y/ f2 B

[1] R. Tang, K. Wang, S. Xiang, Y. Su, C. Cao, Y. He, and X. Gui, "A Low-Latency 200Gb/s PAM-4 Heterogeneous Transceiver in 0.13μm SiGe BiCMOS and 28nm CMOS for Retimed Pluggable Optics," in 2025 IEEE International Solid-State Circuits Conference (ISSCC), Feb. 2025, pp. 594-595.

( j( K7 @2 Y& x2 n n" gEND

8 e$ g1 x1 a: q& P

+ {2 {! D" r8 u7 z! ?0 H软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

; N+ [* d" o; l" O1 o& L B点击左下角"阅读原文"马上申请$ d6 t" o0 ^0 ]* M, o' `. K7 i4 u

! F3 T8 O' I1 W4 Z欢迎转载/ I' H: G$ z' I6 k% C6 \7 Y

( G; ^' B( K* d! G转载请注明出处,请勿修改内容和删除作者信息!+ F# D: X7 v6 r" O! L+ n

5 s" \5 i" I# M% v6 x3 p1 W4 D2 @

) ^: R: {/ N2 Q* s- j% L9 i7 ]& n2 O8 K) \3 s7 v6 _

zxyritcgbfz6403796051.gif

6 r$ L l @+ W2 n0 r

% @6 }7 w& z G, _6 H v- m) C关注我们- Y/ O6 {8 L0 h$ f$ a& m- e* t

/ H3 Q+ O% Z3 m1 r, l& `

. V8 t" R/ U: w+ S6 n

22khmwrmj3x6403796151.png

/ }4 w. F5 B$ _

/ }4 w. F5 B$ _

| % e. C' V/ H* J5 e4 j, A

l0wwcxgpjkd6403796251.png

4 w* a& Y8 X2 Q% u" U0 ?% a | 1 \( p" |1 H1 b* a) i) Y

av1bygzdukb6403796351.png

0 l. [+ X1 s* M# N

0 l. [+ X1 s* M# N

|

_+ G7 _9 U3 G! l8 ^* ?8 Z+ {

, R2 ~4 ^5 w2 M) g

: A# U6 @! r- d6 o

' \8 x s7 _' q9 m关于我们:+ f. i1 r, ]- b6 E6 l$ T p& e

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。! u+ L4 Z7 R- m8 W" i

/ ?* ?2 u' C' B4 J. j' qhttp://www.latitudeda.com/2 {2 V" e# u) X' Z) f

(点击上方名片关注我们,发现更多精彩内容) |

|