|

nkjk4yiids26404092617.gif

' s r7 a$ P/ U( F% x" r

' s r7 a$ P/ U( F% x" r

点击上方蓝色字体,关注我们4 C" d: ]. S4 g# {) v! g; e

: v( t; u8 }1 q- \2 g. P. ~1

7 @/ w1 o U5 q7 M0 G8 l异常波形分析

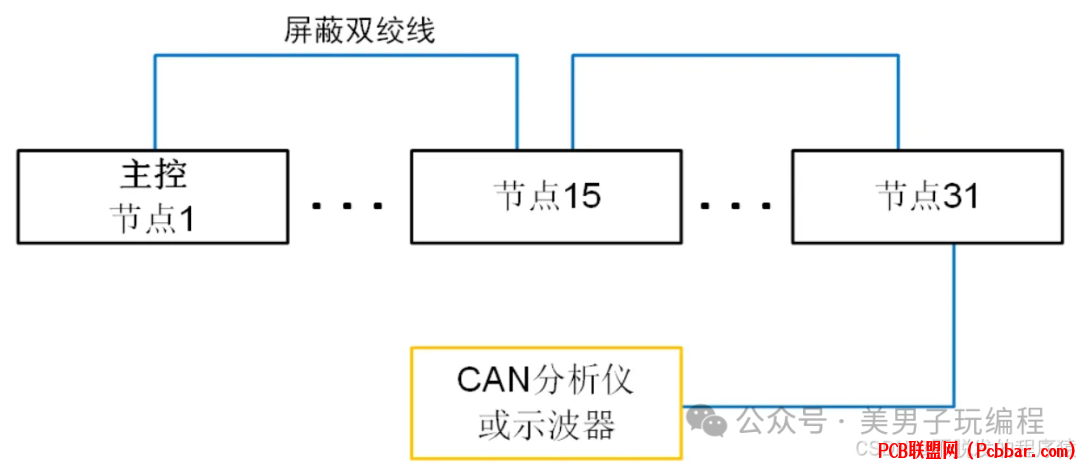

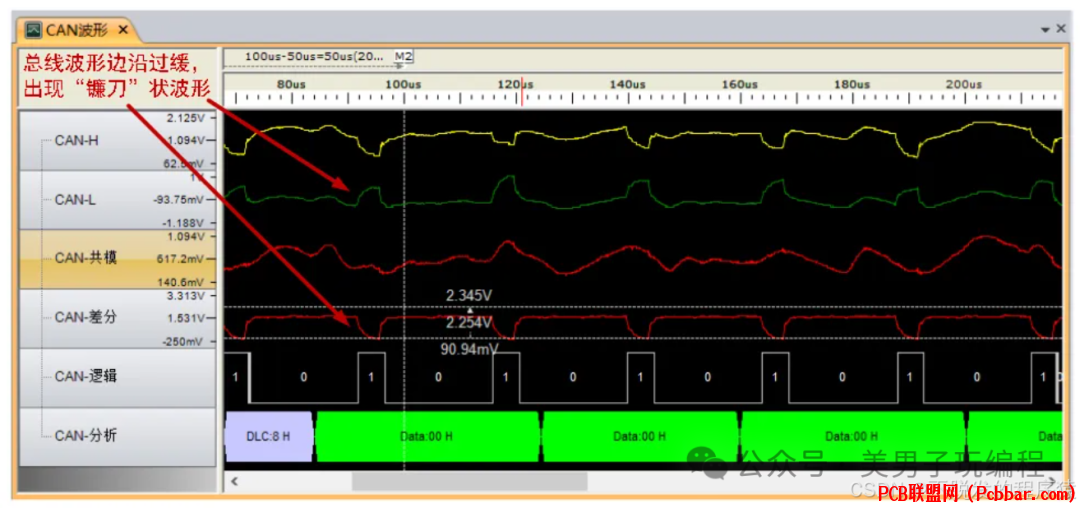

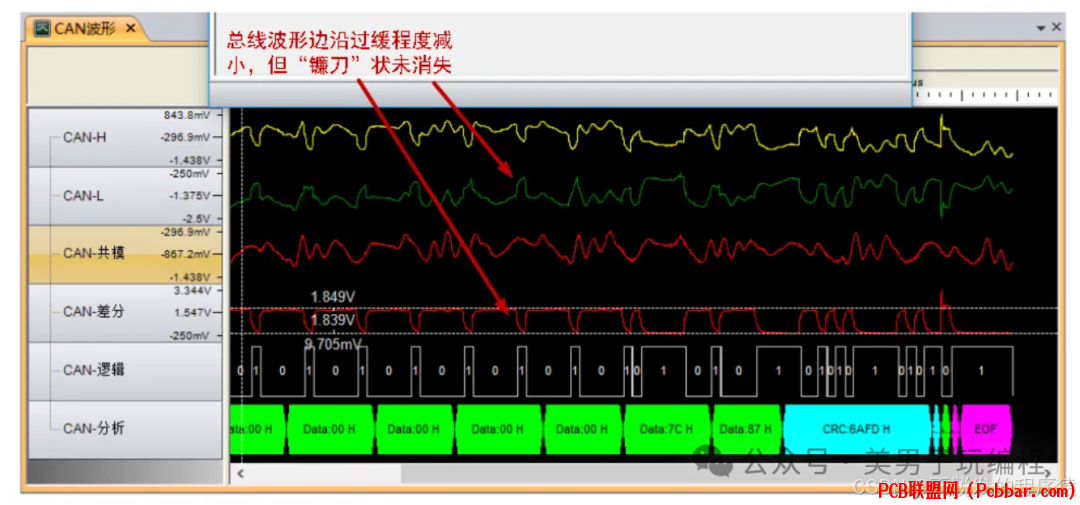

/ T. u' [6 h4 {技术团队通过 CAN 分析仪抓取第 31 个节点的总线波形,发现其边沿过缓,且呈现明显的“镰刀”状。' P5 K$ A( m: H( z' N$ n

; N3 b! v6 h& B

vd5sk3qdyte6404092722.png

, M$ a7 [% P6 h; f, k

, M$ a7 [% P6 h; f, k

/ l: g2 I3 w) N$ J: \$ b

hzlac3kjnzn6404092842.png

7 ?; l$ u- [% b0 A5 q) M$ x

7 ?; l$ u- [% b0 A5 q) M$ x

7 F+ a/ f+ n3 b" E. u5 \6 C( @

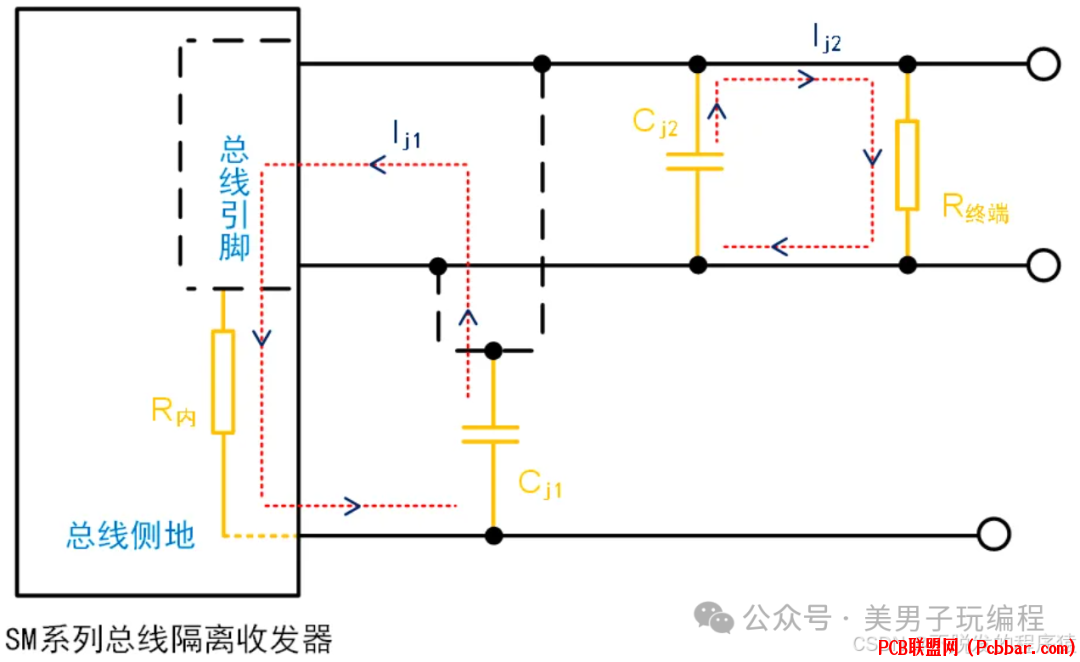

经过分析,总线波形出现此类异常的主要原因是 总线上存在较大的等效电容,导致信号的充放电时间过长。# z0 s- u. Q; T' d

22 ?* R4 K: y% M5 X- Z

电容效应与波形异常的理论基础& X$ H& K0 o4 \' _! d$ c

根据充放电时间公式 t=RCt = RCt=RC:9 W1 m/ M+ R J/ h

RRR:等效电阻,包括 收发器内阻和 终端电阻。CCC:等效电容,包括引脚对地电容(Cj1)和总线间电容(Cj2)。& j. ^/ w; E# ^. |& d! q/ B

0 M0 E% f5 d2 X; ^1 m+ x当总线电平从高变低时,电容上的电压需通过内阻 RRR 和终端电阻释放。若 等效电容过大,放电时间增大,导致波形边沿变缓。

2 V; c4 s: S- u1 I, o/ F

8 G2 Q) R. r4 G7 C8 p7 w

5s2qq3scb406404092952.png

: j$ s$ B4 ~( F. m

: j$ s$ B4 ~( F. m

3

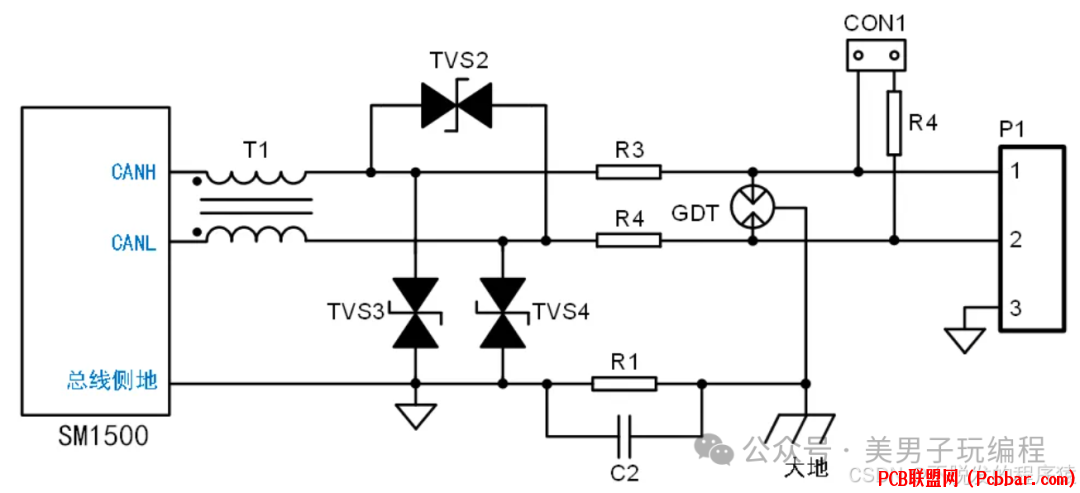

3 d$ l) u7 I9 F: A7 e; ?: J+ q" {2 G: x总线接口电路检查与优化1 G' `, b! ^( x- x5 b9 {* N' f

通过检查客户使用的 CAN 接口保护电路。

: y/ N4 h& J8 s, T2 r S* F

2 j, [4 s. z* p8 c) V$ q; k

l2gm3jz2q2n6404093059.png

9 e# V# J2 ^4 C Q& N& v) g

9 e# V# J2 ^4 C Q& N& v) g

; Y7 ?% ~; h" o3 D5 g/ w; r( }) y

发现:电路中采用了 TVS 管和 气体放电管作为保护器件。TVS 管的结电容较大,通常在数百到上千皮法,多个节点组网时,结电容叠加会显著影响总线性能。. q% N9 W9 \- `+ q2 F

42 S0 y, n$ b5 U, R& s

实验验证与优化过程

- w! a# C: r/ F7 X# [% [5 c去除部分 TVS 管后(保留部分保护器件)" P$ V0 E, y6 g e* n# a. {

波形边沿迟缓程度有所改善,但仍呈“镰刀”状。

, r$ m/ Y& T0 C8 Y

w2 O; ?, B3 b% O% [) Y

y2gzgzwur136404093122.png

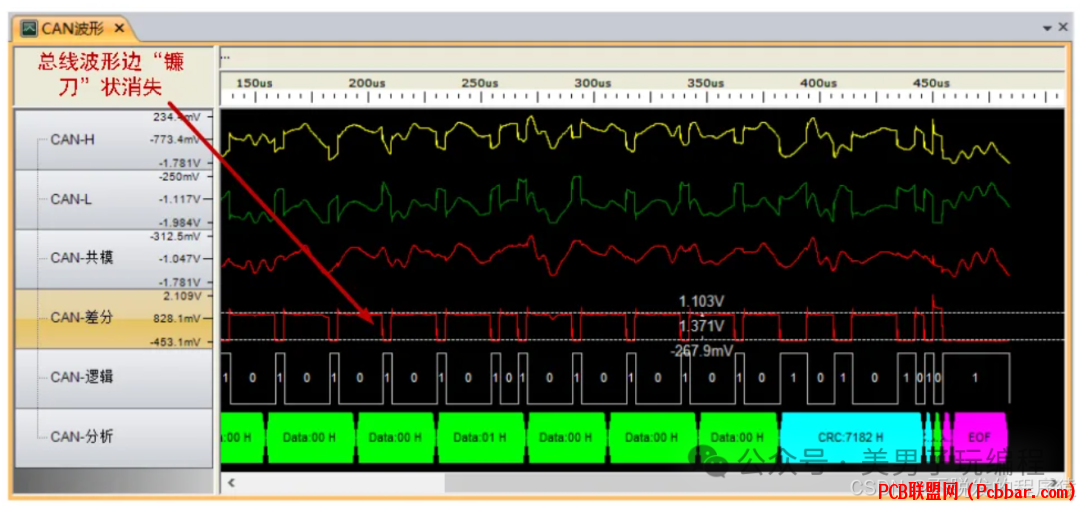

7 K6 F* h# P8 r" s$ _$ C) V2 k' \5 k完全去除 TVS 管后

7 H) C0 {% f6 {: u; r0 o' V- \波形恢复正常,“镰刀”状消失,且丢帧问题解决。

; e% |9 C, c/ t5 q' K, X6 y

4zkzcikyuoe6404093247.png

+ @1 \2 M7 ]8 e( m7 R2 U

+ @1 \2 M7 ]8 e( m7 R2 U

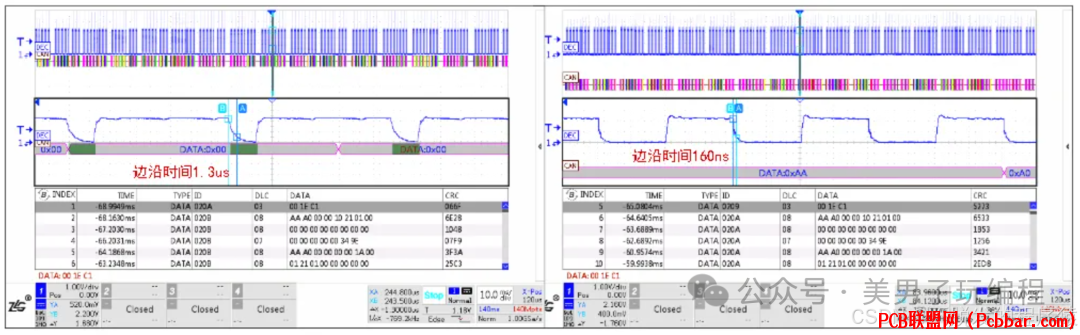

7 H: `+ z3 @% C0 B; S对比去掉 TVS 管前后的波形:

+ Q$ I3 C$ {' k& Z2 a& G优化前:边沿时间约 1.3 μs。优化后:边沿时间减小至 160 ns,通讯性能显著提升。

$ h- F$ K N: a+ G, r: ^$ n

yfjplu2onz56404093310.png

$ A; V5 K$ { s3 m3 m7 O N

$ A; V5 K$ { s3 m3 m7 O N

5% E/ Z3 i3 w$ v1 h! q' a! i+ m# h

结论与建议 y4 n7 O( V/ K* K9 g

异常波形的核心原因:

, m/ {4 r, ` s7 K) X' f( D总线等效电容过大是“镰刀”波形的主因。保护电路中使用的大结电容器件(如 TVS 管)可能导致总线性能下降,需权衡其保护效果与通讯效率。

6 Z) ~& }2 D0 ~( g: \! v0 s' F9 M; z3 R) E) v

优化方向:

; `! @% a l1 r' h优选低结电容的保护器件。组网设计时,尽量减少无必要的并联电容。在调试时通过波形分析仪定位问题节点,并适时调整终端匹配电阻值或减少节点数。. U3 a, d4 }+ C& J

6 U4 T' e8 |0 q' s. q0 D7 Y" D5 n

建议的实践措施:: k# N: P0 y2 P8 S' W, X

对关键节点进行波形测试,确保边沿时间满足协议要求。在节点数较多的情况下,适当降低通讯速率或优化拓扑结构(如采用分支网络)。* j; z5 |( Z L0 Q3 A

4 j! F/ a9 A8 j6 \此案例充分说明,总线通讯的可靠性不仅依赖于设计阶段的参数选型,更需要在现场调试中结合波形分析工具优化组网细节,为工业场景的高效运行提供保障。

6 E3 W9 E6 Q0 w, Z+ H

czfxkkjr2aa6404093411.jpg

m! g0 O1 D4 c

m! g0 O1 D4 c

ygigrrdwn0r6404093511.gif

8 f! ?' z* R2 b) h8 a点击阅读原文,更精彩~ |