3049行RTL,Github最高星开源verilog项目 —— PicoRV32

一夜凭马从头越 —— Github Verilog“兵器谱”第四把交椅:DarkRISCV

gvwqjwtgzuz6404515445.png

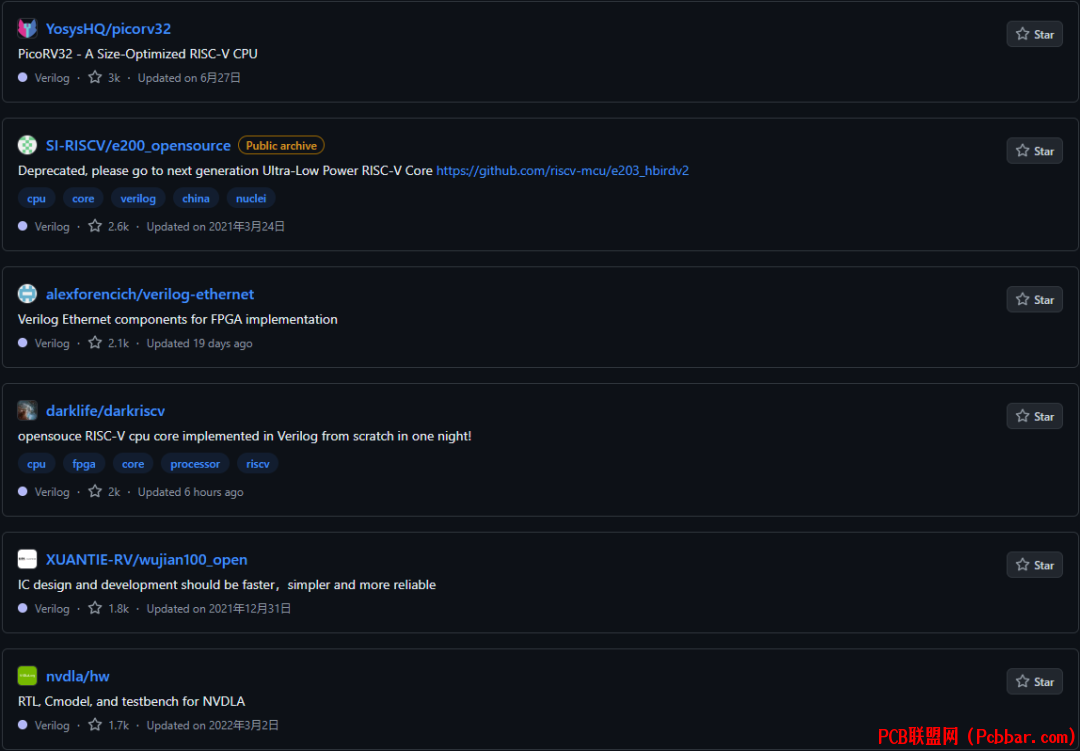

继续往下品品Github Verilog“兵器谱”,在之前的推送中已经盘点了榜单的前6名:

yfbnapo2xgt6404515545.png

而第7名是一个高性能的NIC(接口卡)和网络计算平台项目Corundum,stars量为1.6K:

pie0sxwr3dy6404515646.png

其README中介绍,Corundum 是一个开源的、基于 FPGA 的高性能 NIC(网络接口卡)和网络内计算平台。其特点包括高性能数据路径、10G/25G/100G 以太网、PCI Express 第三代、一个定制的、高性能的、紧密集成的 PCIe DMA 引擎、众多(1000+)的传输、接收、完成和事件队列、分散/聚合 DMA、MSI 中断、多个接口、每个接口有多个端口、每个端口的传输调度包括高精度 TDMA、流哈希、RSS、校验和卸载以及原生 IEEE 1588 PTP 时间戳。

此外Corundum 有几个独特的架构特性。首先,传输、接收、完成和事件队列状态高效地存储在块 RAM 或超 RAM 中,支持数千个可单独控制的队列。这些队列与接口关联,每个接口可以有多个端口,每个端口都有自己的独立调度器。这使得数据包传输控制非常精细。结合 PTP 时间同步,这实现了高精度 TDMA。Corundum 还提供了一个应用部分,用于实现自定义逻辑。应用部分有一个专用的 PCIe BAR 用于控制,以及一些提供对核心数据路径和 DMA 基础设施访问的接口。

鉴于自己对这个领域没有什么造诣积累,自然也放弃了具体去看里面的内容。如果感兴趣大家就查阅一下吧:

https://github.com/corundum/corundum

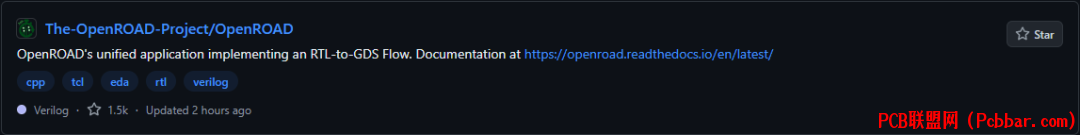

而紧随其后的就是今天的主角,坐居verilog“兵器谱”上的第8位的basic_verilog:

https://github.com/pConst/basic_verilog

在FPGA和ASIC设计的世界里,代码的可重用性是至关重要的。Konstantin Pavlov,一位热情的硬件开发者,通过他的GitHub项目basic_verilog,为我们提供了一个宝贵的资源库,里面包含了大量可综合的Verilog和SystemVerilog模块。令人开心的是,这些模块不仅适用于学术研究,也能满足工业项目的需求(可以拿来主义emmm)。该项目采用CC BY-SA 4.0许可,因此无论是出于个人爱好还是商业目的,大家都可以在这些模块的基础上自由地重新混合、转换和构建新的单元和项目。但同时需要遵循许可协议,提供原作者的姓名。由 Konstantin Pavlov 提供,电子邮件地址为 pavlovconst@gmail.com

您好!这是一个Verilog和SystemVerilog可综合模块的集合。所有代码在典型的FPGA项目和主流FPGA供应商中都非常可重用。如果您发现任何代码问题,请随时提交拉取请求或与我联系。

此外,如果您的项目——无论是业余爱好、科学研究还是工业项目——成功地使用了这些代码,请告诉我,这将给我带来快乐!

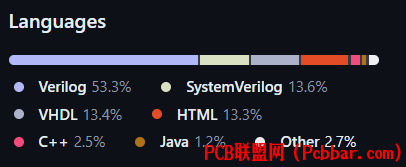

basic_verilog开源项目和之前的都不太一样,之前的项目都是一个完整的工程以及配套流程工具,而basic_verilog则是涵盖众多功能的unit block的集合体。工程的verilog代码量占比为53.3%,systemverilog代码量占比为13.6%,此外还有13.4%的VHDL代码,硬件友好度极高:

1grp153zyex6404515846.png

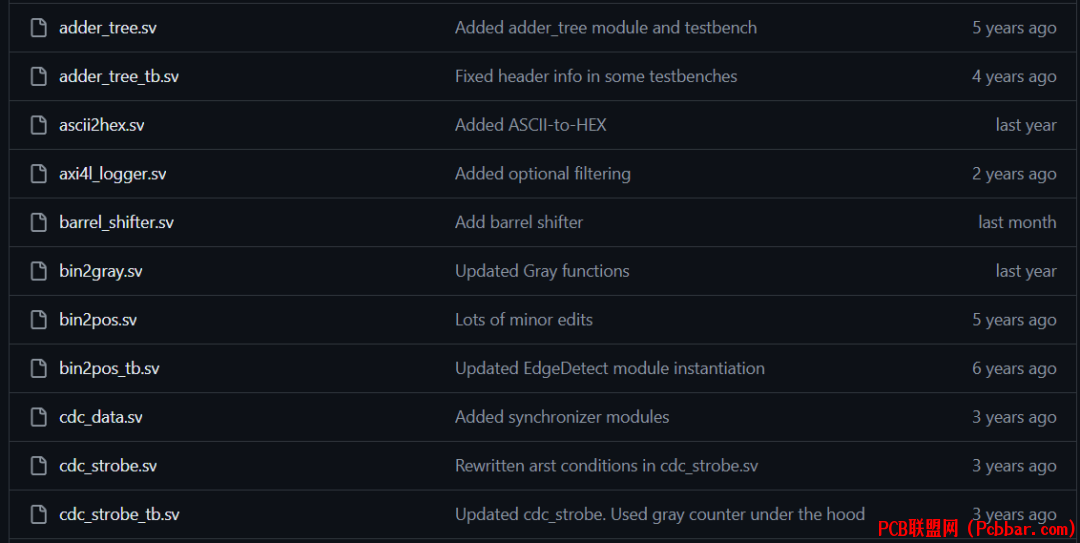

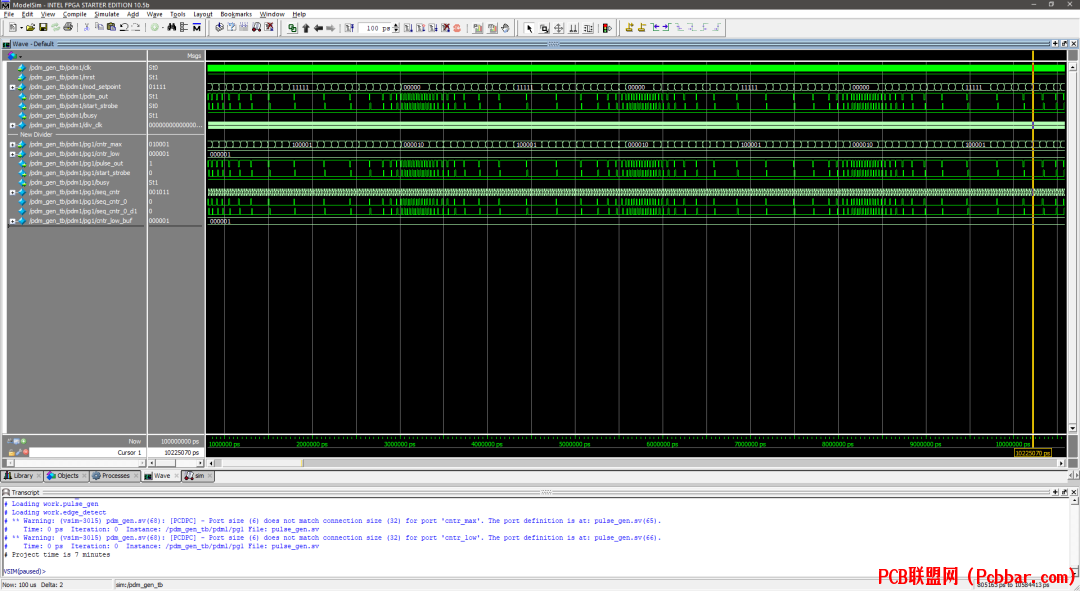

工程中提供了数以百计(我也没具体统计)功能各异的模块实现,有一些同时提供了verilog版本和sv版本,更多的是提供了二者之一。令人感动的是每个模块都不只提供了RTL,还提供了testbench:

0e5ne5cpixv6404515946.png

这意味着你把工程clone下来,想学习和仿真哪个模块只要用auto_testbench把仿真环境一建然后将testbench替换一下就可以了(适时插入自己的东西哈哈)。而且呢有些模块不只提供了RTL和testbench,甚至直接把波形图放上了,这么认真负责的态度果然是值得star的:

1wgz3bvitcb6404516046.png

不仅如此,项目里还提供了一些封装好的funtion供调用,比如说格雷码和二进制的互转:

//------------------------------------------------------------------------------// gray_functions.vh// published as part of https://github.com/pConst/basic_verilog// Konstantin Pavlov, pavlovconst@gmail.com//------------------------------------------------------------------------------

// INFO ------------------------------------------------------------------------// Gray code parametrizable converter functions//// Parametrized classes are supported by Vivado, NOT supported by Quartus.// Please use bin2gray.sv and gray2bin.sv conventional modules instead.//// Call syntax:// ============// assign a[63:0] = gray_functions#(64)::bin2gray( b[63:0] );// assign c[255:0] = gray_functions#(256)::gray2bin( d[255:0] );//

virtual class gray_functions #( parameter WIDTH = 32);

static function [WIDTH-1:0] bin2gray( input [WIDTH-1:0] bin);

bin2gray[WIDTH-1:0] = bin[WIDTH-1:0] ^ ( bin[WIDTH-1:0] >> 1 ); endfunction

static function [WIDTH-1:0] gray2bin( input [WIDTH-1:0] gray);

gray2bin[WIDTH-1:0] = '0;

for( integer i=0; i gray2bin[WIDTH-1:0] ^= gray[WIDTH-1:0] >> i; end endfunction

endclass不过因为这个项目主要的目标还是FPGA所以有些模块是需要依赖于FPGA厂商库的,这些无法直接在ASIC设计中使用。这部分模块基本都汇总在相应的文件夹中:

nywnmpkaxwp6404516146.png

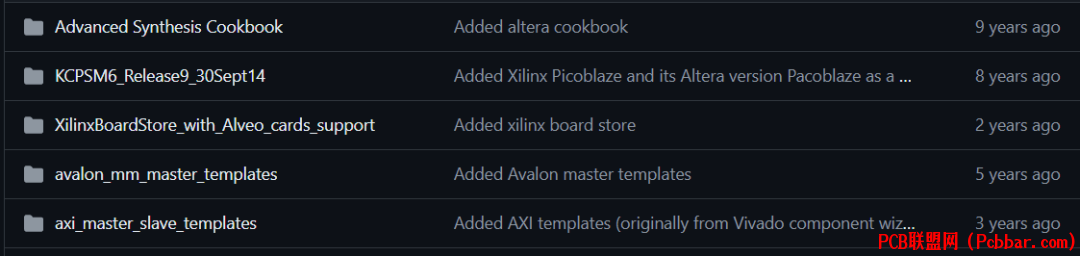

当然文件夹还包含一些脚本、FPGA实例等,从名字上也能看出个七七八八。作者在README对这些文件夹的作用、来源或者使用范围进行了说明:

5era4v3tako6404516246.png

图中标绿意为用于最基本的任务,标红则是用于高级或特殊用途的例程。如果是硬件设计的初学者建议先从标记为??的代码开始探索(原作者建议)。不仅如此,工程里的每一个RTL文件大多进行了功能说明和????建议,写注释和说明文档到这一步已经是我所不能及了!

a5ispliwknv6404516346.png

更加详细的说明大家点击“阅读原文”查看就好了。

最后呢是代码风格,又可以用到之前的形容词了“赏心悦目”,缩进得当层次分明逻辑清晰注释详实:

// WRITE =======================================================================

// sequence start condition //*cmd_rise signals are NOT synchronous with spi_clk edges if( sequence_cntr[7:0]==0 && (spi_wr_cmd_rise || spi_rd_cmd_rise) ) begin if( spi_rd_cmd_rise ) begin rd_nwr 1'b1; end else begin rd_nwr b0; end // buffering mosi_data to avoid data change after shift_cmd issued if( WRITE_MSB_FIRST ) begin mosi_data_buf[MOSI_DATA_WIDTH-1:0] 1:0]; end else begin mosi_data_buf[MOSI_DATA_WIDTH-1:0] 1:0]; end sequence_cntr[7:0] 7:0] + 1'b1; end甚至还贴心的把模块例化提供给大家:

/* --- INSTANTIATION TEMPLATE BEGIN ---

spi_master #( .CPOL( 0 ), .FREE_RUNNING_SPI_CLK( 0 ), .MOSI_DATA_WIDTH( 8 ), .WRITE_MSB_FIRST( 1 ), .MISO_DATA_WIDTH( 8 ), .READ_MSB_FIRST( 1 )) SM1 ( .clk( ), .nrst( ), .spi_clk( ), .spi_wr_cmd( ), .spi_rd_cmd( ), .spi_busy( ),

.mosi_data( ), .miso_data( ),

.clk_pin( ), .ncs_pin( ), .mosi_pin( ), .oe_pin( ), .miso_pin( ));

--- INSTANTIATION TEMPLATE END ---*/总之是值得一看和学习研究的代码。而且他的代码还有一个特点,就是赋值(包括其他逻辑语句)时前后都会加入位宽信息:

// WRITE =======================================================================

// sequence start condition //*cmd_rise signals are NOT synchronous with spi_clk edges if( sequence_cntr[7:0]==0 && (spi_wr_cmd_rise || spi_rd_cmd_rise) ) begin if( spi_rd_cmd_rise ) begin rd_nwr 1'b1; end else begin rd_nwr b0; end // buffering mosi_data to avoid data change after shift_cmd issued if( WRITE_MSB_FIRST ) begin mosi_data_buf[MOSI_DATA_WIDTH-1:0] 1:0]; end else begin mosi_data_buf[MOSI_DATA_WIDTH-1:0] 1:0]; end sequence_cntr[7:0] 7:0] + 1'b1; end关于这种写法呢在前司大家有过几次讨论,也有一些项目确实对代码风格做了该要求。但是我个人仍旧不认同这种代码风格,关于这一点在之后的推送中咱们再专门探讨下吧。好的,今天的内容就到这里,祝大家学习愉快工作顺利!

cjljybggsvs6404516446.png

系列文章入口——

| 【芯片设计】SoC 101(一):绪论 | | 【芯片设计】FIFO漫谈(零)从无处不在的FIFO开始说起 | | 【芯片设计】计算机体系结构(一)虚拟内存 | 【芯片设计】深入理解AMBA总线(零)绪论

| | 【芯片设计】握手协议的介绍与时序说明 | | 【芯片设计】复位那些小事 —— 复位消抖 | | 【芯片设计】快速入门数字芯片设计(一)Introduction | 【芯片验证】UVM源码计划(零)下定决心读源码前的自测环节

| 【芯片设计】异步电路碎碎念(一) 到底什么是异步电路

| 【芯片设计】从RTL到GDS(一):Introduction

|

其他文章链接——

| 【芯片验证】sva_assertion: 15道助力飞升的断言练习 | | 【芯片验证】可能是RTL定向验证的巅峰之作 | | 【芯片验证】RTL仿真中X态行为的传播 —— 从xprop说起 | | 【芯片验证】年轻人的第一个systemVerilog验证环境全工程与解析 |

【芯片设计】verilog中有符号数和无符号数的本质探究

| | 【芯片设计】论RTL中always语法的消失术 | | 【芯片设计】代码即注释,注释即代码 | | 【芯片设计】700行代码的risc处理器你确实不能要求太多了 |

| 入职芯片开发部门后,每天摸鱼之外的时间我们要做些什么呢 | | 如何计算系统的outstanding 和 burst length? | | 芯片搬砖日常·逼死强迫症的关键词不对齐事件 | | 熟人社会里,一群没有社会价值的局外人 |

|