|

|

|

hzeagyw0vft64068600.png

/ _6 k' x `( e6 J6 o. _1 V7 f' p7 [" E

/ T% ]+ `5 M3 s8 W铺铜究竟如何发挥作用?先插个概念:共模扼流圈

, z. ` S+ o0 A( G! A电子电路中,电子流动虽受导体约束,但能量传递并非通过粒子碰撞实现,而是通过电磁场完成。电磁场源自于载流子,却自由延伸至周围空间。( N" f( N4 {, s

铁氧体等材料会通过价电子重排响应外部磁场,从而吸收周围场能量。如果这个磁场是由附近的导体产生的,那么在铁氧体重新排列电子的过程中,导体中的电流流动会暂时受到阻碍。

, M- C6 N ?7 N8 ?! ], n* R这是因为铁氧体在吸收磁场能量时,会对导体中的电流产生反作用力。随着铁氧体吸收越来越多的能量,它最终会达到饱和状态,即它不能再吸收更多的磁场能量了。但即使在这种情况下,如果导体中的电流发生变化,铁氧体仍然会阻碍这些变化,直到达到一个新的平衡状态。

- B4 @; S4 p" }) Y' i4 L这是标准的电感原理,它有一个巧妙的变体:共模扼流圈。其基础形态可见于某些计算机电缆:管状铁氧体元件包裹两条同向导线。更紧凑的版本采用环形磁芯,每根导体绕制数匝:

/ S0 q4 s& g4 f

f20n1ei5m1n64068700.png

7 w6 t5 `# e) K3 E4 \% e/ m) m

7 w6 t5 `# e) K3 E4 \% e/ m) m

共模扼流圈示意图- |8 f4 Y& t% u. E5 C. ~) j. o: B/ ]

共模电流情况:当两个导线中有共模电流以相同方向流动时,会产生一个一致的磁场作用于铁氧体(ferrite)。这使得该装置表现得像一个普通的电感器,直流电(DC)可以顺利通过,但对于高频交流电(AC)成分,其会根据频率变化的速率(即与交流频率成正比)来减弱它们。这是因为电感对交流电会产生感抗,频率越高,感抗越大,从而阻碍交流电的通过。差模电流情况:相反地,如果存在互补的电流以相反方向流动,比如差分信号对或者连接到电源的“+”和“-”导线,那么产生的磁场会相互抵消,总和为零。这就没有磁化现象发生,铁氧体没有吸收能量,所以装置的感抗(衡量其对交流信号衰减程度的一个类似电阻的指标)保持在较低水平。共模扼流圈可以抑制长电缆上的射频干扰:射频干扰通常会在所有捆绑的导体中产生相同的感应电动势,导致产生的电流是共模的。而共模扼流圈可以将这些共模电流与我们关心的差分信号区分开来,从而起到抑制长电缆上射频干扰的作用。回到铺铜

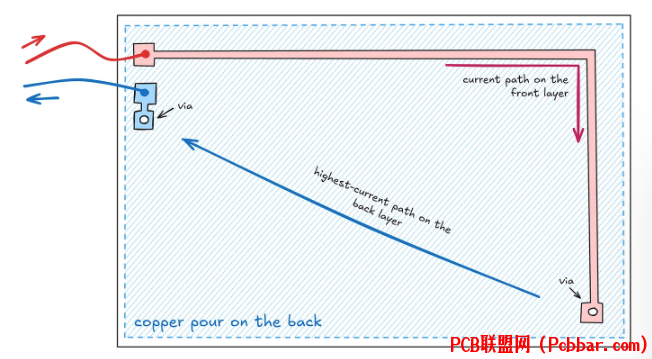

: u9 J7 N0 z1 v+ {4 ~* @. x电感现象不仅限于铁氧体磁芯,PCB走线同样存在(虽程度轻微)。为了更直观地让大家理解PCB走线电感为什么重要,举一个具体的电路板例子。这个电路板的结构是:在顶层有一个单独的红色走线,在底层有一个蓝色的铺铜平面,还有两个过孔(vias)来完成整个电路的连接。2 O4 F0 `9 v, |& v

* C" d& I8 c" C( f( |& @' v简易PCB结构示意图& M5 n: ~: q% F) Y+ z5 ]

当在 PCB 的引脚上施加直流(DC)信号时,顶层的“正向”电流被限制在走线内。而底层的返回电流理论上可以自由地扩散,但实际上它会选择电阻最小的路径,也就是两个过孔(vias)之间的最短直线路径。这是因为电流总是倾向于沿着阻抗最小的路径流动,以最小化能量损耗。; ~0 C$ U! @) W. s( D

随着正弦波频率 f 的升高,原始电流路径中的磁化相关准电阻效应也会增加。这是因为PCB走线具有电感特性,电感值 L 通常在几十到几百纳亨利之间,具体取决于走线的长度和其他因素。对于给定的频率f和电感L,感抗的公式为:- G2 o) b; B% h( x# E

lcm1lc1sm5x64068800.png

/ s+ P- v& O7 G- B, }即 20MHz 正弦频率下,感抗可达约50Ω。& m, {( G( l, C. E4 @9 K$ M' d$ s

所幸存在补偿机制:若底层回流路径紧贴顶层走线投影路径,则形成类似共模扼流圈状态——磁场相互抵消,阻抗保持较低水平。

# C9 |/ t: d( C' V( z这就会引出两个实际问题:

0 M8 p0 J: P# k' U6 \其一,如果正向路径和最佳可用的返回路径相距较远,那么就会产生较高的阻抗。在这种情况下,高速数据线上会有更多的能量以电磁波的形式辐射到周围空间。这不仅会导致信号传输的损耗,还可能对周围的电子设备产生电磁干扰。

8 b: w+ _5 r, o& f2 x2 Y& |其二,如果附近存在一些不相关的“受害”走线,并且这些走线提供了一条返回地的路径(即使是通过集成电路的本体),那么电流可能会选择这条路径,而不是我们精心设计的电流路径。这可能会导致信号传输的错误和不稳定,因为电流的路径不再是我们预期的那样。

6 P2 h. `4 i5 k$ R3 X8 w- _是否需要整板铺铜?

4 H3 L" x/ A% B) ^# X* z: D未必。铺铜并非唯一解决方案,但相比手动为每个数据总线布设电流回流通道,这种方法能节省时间。

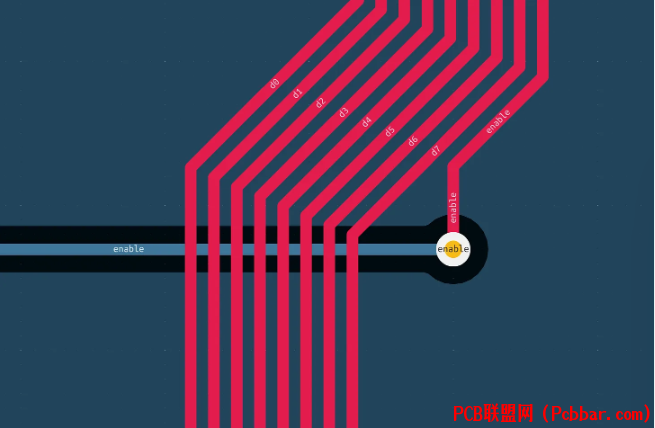

; }! Z& f) B) ]* l无论采用何种方法,都需审慎设计。比如铺铜不连续导致的问题:

! U! r% P _. o4 P+ v0 d

lag3mps5vlc64068901.png

0 s% b' B7 v, C( V不连续铺铜导致劣质回流路径9 N$ `' ]: v+ e

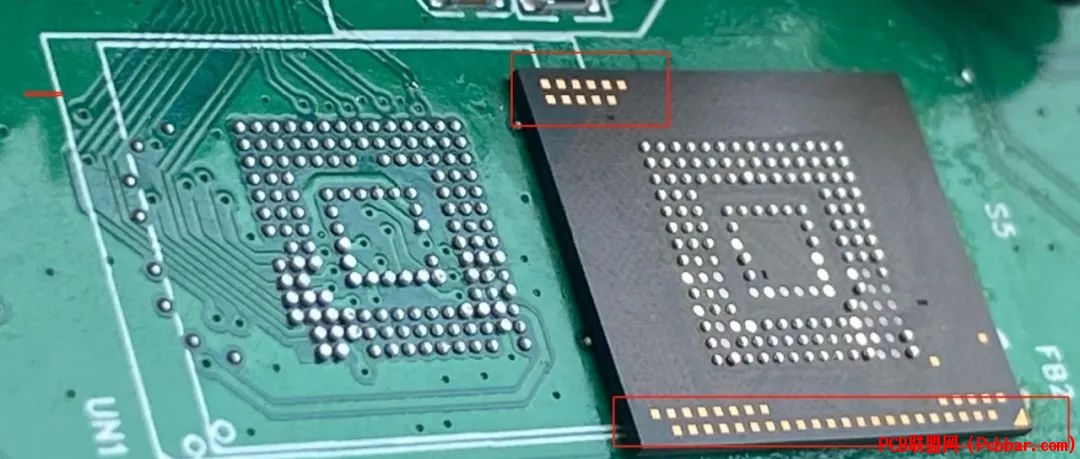

铜铺也容易让人忽视电源布线的问题。例如,下图芯片右上角的 Vdd 供电设计就不太好。# ~- ?3 p% @7 b1 v: h4 y

kpgjucexa1z64069001.png

. m& I7 h) [3 `0 F3 C( l0 Z

. m& I7 h) [3 `0 F3 C( l0 Z

正极供电路径很长为了简化设计,一些爱好者会选择使用四层板,将中间两层专用于GND与Vdd。此方案有效但成本倍增。另一个问题在于:电源平面(或者铺铜)可以降低 PCB 的电感,但会增加整个 PCB 的旁路电容。对数字信号而言,增加的旁路电容通常是可以接受的,因为它有助于稳定信号和减少噪声。然而,在模拟电子电路中,特别是在运算放大器(op-amp)的反馈回路中,每增加一点旁路电容(如几皮法拉)都可能带来不良影响。实际应用中,对多数使用ESP32、树莓派或8位AVR单片机的项目而言,无需过度纠结:铺铜应以便利设计为准则,而非盲目追随网络建议。真正挑战始于处理MIPI-DSI、USB3.0等高速接口时。. \- b, U9 n" H4 S3 l- c2 f; W

原文转载自:https://lcamtuf.substack.com/p/pcbs-ground-planes-and-you已做翻译及修订

7 E) M3 W8 ?+ d g. [$ U- [声明:

# X. L/ }5 e0 ~本文转载自KiCad公众号,如涉及作品内容、版权和其它问题,请联系工作人员微(13237418207),我们将在第一时间和您对接删除处理!投稿/招聘/广告/课程合作/资源置换请加微信:13237418207

+ k# r) x2 H+ F" x- R5 i

jllwub1d0cf64069101.png

. s0 d0 f% y" l. i$ U/ m: l

. s0 d0 f% y" l. i$ U/ m: l

; C5 _+ X) m0 f; V$ @& r- J0 L. H

2zmeksfnu2n64069201.jpg

" C' x- j4 U+ ?( D; @8 kemcC存储芯片外面那一圈焊盘是做什么用的?

* o0 G# |% d/ l$ V# ]) x0 Z3 g4 @7 H5 u5 B8 ]8 l

xwdjqeguk3h64069301.jpg

/ ?. y6 k" x! z2 k' d

/ ?. y6 k" x! z2 k' d

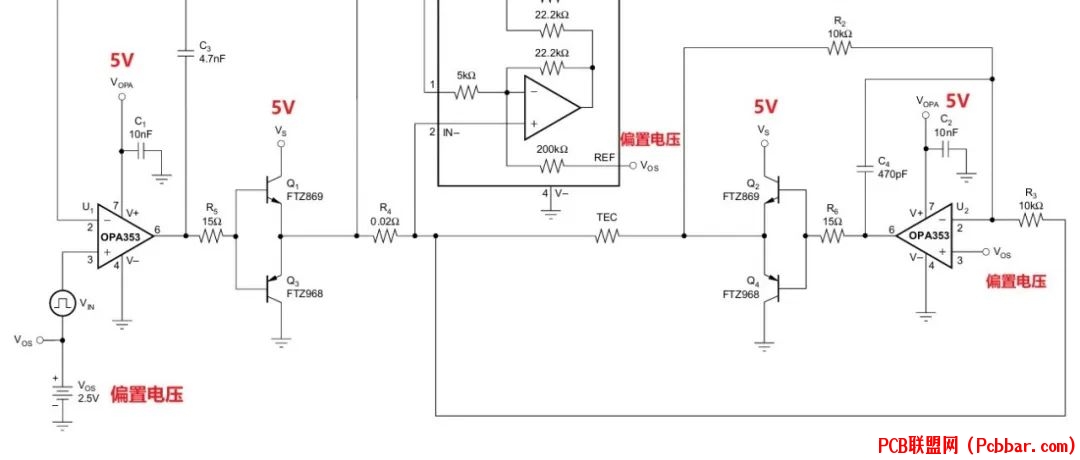

双向恒流源电路分析及仿真

9 V9 w# H" | _- ]" S" Y1 `+ U; s8 n5 u+ e0 s, R# W6 S

* U6 v0 B7 \6 X* Q& u' ?% ~

pyx3vgtnvsf64069402.png

: Y' _/ G( r$ b8 Y" F( s: i" V

: Y' _/ G( r$ b8 Y" F( s: i" V

扫码添加客服微信,备注“入群”拉您进凡亿教育官方专属技术微信群,与众位电子技术大神一起交流技术问题及心得~6 i) A X/ i/ b

分享 点赞 在看?? “三连”支持! |

|