|

|

引言

1 q [7 M- N! [* c7 N+ `9 _数据密集型应用,如人工智能(AI)和高性能计算(HPC)的快速发展为数据传输能力带来了重大挑战。随着这些系统规模和复杂度的增长,高速可靠的互连变得极为重要。引用论文介绍了一种突破性的212.5Gb/s基于DSP的PAM-4收发器,该收发器采用4nm FinFET工艺制造,专为满足大型AI系统互连的严苛需求而设计。$ r& P( U: ?& I

1 _9 u4 G# [$ D3 O

这款收发器的特别之处在于能在插入损耗超过50dB的信道上实现2.5e-6的误码率(BER)。这在严酷条件下的信号完整性方面代表了显著进步。该设计结合了先进的数字信号处理技术和创新的模拟前端架构,以克服在大型复杂封装环境中常见的严重信号完整性问题。, r$ q' C# ?% C. J2 Q

atq0e1mfbuw64026550552.png

. c* a0 i' l* a/ r" Y9 H$ E G4 t

. c* a0 i' l* a/ r" Y9 H$ E G4 t

& |! x! ?% D8 h) V6 l s' v' j# T

14 E" }8 }* n0 c$ \1 V! ~" ^& y

发射器架构5 M" S; C& X0 C0 F( P. G; c

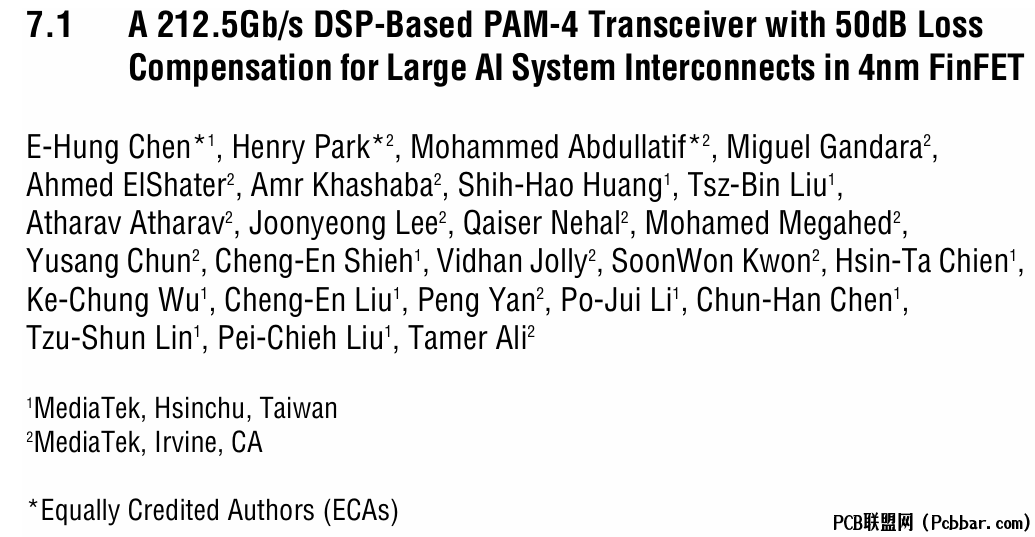

发射器(TX)设计采用多种创新技术,以实现AI系统互连所需的高数据率。其核心是TX DSP向TXFIR数字模块传输64位并行PAM-4 MSB和LSB数据。该模块将2位PAM-4数据转换为带有6抽头预加重的7位编码,为后续的64-to-1数据路径串行器准备信号。, i! ~% D* ^# V" r

+ @$ p) N) x# |0 L5 ?驱动器由电流模式逻辑(CML)7位数模转换器(DAC)构成,每个DAC切片包含一个4-to-1多路复用器。该多路复用器使用1UI脉冲宽度的4相时钟将数据串行化至112GBaud。为最大化带宽并减轻输出数据依赖性抖动,一个2抽头前馈均衡器(FFE)被集成到这个高速多路复用器中,在高速操作期间(56Gbaud及以上)激活。3 G- i/ j# J: w. V; v* x

. s( G& A( f: C/ ]TX输出网络具有四对电感,有效分散来自终端电阻、驱动器、ESD二极管和C4凸点的负载。这种L-C网络专门设计用于最小化反射,同时保持宽带宽,优化整体链路性能。7 p6 u7 ]- n) o9 Q* \

ilaez4zblbb64026550652.png

8 Q: }" j4 L- B图1展示了发射器模块图,包括TXFIR数字模块、64-to-1数据路径串行器和CML 7b DAC驱动器架构。( B5 V( J; f0 W/ r* z3 u, j

5 D: V5 g' O0 H8 T

2/ e) s* @8 _) M

先进时钟系统' }0 N+ p% Z4 C5 e8 x

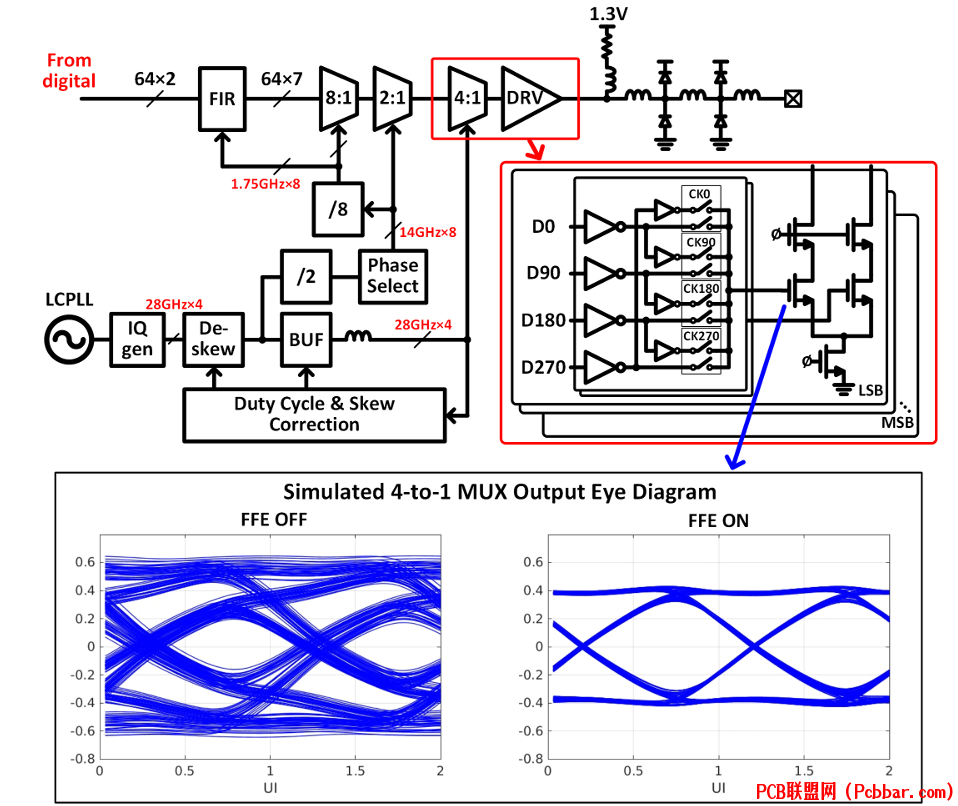

收发器采用了复杂的时钟系统,首先是抖动清除PLL(JCPLL),它生成一个干净的低频参考时钟,路由到每通道的TX/RX PLL。这种方法对于较大的芯片很重要,因为在这些芯片中参考时钟质量无法保证,从而允许TX/RX PLL的宽带宽操作。

6 B7 A2 O! S3 I% ]* I' n. r9 M! y: k) S

每个TX和RX通道集成了一个专用数字PLL,面积紧凑,便于灵活的每通道TX/RX速度编程。该设计包含一个20至28GHz的LC VCO,配有高Q值电感和二次谐波LC滤波器,以实现低相位噪声性能。优化阈值的时-数转换器(TDC)包括一个时间放大电路,增强时域增益,降低输入参考抖动和偏移。

; }: a/ J$ A1 D2 A# n% r# D

# {5 k0 @+ r& t; N4 h3 C( c正交时钟由VCO输出处的IQ生成电路产生。在Q路径中,所需延迟由一个电流匮乏反相器产生,与一个小反相器插值,最小化抖动影响。电流匮乏反相器的偏置通过背景校准环路维持,确保精确的90度相移。8 B. w! B! u3 v

kbt3goszep364026550752.png

3 A9 A1 q2 ^0 } O; ~# P

3 A9 A1 q2 ^0 } O; ~# P

图2说明了数字PLL架构,包括20-28GHz LC VCO、优化阈值TDC和用于正交时钟生成的IQ生成电路。

' `- \8 l; c- k: A

: ?9 J! B5 ]8 M2 V& N3

! K6 P1 f% I- G1 }2 c* @# O% U2 ^接收器架构+ D H" l0 ~( u

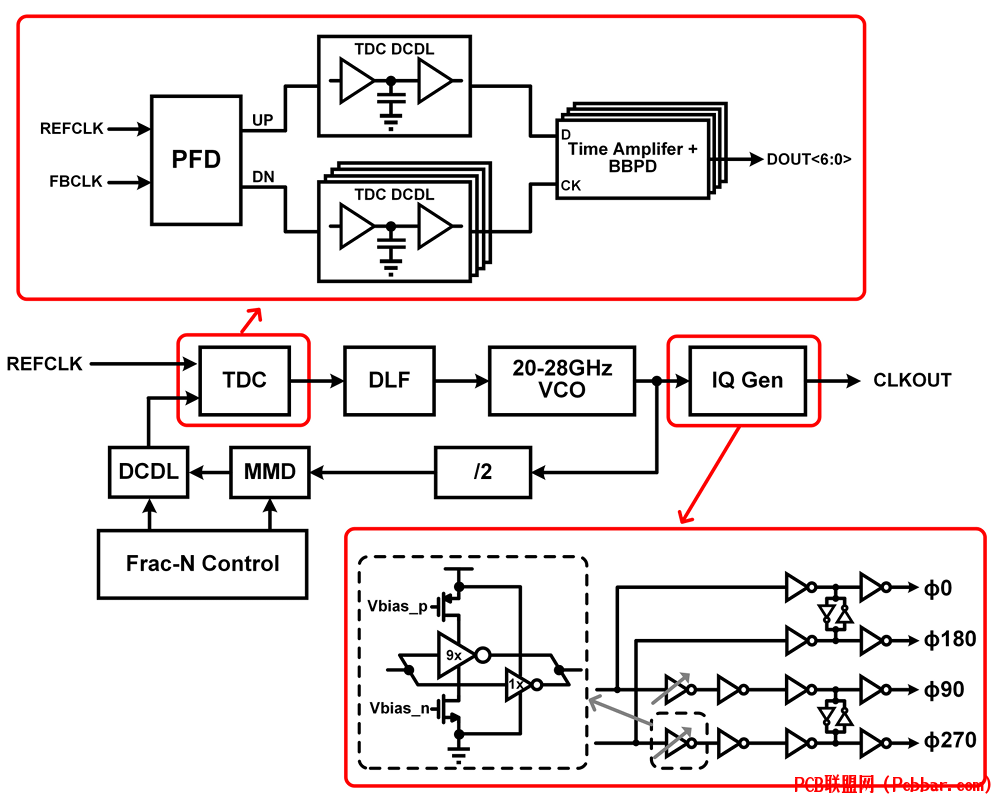

接收器(RX)设计同样精密,首先是一个输入网络,包括紧凑的T线圈和一个与200V CDM兼容ESD二极管调谐的并联峰值电感。RX终端电阻通常为50Ω,但可编程下调至20Ω以适应大幅度的输入信号。' D+ _( c1 v% r- {0 c5 o; H

`5 e" w1 S3 w6 }" k% M$ K% ^# p

具有小输入负载的源跟随器缓冲器作为RX前端的第一级,最小化信号反射。缓冲器的输出信号通过连续时间线性均衡器(CTLE),均衡后的信号分配到四个跟踪保持(T/H)缓冲器。每个T/H缓冲器由四个T/H开关以28GS/s的速率采样,每个交错路径随后由翻转源跟随器(FSF)缓冲。

! l! u: s9 u% g! [9 t F1 q3 t& a, D1 q0 G% N& w0 N

每个FSF缓冲器驱动八个7位875MS/s逐次逼近寄存器(SAR)模数转换器(ADC),导致每个RX通道总共有128个ADC单元。为管理ADC输出接口的复杂性,采用2-to-1串行器将数据从128×875MS/s上转换为64×1.75GS/s。

0 v$ u, n6 [- o# n0 C- x

: W3 J [% i1 c) ?RX DSP均衡器路径具有32抽头FFE用于码间干扰(ISI)和近端反射,32抽头浮动决策反馈均衡器(DFE)用于远端反射,以及1抽头DFE或最大似然序列检测(MLSD)用于最终数据决策。

2 s3 e( k. n* o& x$ P. i

alzmn2zjdrs64026550852.png

9 V; J! L; q. l. ~2 {图3展示了接收器模块图,显示带有CTLE的模拟前端、T/H缓冲器、SAR ADC以及具有复杂均衡技术的数字后端。! P) y6 G( m9 D \9 G

: E1 d! r1 Y e0 b% h# M# E# u4 c8 d5 _) s7 ]5 E" ^

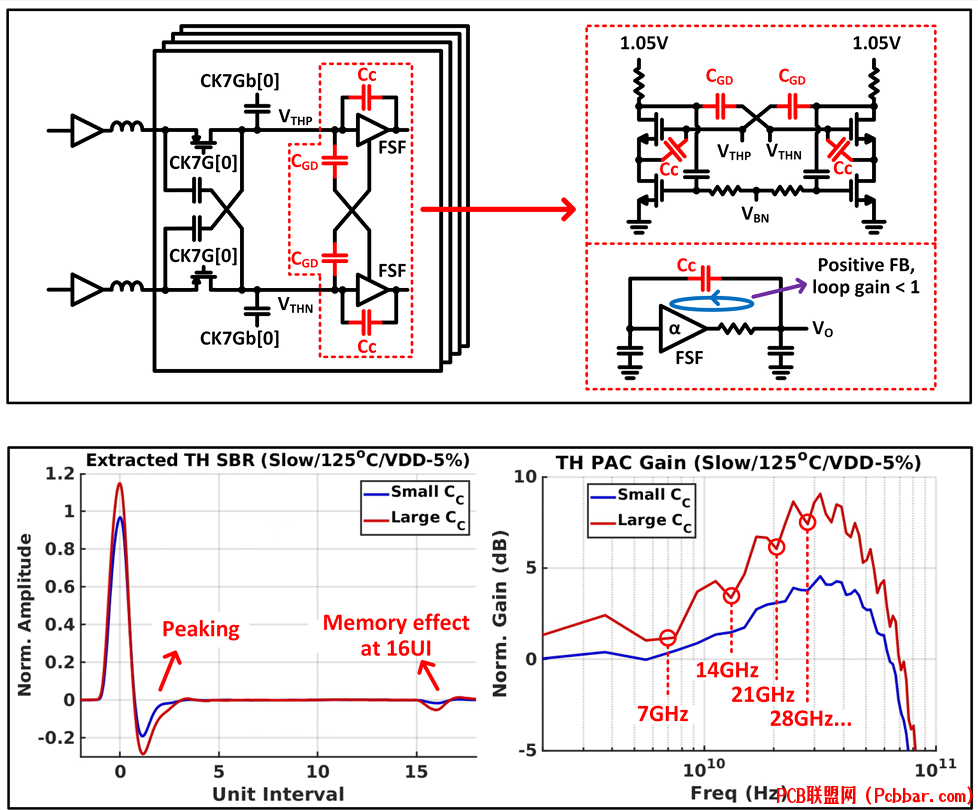

跟踪保持架构

% |& q, }3 O H& l( F2 Q/ K; u1 H接收器的跟踪保持(T/H)系统采用创新架构以优化性能。第一级T/H系统由带串联峰值的源跟随器组成,驱动四个由CK7G控制的P型T/H开关。每对开关配备数据馈通消除电容和时钟馈通消除电容,以及基于FSF的ADC缓冲器。

9 v0 y2 h' B; s# z/ U9 O% e/ R- v

基于FSF的ADC缓冲器负载较重,包含八个SAR ADC,将其输出带宽限制在20GHz以下。当T/H开关启用时,ADC缓冲器输出无法跟踪超过20GHz的高频输入信号。在保持状态下禁用时,缓冲器输出稳定在存储的输入电压电平(VTHP/VTHN)。

h. o4 V3 \: [- I* v/ |" }# B* k+ g# K( ^3 k4 j0 v0 ]

该设计的独特之处在于保持状态下的输出摆幅通过耦合电容CC反馈到VTHP/VTHN,创建一个环路增益小于1的正反馈环路。这种正反馈使净T/H响应在20GHz以上产生峰值增益,增强高频性能。

2 h4 p5 n! ]/ o( Y# I! h5 p- I$ ?7 i4 M# ?3 N6 Y' m

CC的大小必须仔细平衡 – 如果过大,可能导致先前采样信号的不完全重置,产生记忆效应,在缓冲器输出带宽在较慢角落受限时更为明显。如果主抽头和第16后置游标极性相反,这将导致7GHz整数倍处出现周期性交流增益下降。

/ B; t, E' J# ~# B" m

glurqx40erw64026550952.png

D6 I% K- i% ~3 A/ ?图4显示了通过耦合电容CC的正反馈T/H架构,以及模拟时域和频域响应,展示了大CC值的记忆效应。

; r: q" s5 Z; t: M! B

/ J& n0 m/ _0 H7 G6 Q2 Z5

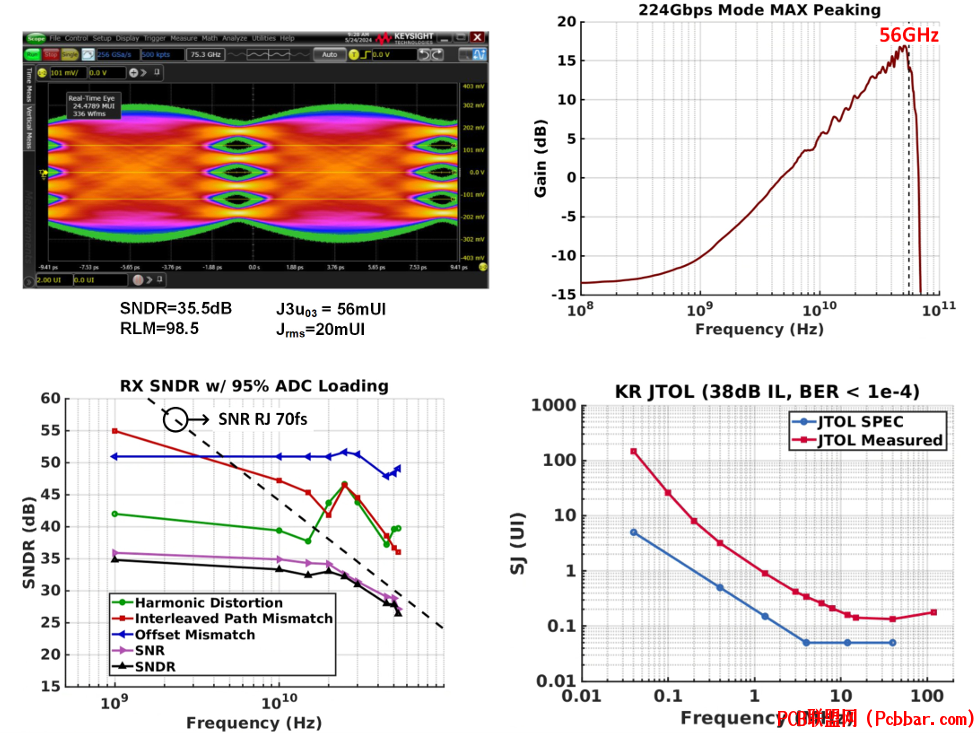

0 I8 @- ~1 ^" X( ?性能结果

( r0 L$ t) b+ {/ k7 F% u% {该收发器采用4nm FinFET工艺制造,凸点设计兼容FCBGA和CoWoS封装。测量结果验证了该设计的卓越性能。

% ~1 q1 J' i- K3 }1 B& s+ h

0 ~& P7 y: Y& T. X212.5Gb/s QPRBS13 TX眼图在9dB损耗信道后展示了出色的信号质量,相对电平裕度(RLM)和信噪比失真比(SNDR)分别为98.5和35.5dB。当TX 4-to-1 MUX FFE停用时,SNDR恶化至30dB以下,突显了这种均衡技术的重要性。

1 A* c" c' z. D3 N2 k) Q( F+ {: _1 d

在最大峰值设置下,去嵌入信道损耗后测得的RX模拟前端频率响应在56GHz处显示约14dB增益。测得的RX SNDR在低频(1GHz)为35dB,而在高频则受RX时钟路径中随机抖动的限制。

! K- M4 X) Q! m; ~ R

wj40jsw0juy64026551052.png

) W. I8 Z n! c# L8 P. Q" n9 ~图5展示了测量结果,包括TX眼图、RX模拟前端频率响应、单音测试结果和抖动容限测量。6 c. v( ?' G& X$ {/ L) N4 }$ u

6 ]3 @2 c3 E3 S' H

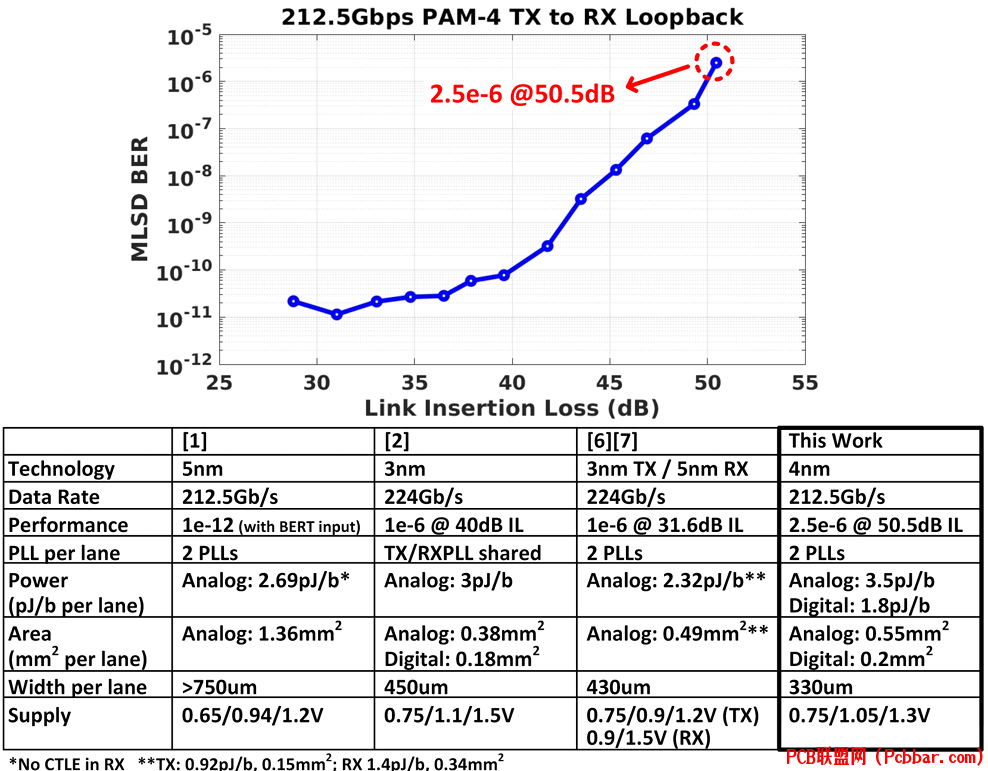

6

5 |' h& g! [) e7 ^8 W9 j+ I3 m性能比较和结论% @) w/ f! d Q% v0 A/ I

在各种迹线长度的单通道测试中,在40dB和50.5dB插入损耗上分别显示BER! W. N- s, t& x# `: C& f5 K

w6 O; B4 ?4 N! [

这种紧凑设计实现了非常高密度的前端集成,适合最先进的AI芯片,在超过200Gb/s的可比收发器中代表了最小的前端宽度。图7.1.6中的比较表将本研究与其他最先进的收发器进行了对比,突出其在数据率、功耗效率和面积效率方面的优越性能。! w- p6 t: }5 f1 T; Q! L

wc1vr2bjc5z64026551152.png

1 U# D9 ~$ X9 K0 F图6说明了BER性能与信道损耗的关系,并提供了与其他超过200Gb/s的先进收发器的比较表。! \" h; G( c! O

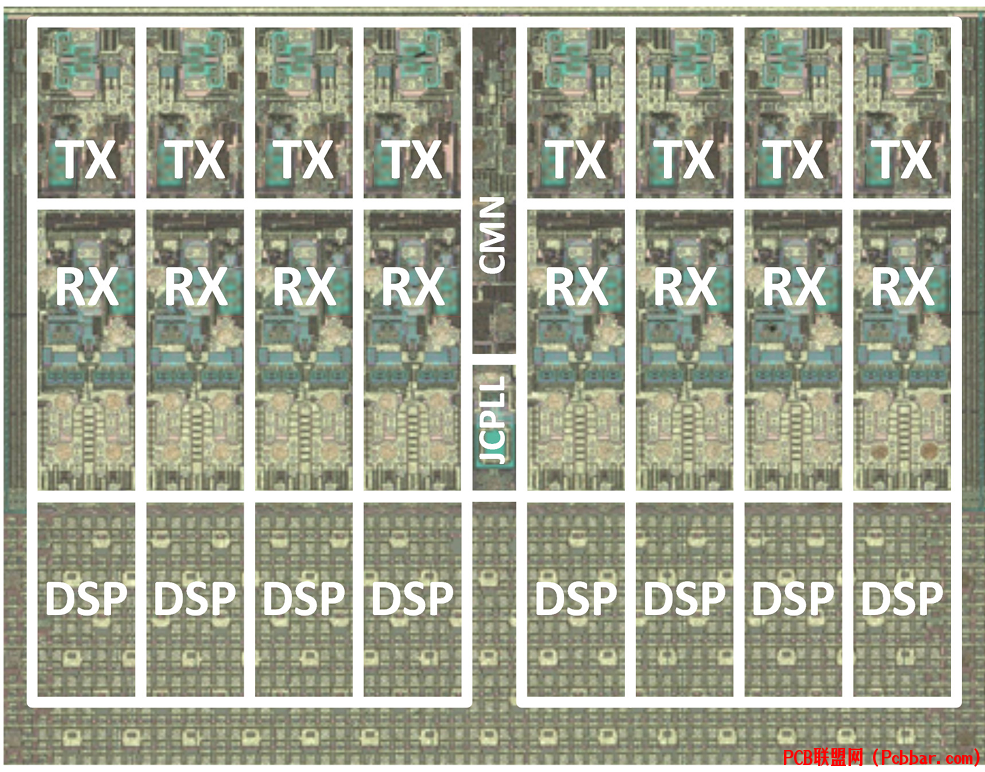

qcu4zfoyhlu64026551252.png

) ]& I( t: V6 H图7显示了采用4nm FinFET工艺制造的212.5Gb/s基于DSP的PAM-4收发器的芯片照片。! I, @0 |5 \) h

9 o* c! _& |/ B$ E

所介绍的212.5Gb/s基于DSP的PAM-4收发器代表了AI系统高速互连技术的重大进步。其能够在极高损耗(>50dB)的信道上实现可靠通信,同时保持紧凑尺寸和合理功耗,证明了在模拟和数字领域采用的创新技术的有效性。该收发器作为下一代大规模AI系统的关键组件,高带宽、高密度芯片间通信是这些系统的基本需求。

; _4 E! ^ c* K0 N

) u$ U, C9 Y ^7 A) F: Q7 J参考文献

4 A, `2 f) k8 g1 j) ^. g7 Y[1] J. Q. Wang et al., “A 2.69pJ/b 212Gb/s DSP-Based PAM-4 Transceiver for Optical Direct-Detect Application in 5nm FinFET,” ISSCC, pp. 123-125, Feb. 2024.

( ^: I' @6 p% L* v3 p/ q( m" P. |: @$ L* W1 ]5 A/ B

[2] D. Pfaff et al., “A 224Gb/s 3pJ/b 40dB Insertion Loss Transceiver in 3nm FinFET CMOS,” ISSCC, pp. 128-130, Feb. 2024.

7 ?- s# m: u* [ A

, J# h) u G# t& F5 W2 Y& Q[3] J. Kim et al., “A 224Gb/s DAC-Based PAM-4 Transmitter with 8-Tap FFE in 10nm CMOS,” ISSCC, pp. 126-128, Feb. 2021.

8 c* s7 W( X( q' j8 ~

) n! S- S7 E" H- G5 [; s[5] H. Park et al., “A 4.63pJ/b 112Gb/s DSP-Based PAM-4 Transceiver for a Large-Scale Switch in 5nm FinFET,” ISSCC, pp. 5-7, Feb. 2023. I0 s0 m+ R0 j' @, {

. h; t8 A9 T4 |/ q, i, @5 P

[6] B. Yang et al., “A high-PSR LDO using a feedforward supply-noise cancellation technique,” IEEE CICC, pp. 1-4, May 2011.

9 t0 r5 l- t) @6 hM. Cusmai et al., “A 224Gb/s sub pJ/b PAM-4 and PAM-6 DAC-Based Transmitter in 3nm FinFET,” ISSCC, pp. 126-128, Feb. 2024. [7] Y. Segal et al., “A 1.41pJ/b 224Gb/s PAM-4 SerDes Receiver with 31dB Loss Compensation,” ISSCC, pp. 114-116, Feb. 2022.7 D& l. H5 m6 g! N; [$ E/ x L

END) |( @ s& z) S3 Q

: G4 ?5 }; ^6 B! B软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

" x, Q5 H# v7 K0 U点击左下角"阅读原文"马上申请! A d- d0 V- C6 ]5 h9 G

. l5 J( ^7 }! { {欢迎转载/ |, d0 i* w9 f

( r4 b4 B3 g+ @. L$ `* w转载请注明出处,请勿修改内容和删除作者信息!

6 N' ]" x6 V/ ?0 ~; `

; o, u5 L: F5 ^

9 w4 @0 {+ n Q( g

& z- ~! |/ S0 P

elfh0xkrh0n64026551352.gif

9 Y' z2 K8 f8 ^( E D i; X m( w6 z

关注我们

4 g0 Z# K2 K$ w9 Q* }

, m0 }$ O6 ]( O% N9 |1 b

1 M0 u2 g* r4 ~) A& J* A

p4wwsa5innl64026551452.png

! Q0 d7 |5 ~# G6 o: Q9 X | + k" E5 h) `) d/ N! O% u# R5 Z5 r

u2wnm0drnu364026551552.png

5 ]0 J; U: \! P5 r2 C1 f; T" q& v | ( T7 U1 j8 F% ~; S

kthqfn4n53o64026551652.png

# w$ A' h( y" W1 H6 R

# w$ A' h( y" W1 H6 R

|

" v0 t9 g' t0 ?3 k. z6 }* A# H1 G2 I# q9 X+ i

% O' u0 }& P+ M1 W0 ~% i

2 s5 L, w9 b% H- c关于我们:) K2 P8 r1 A6 d0 v

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。4 K; N$ X7 b& ^3 F& G0 R% T

: d* }3 M1 j: N! V5 y- x N

http://www.latitudeda.com/; P* `; Q+ n5 H# E' }7 S; M

(点击上方名片关注我们,发现更多精彩内容) |

|