引言

1 T# w2 \) p9 _7 _1 \随着半导体器件不断缩小,在性能和功耗之间取得平衡变得越来越具有挑战性。当晶体管尺寸缩小到2纳米及更小时,Nanosheet技术已经逐渐取代鳍式场效应晶体管(FinFET)架构。本文探讨了通过选择性层减薄技术实现多阈值电压解决方案的创新方法[1]。; N, }- W0 H4 t

wuglku2mngq64010898027.png

7 T, Q$ O2 { o7 m

myesujgwkwa64010898127.png

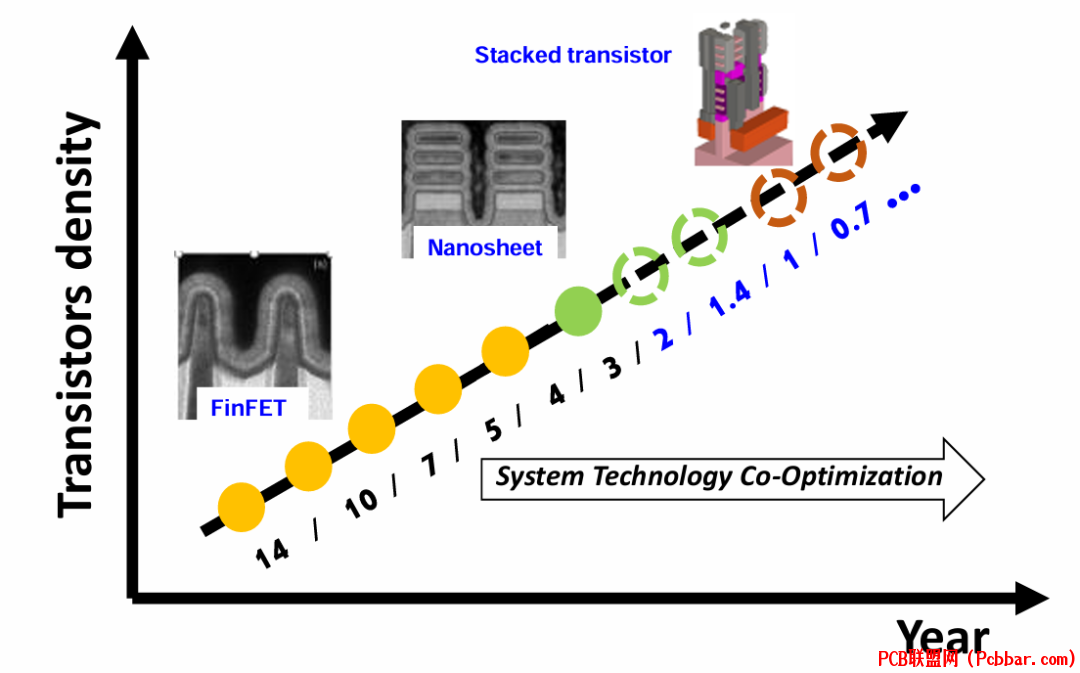

0 g4 K3 Y) L, L/ _, d" B图1展示了从FinFET到Nanosheet架构的CMOS技术发展路线图,说明了晶体管持续缩小的趋势。

4 |' v, a+ k7 R$ U- c1 I: V

6 W' z- T4 e, f与传统的FinFET设计相比,纳米片晶体管架构具有多项优势,包括每个有效器件占用面积可获得更大的有效宽度以及更优异的静电控制能力。这些优势可转化为更好的功率性能特性。随着极紫外(EUV)光刻技术的进步,特别是高数值孔径EUV的发展,纳米片技术可提供更灵活的设计选项,以优化性能并降低功耗。

' G9 d6 s) `) x a0 G! D4 W

4pd0fkbltyy64010898227.png

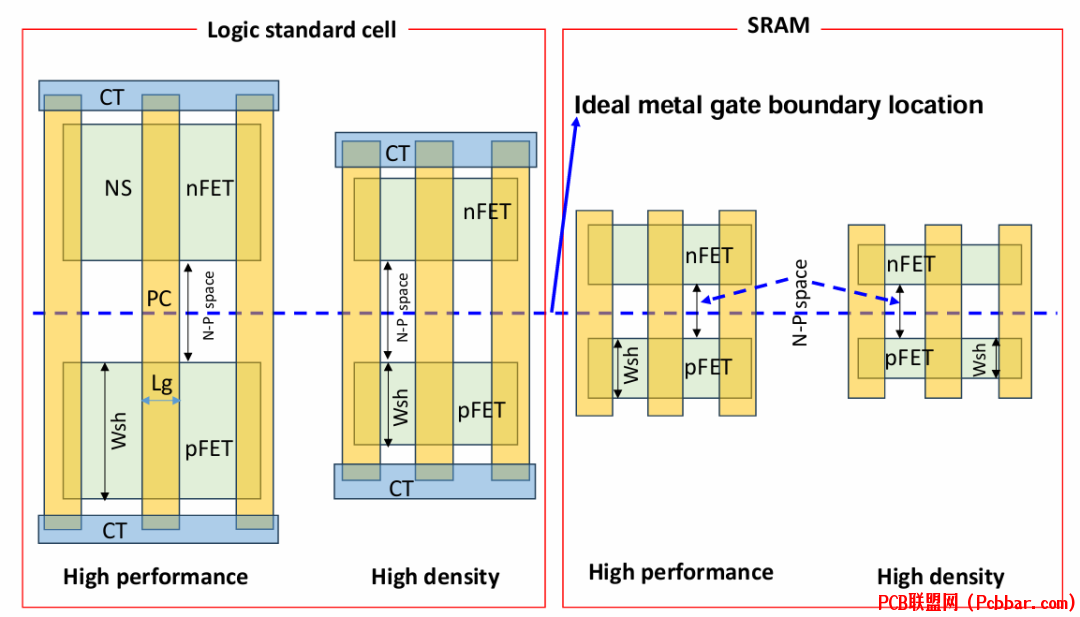

. i" R, n* y, S, A) ]' K' W图2展示了Nanosheet技术中的典型设计布局,说明了高性能逻辑标准单元需要更宽的片宽,而高密度设计则需要紧密的N-P间距。

2 M( m5 u7 l. c# h# b" M0 |* S! D+ Z- q% m6 ?) |# f: ]

11 f* T+ u1 ~ p" O( Y

多阈值集成的挑战0 O2 w# \% e2 M, F9 d

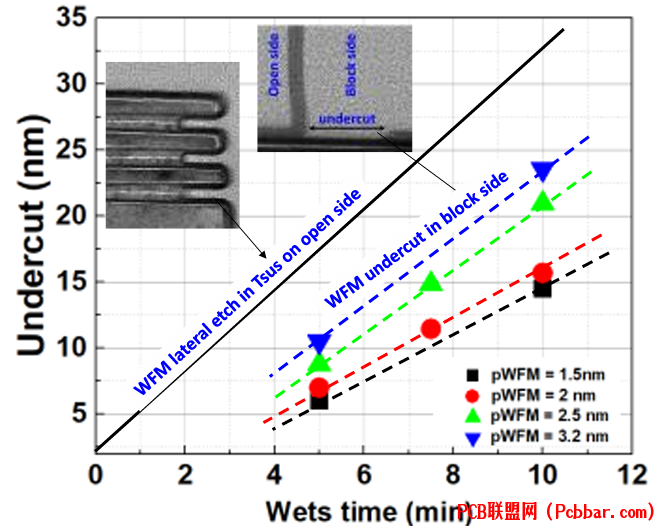

在Nanosheet技术中实现多阈值解决方案的主要挑战之一源于其复杂的结构。堆叠纳米片之间的空间(Tsus)和栅极长度(Lg)的综合效应产生了独特的集成困难。先前的解决方案使用Tsus阻塞(TPO)来避免Tsus内部的软掩模问题,但2纳米技术及其后续技术需要新的方法来实现稳健的多阈值集成。1 W* z6 P: v" f

fbnmety5fi364010898327.png

' G. a" r, }; f( V

' G. a" r, }; f( V

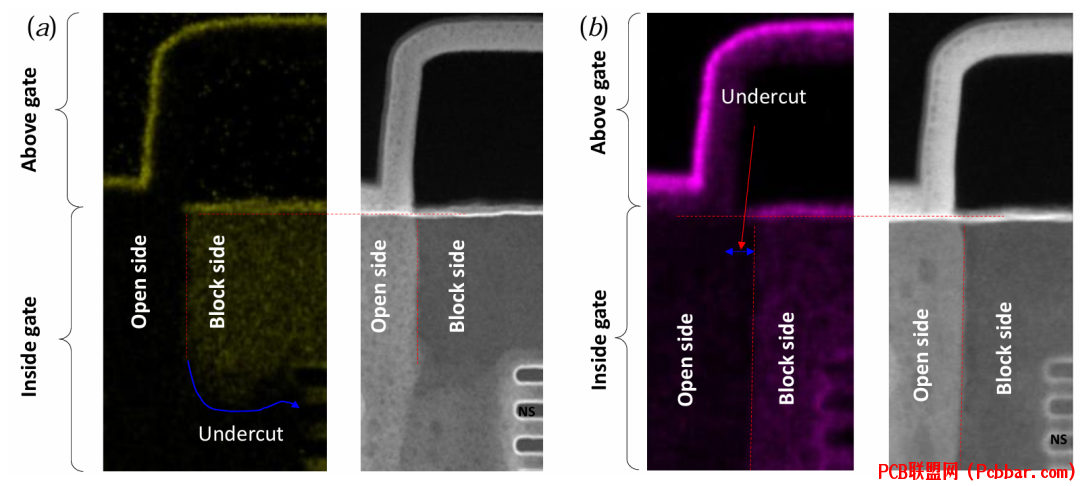

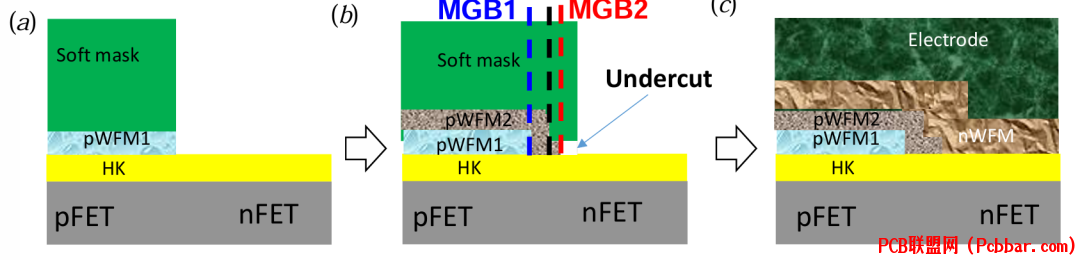

图3展示了金属栅极图形化过程中的典型下切,说明了从nFET的Tsus内部去除金属如何影响阻挡掩模轮廓。1 |+ ]% `/ r% V* |; A! F# F1 c% g

; V& h5 O* O I$ x5 ^1 C

多阈值集成的一个关键方面是管理NFET和PFET区域之间的金属栅极边界(MGB)。对于2纳米技术节点,最宽的片宽约为40-50纳米,而最紧密的N-P间距小于40纳米。这种尺寸限制使多阈值集成过程中的金属下切控制变得特别具有挑战性。

9 G8 }0 l; ^ T4 w- O

- j& z3 l+ o7 t1 B9 ~2

1 V( s y. E% \0 s; s( j选择性层减薄解决方案

- F& y/ G$ k1 G: Z0 X为了应对这些挑战,研发人员开发了两种创新方法:选择性层减薄1(SLR1)和选择性层减薄2(SLR2)。 N2 r5 ~: b" p- D& i) _

2on1bm2h0vl64010898428.png

& c! j5 j F2 A$ d& ?/ P! ~; o

& c! j5 j F2 A$ d& ?/ P! ~; o

w0suy31i3ri64010898528.png

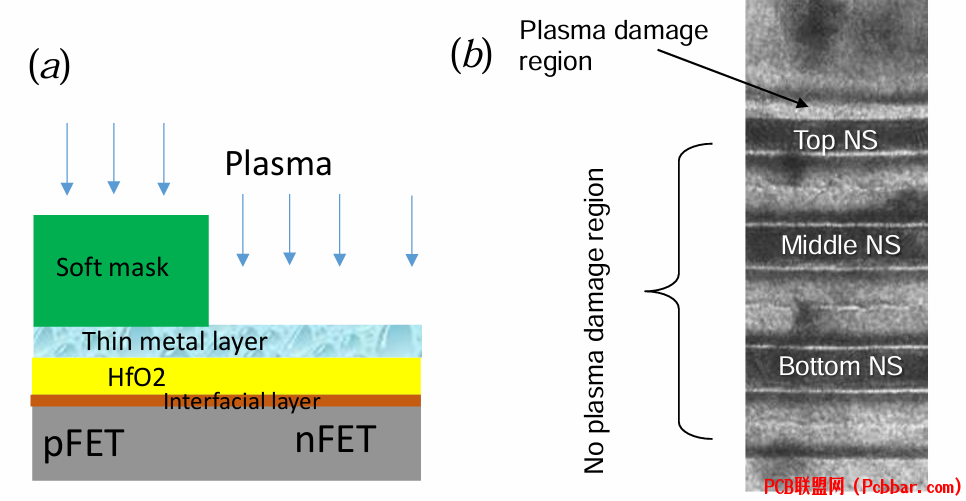

5 m0 P, f' ^2 {, R图4展示了下切如何依赖于金属厚度,以及薄层图形化过程中等离子体损伤的影响。! T% h" ~2 s& }* w

: V# w7 i1 N7 h- v& W

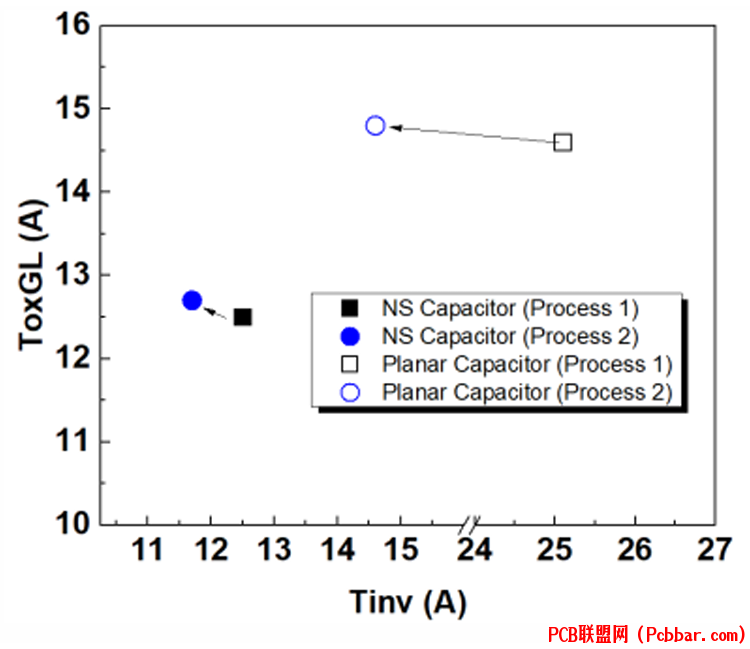

SLR1专门设计用于通过解决TPO方案上薄层图形化过程中的下切问题来控制N/P边界。该方法包括一种新的刻蚀工艺,可有效最小化栅极介质层的等离子体损伤,这对于维持器件性能和可靠性非常重要。' L. B& p; X( Z2 |7 D

hbmq4u5rgy264010898628.png

' M7 ?) F5 r' K3 U, W8 ~

ryder30bfpv64010898728.png

+ g. C2 z; f E

+ g. C2 z; f E

图5展示了SLR1实现的优化结果,以及通过新工艺实现的介质特性显著改善。

& J$ y R0 D, }% }9 J+ ?$ @4 I/ \1 [8 O

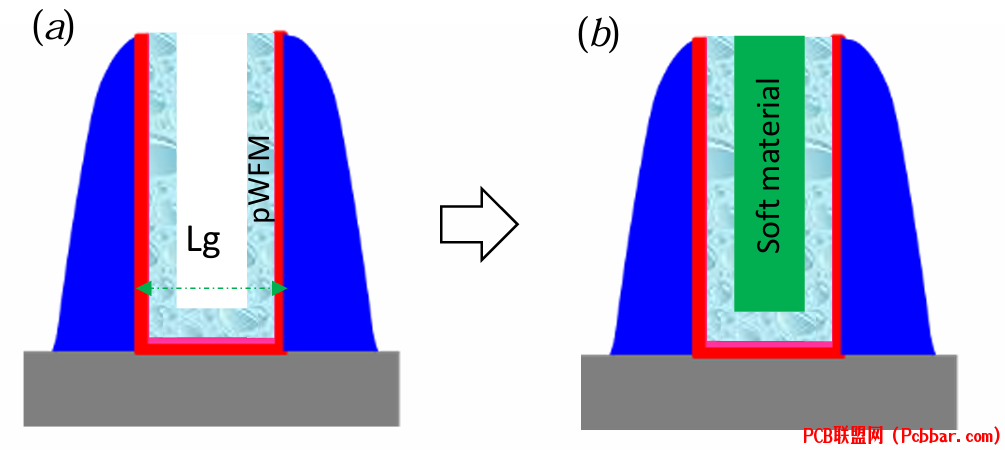

另一方面,SLR2着重于控制厚功函数金属(WFM)集成过程中的N/P边界。这种技术对于在保持适当金属栅极轮廓的同时实现低阈值电压器件特别重要。+ H1 M6 b3 ~. ^& m+ j$ T3 |( {

wneawwa0bfv64010898828.png

! n6 {8 v% J$ y3 q$ r' }

! n6 {8 v% J$ y3 q$ r' }

gp3xkcfn01z64010898928.png

( j5 ]" P' O1 H$ I0 S* X图6展示了栅极长度缩小对金属栅极图形化的影响,以及提出的多WFM沉积方法。6 V6 P! M/ t3 {

1 }. H& C2 c( _9 k3

5 X5 w; }% m2 w+ H性能优化和结果

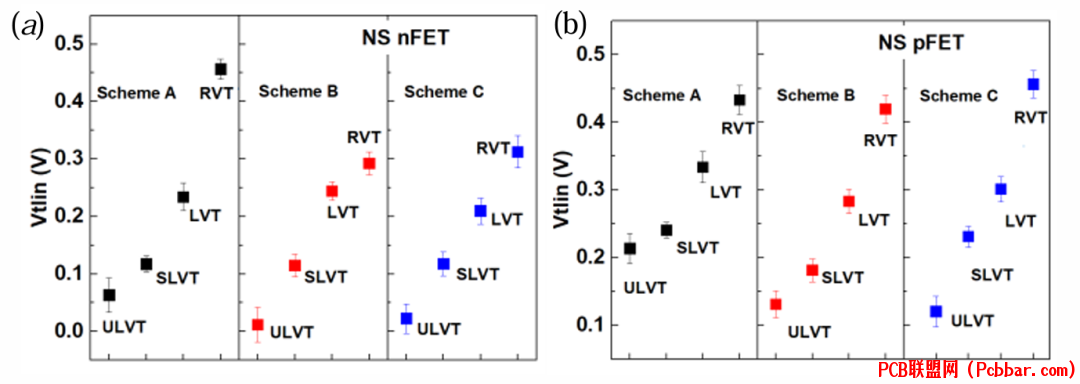

: h1 e* P9 s8 w7 j( R5 P这些选择性层减薄技术的实施在实现多个阈值电压选项方面取得了显著成果。通过结合无体积多阈值和金属多阈值方法,研究人员成功地为2纳米高性能纳米片技术实现了四对阈值电压。

; u* S! [; a8 c; X% z5 f8 x

2n4ahyhos4x64010899028.png

! z/ X- H# w. r/ v( M1 F8 W

ty0dah0ixzh64010899128.png

( F" w4 g) _* K) F& R* Z

( F" w4 g) _* K) F& R* Z

图7展示了通过不同集成方案实现的四个不同Vt对及其相应的性能特征。$ k2 y, G2 Y( x" {

. Q/ G% B% B0 I0 m0 X: K( ~0 x优化过程需要仔细考虑NFET和PFET的特性。改进的双偶极子集成方案在保持器件性能的同时,可以精确控制阈值电压水平。

: `+ k4 Y; M! ]0 B

dk2ojxmvgiy64010899228.png

7 F, }- o+ ~0 @5 Z; @

7 F, }- o+ ~0 @5 Z; @

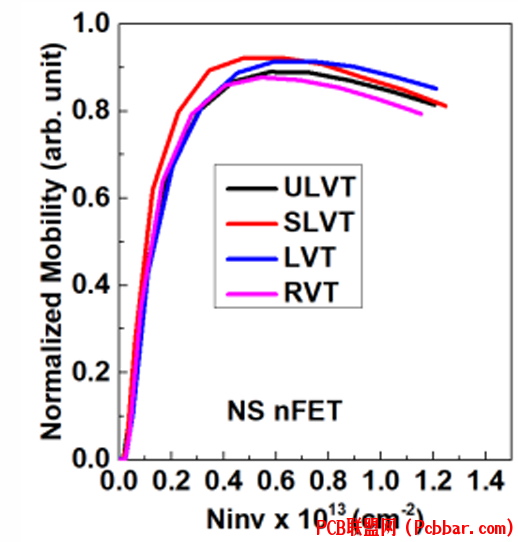

图8展示了引述论文中方案C中不同Vt选项的一致性迁移率特性,证实了在各种阈值电压水平下性能得到保持[1]。

; I" f& l" a; H) W7 t! O) t: m

- u( g9 m* H5 k U- c; C; @6 X$ g5 P3 i这些技术的成功实施使得在不损害器件性能或可靠性的情况下,实现了广泛的阈值电压选项。这一成就代表了半导体技术向下一代应用推进的重要进展。

! B+ O, N3 H G. U) T. |

dzjoxlgexlk64010899328.png

% [, }/ ]1 E# a3 k( t5 N

% [, }/ ]1 E# a3 k( t5 N

图9展示了引述论文中方案C中NFET和PFET器件实现的完整Vt范围,展示了该方法的灵活性[1]。

" S( {! O3 N# E2 d8 W, R5 e/ |9 c

本文介绍了通过选择性层减薄技术在2纳米纳米片技术中实现多阈值电压解决方案的先进方法。SLR1和SLR2的结合,加上改进的双偶极子集成,提供了一个稳健的框架,可在保持器件性能和可靠性的同时实现多样化的阈值电压选项。

4 k6 |9 P( Q& N0 n

9 A5 ^) R8 W: Z5 l9 V7 _: N参考文献# |# J. S" N/ R3 n% q2 V* R

[1] R. Bao et al., "Advanced Multi-Vt Enabled by Selective Layer Reductions for 2nm Nanosheet Technology and Beyond," in 2024 International Electron Devices Meeting (IEDM), 2024.2 |$ `* n8 e) C: ~4 Q

END

1 a c% k& ], t3 S" a软件试用申请欢迎光电子芯片研发人员申请试用PIC Studio,其中包含:代码绘版软件PhotoCAD,DRC软件pVerify,片上链路仿真软件pSIM,光纤系统仿真软件pSIM+等。更多新功能和新软件将于近期发布,敬请期待!8 j: m4 Y k) `! } Q5 S( G

点击左下角"阅读原文"马上申请

2 ]5 e3 H/ M* x c% |; I! i/ q t4 \. o+ `' Z( a. E

欢迎转载% ]$ Y6 N5 }6 S" g

, b; T7 H8 A& y; B) n. X2 X; Z% [

转载请注明出处,请勿修改内容和删除作者信息!: |$ Y- [" v) w# Y

% V$ |6 R- W `3 J

2 M1 W+ V) D) d) `# g3 G

1 t: `! F/ _. n

mao2b0r3mdz64010899428.gif

4 U) Q. O0 J# K/ e

4 U) Q. O0 J# K/ e

+ x0 I% \& z2 k( n

关注我们

! _1 L6 ]& t# X& P8 F) [

+ M+ u( a% j( a9 G& w, `+ E! X5 u

( T! i# V* w+ f3 r' p; c }9 Q

pi4bfptnjy164010899528.png

+ c! x; v3 i f! ^! u) d0 b% e |

r$ }) |1 N5 L

d1gbhggxw2f64010899628.png

; {$ m I* q4 O7 R* j: w: d( a

; {$ m I* q4 O7 R* j: w: d( a

| - n$ B9 }" j7 S& E- x0 |

ovtltnlcxpg64010899728.png

) O) Z" V# v& O- L1 y; L1 Q |

1 k' F- L. i8 r, V! [

% X! c# X" ~+ i- b6 M( i! G, ~# n9 s

. }! w, L2 l3 r! O8 D) R- ~+ p; F5 u! }4 _7 I

关于我们:9 ]- S* U* t) g0 ^

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。( |0 o- G. D) W- `/ o* P H0 n

# x6 K' A$ x. L& Z2 C0 Ohttp://www.latitudeda.com/

1 _! u* W2 E x: K! D(点击上方名片关注我们,发现更多精彩内容) |