|

|

引言

7 Y, m' D6 i- }/ f. l: H( x; h半导体行业正面临传统缩放方法接近基本物理极限的挑战。过去十年间,三维集成(3DI)和异构集成(HI)技术在现场可编程门阵列、背照式CMOS图像传感器、高性能计算GPU和高带宽存储器等多种半导体器件中得到广泛应用。这些先进技术的核心在于晶圆键合、硅通孔(TSV)和晶圆减薄工艺[1]。

, F! |8 | Q8 t

qx41ws2hhvr64012024530.png

9 Y2 \! C2 o! u7 j2 v; d! A3 ?0 c% @( c' V

leqzl45pveh64012024631.png

% ^7 }, v& i) R( w8 u% i

% ^7 }, v& i) R( w8 u% i

图1:2022年至2033年逻辑技术发展时间表,展示了从FinFET到环栅(GAA)再到互补场效应晶体管(CFET)的技术演进。该路线图展示了器件架构日益增加的复杂性以及先进制造工艺的关键作用。8 x' K. e6 P& S! o

4 t( P7 K5 I# p' [2 n5 k7 N

1

- B# l$ w! m/ h, l6 c" V晶圆键合工艺流程

8 @% n( B3 R; k8 { v晶圆键合工艺包含一系列需要精确控制的复杂步骤。由于融合键合和混合键合技术在可扩展性、成本效益和可靠性方面具有固有优势,半导体行业主要关注这两种键合方法。" h; J, p" x5 d! W; V; m

3d2ugdwc4qy64012024731.png

, v* U/ N- E* B图2:晶圆对晶圆键合工艺流程的详细说明,展示了从等离子体活化到最终光刻的关键步骤。工艺流程展示了在保持精确对准的同时实现高质量键合的复杂性。

$ Z1 P, ^( @2 x9 v, ~8 f$ c/ q! ~. Y* e5 }

2

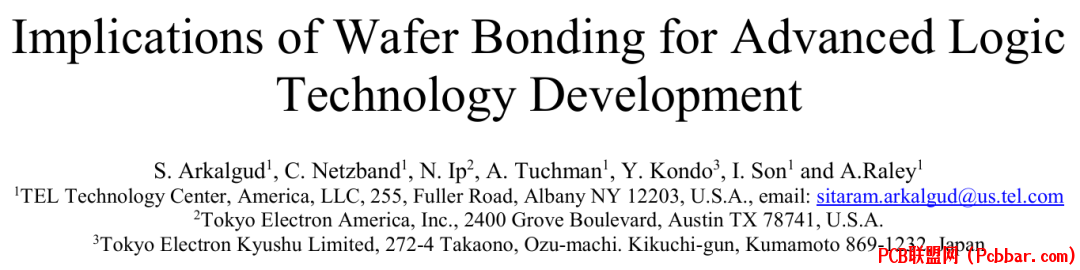

1 P9 K( `1 k* `0 ~* U7 L- `4 f& j叠层对准和变形控制的关键因素! O$ e- E" C- }& L2 w% Q; f

在先进逻辑器件应用中实施晶圆键合时,叠层对准和变形的管理格外重要。半导体行业采用复杂的四因素模型来有效分析和控制这些参数。

0 t2 s: \$ c8 E

5wrvnuvpwxb64012024831.png

; r( |6 m0 L- A' r% S图3:晶圆键合中使用的四因素模型示意图,说明了总叠层对准如何分解为缩放、平移、旋转和变形分量。该模型为理解和控制键合精度提供了框架。- Q* u% H- }7 P! D! m! W: \" @

0 _; M2 j7 Q; a- t6 Q- q

cpjfmjarrdv64012024931.png

$ {9 |# C3 a B5 ?5 \图4:展示键合工艺参数对变形影响的模拟结果,包括卡盘压力效应和晶圆释放行为。图形显示了径向位置与变形残余量之间的关系。/ W( d) _; H, X- o9 J

6 ?0 I1 `* t3 y% _38 `9 ?( c. i4 c5 N R

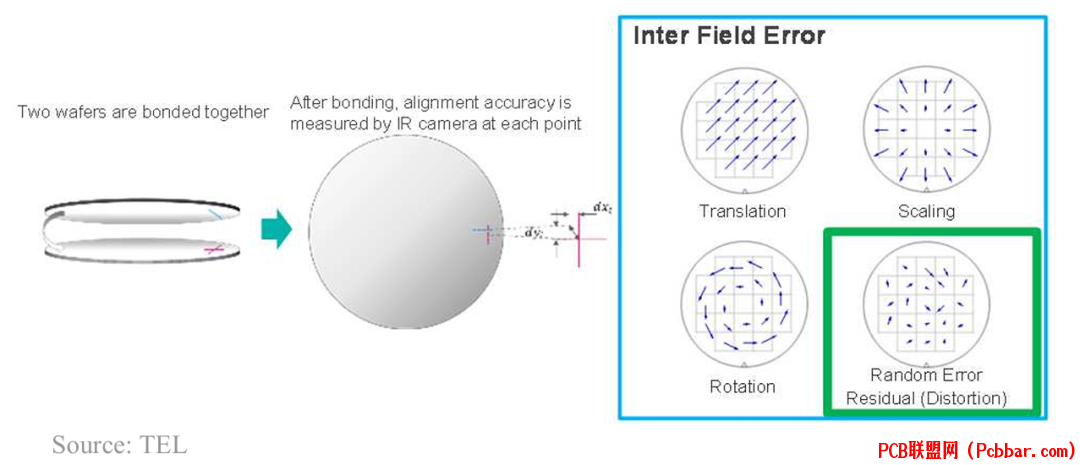

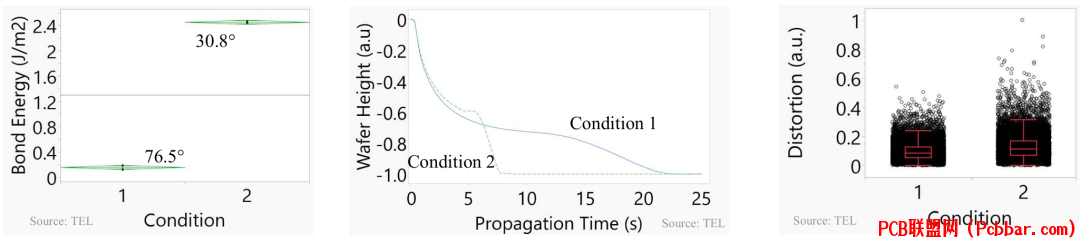

影响因素的全面分析

7 [1 Y0 Q0 B h- K. H5 A8 r0 k* G; z# b晶圆键合的成功取决于多个因素的复杂相互作用,这些因素在整个工艺过程中都需要仔细控制。可以系统地对这些因素进行分类和分析,以优化键合结果。* e; a8 V0 L+ H8 c. ?5 M ?

e4tnxatu0xt64012025031.png

; R: |! }, Y& z4 X: \ C* N图5:对晶圆对晶圆键合变形的影响因素的详细分类,包括晶圆特性、工艺参数和设备考虑因素。这种全面概述有助于理解变形控制的多面性。

7 O7 h+ ~8 ]2 B8 q7 \0 ^, |" d

' e; R% m1 @3 O* W, X4

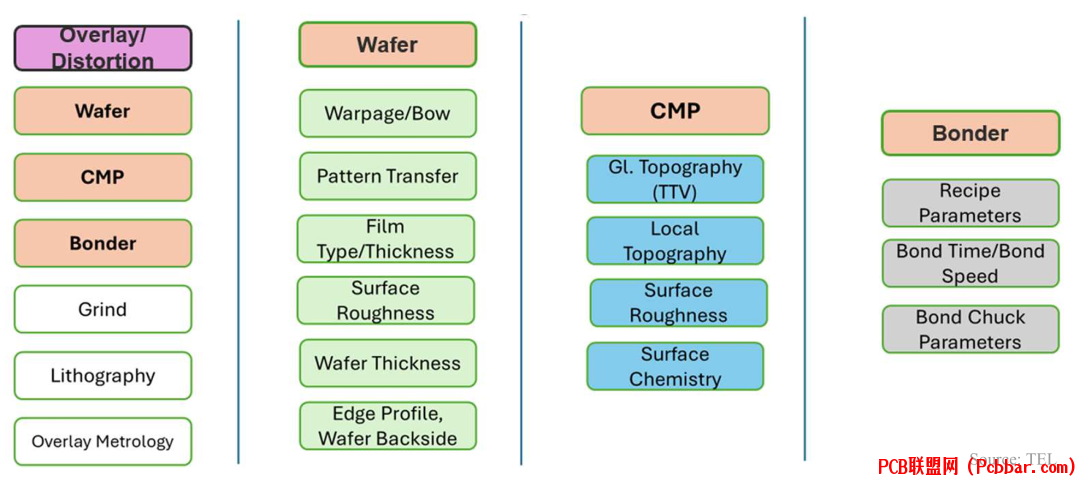

+ g! s3 V$ Q" F表面质量和键合传播" J l6 ?6 ~: x8 t4 M

表面特性与键合性能之间的关系是工艺中最关键的方面之一。表面质量直接影响接触角、键合能量和传播速度,进而影响最终的变形结果。

1 D: Z$ C5 L8 n9 P7 j

nfinuscsq0c64012025131.png

1 ]7 ^' r7 x7 M

1 ]7 ^' r7 x7 M

图6:三面板图示展示了表面质量与关键键合参数之间的关系:(左)接触角和键合能量,(中)传播速度,(右)产生的变形。这些图表展示了表面特性和键合结果之间的复杂相互作用。% u3 C+ Z7 D9 x, i

0 {+ U# ^& q& b

5' m- D' w5 H4 d. G6 p+ G8 J( Q- [

工艺优化和应力管理

* h* I, n% R- q, K) e% y* a/ o9 l通过表面处理优化进行有效的应力管理,对于实现高质量键合同时最小化变形起着关键作用。

* {+ W! ~9 x8 D6 \+ \

i15ye5gxa4t64012025231.png

c& R! @2 _1 m4 ]; M3 W

c& R! @2 _1 m4 ]; M3 W

图7:通过优化表面处理实现晶圆应力降低的图表,同时保持所需的键合能量水平。该图展示了不同表面处理条件在管理晶圆应力方面的效果。' t3 t9 j% }6 L, K" I4 S( ?

( O& q, a3 X* r" |# ?" g

6

l% [3 [4 S% _! b+ u图形传递和界面质量

( m1 ?* Z \1 N/ ~图形传递效应和界面质量的管理是成功实现晶圆键合的另一个重要方面。底层器件结构的图形会影响键合表面的均匀性和平整度。

x/ T2 G. C% q& \6 a

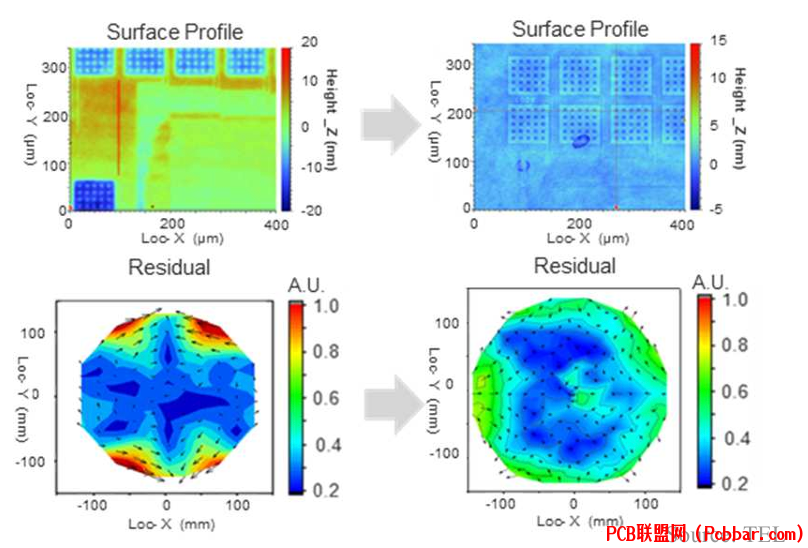

q05suzeh40j64012025331.png

. J0 I& T. W6 b/ r! f

. J0 I& T. W6 b/ r! f

图8:两面板比较展示了通过改进底层器件层的图形传递控制来消除非均匀边缘变形的效果。这种优化对于确保整个晶圆表面的键合质量具有重要意义。

6 q9 V5 s; N0 M. i2 ~1 X; M& I+ ^" J3 q; C% s

3fxprripw3u64012025431.png

! \" @8 Q1 ^* W; ]- b0 M图9:显微镜图像显示了由于底层结构的形貌传递导致键合界面处的空洞形成,强调了适当平坦化的重要性。& h- Y$ @5 u' B; S9 {$ K

0 d! R# f3 z! W: Q' Q% a% n; D3 b1 k7+ Z! g7 e6 B9 ~1 T1 V1 q& J

形状效应和工艺集成0 n; x& ~; h+ j* V. \1 \

晶圆形状对键合结果的影响贯穿多个工艺步骤,在工艺集成过程中需要仔细考虑。晶圆的初始形状会影响键合过程中的应力分布,并在后续减薄和处理过程中继续产生影响。; |. I, N' }& `

diovxypodch64012025531.png

. k2 E- W- @5 Q( l" Z- l8 \图10:多面板图示展示了晶圆形状如何通过键合和减薄工艺的各个阶段影响变形,展示了形状相关效应的传播过程。这种理解对于优化整体工艺流程非常重要。8 I* ]9 S7 T6 ]. h/ g/ Y

" P* y9 R# j( r* u1 t' C8, l, _5 \5 w: [( b7 U

先进工艺控制和模拟/ Q8 V( {* ?4 C+ [

实施复杂的工艺控制和模拟工具已经成为实现先进逻辑器件所需严格规格的基本要求。模拟工具能够预测和优化键合过程中的各种参数。

8 Q& [0 W3 i1 a" P% G+ P' k' E

g2kgechqbmi64012025631.png

( `: G1 F4 F1 ^1 l5 s- M4 x4 P* _图11:键合模拟模型的详细示意图,显示了键合过程中各组件及其相互作用。这种模拟能力为工艺优化提供了重要指导。

4 E( |) Q9 u/ b+ F1 b5 t+ \# }) R" C" x4 ^2 c

9

) Z% ~, V3 f1 | x P8 y性能优化和结果+ [9 y! i4 n/ C3 h* W

通过多个工艺参数的精确优化,晶圆键合性能取得了显著提升。这些改进包括中心区域和边缘区域变形的减少。) E# C! p) E7 ?: F' Q8 M) H

53ztxuae5c264012025732.png

2 m* \8 Z G2 q

2 m* \8 Z G2 q

图12:展示300毫米晶圆对晶圆键合结果,实现了36纳米(3σ)的变形控制,代表了键合技术发展的重要里程碑。这一成果对于支持先进逻辑器件的制造具有重要意义。) F% b' O/ [! }1 q2 U" w

# D& U5 h+ F) P

02lxdl5e1oe64012025832.png

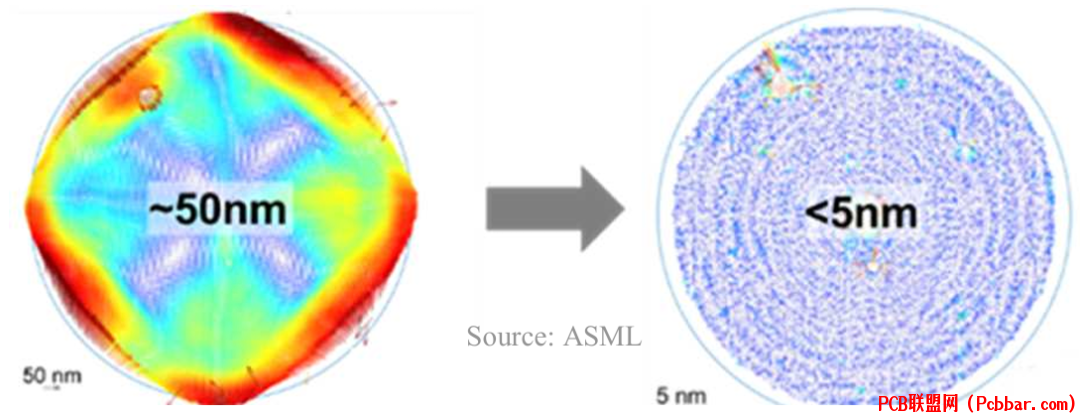

4 Y3 ~3 I) |/ k4 h9 A图13:两面板比较显示在研发环境中将键合后约50纳米的变形通过光刻校正减少到小于5纳米,展示了综合工艺优化策略的效果。这种变形控制能力对于实现高精度的三维集成很重要。' l' f: G8 c! {* L

- N9 D: \' W+ U9 W+ R. ?! R+ ~% E9 T

104 p8 v5 j3 F% ?7 s

总结

: Z- W8 F% {2 I" s半导体器件的持续发展对晶圆键合提出了更高要求。通过表面处理、工艺参数和集成策略的优化,半导体行业在满足先进逻辑器件的严格要求方面取得了显著进展。控制变形到5纳米以下的能力,为更复杂的三维集成结构提供了技术支持。随着器件架构向更高复杂度发展,精确控制键合工艺将继续作为半导体技术进步的重要基础。4 z' B L. Z+ W2 d

2 q/ ~9 r5 E; A8 g0 R, o

参考文献- q" K& f9 ^6 h0 k, C

[1] S. Arkalgud, C. Netzband, N. Ip, A. Tuchman, Y. Kondo, I. Son and A. Raley, "Implications of Wafer Bonding for Advanced Logic Technology Development," in 2024 IEEE International Electron Devices Meeting (IEDM), 2024.1 U8 c: X' x7 @" K" J

END

) Z; ~. o4 K$ V2 p8 v软件试用申请欢迎光电子芯片研发人员申请试用PIC Studio,其中包含:代码绘版软件PhotoCAD,DRC软件pVerify,片上链路仿真软件pSim,光纤系统仿真软件pSim+等。更多新功能和新软件将于近期发布,敬请期待!7 ^( I. p" Q; K* {- B5 w& P

点击左下角"阅读原文"马上申请

3 n- P& @7 C- ]6 t6 U

& J/ ~ h0 b A- v9 Y2 r欢迎转载4 J! U3 G' P' H6 k1 D( ?1 F3 z* m6 p/ U

! b+ J8 @( ?' _0 v/ a* j" h! i

转载请注明出处,请勿修改内容和删除作者信息!. @- f1 B! |* B4 G- w# m! I

$ k2 G! B2 U! |8 A0 j. Y

5 k, O& c E- }5 ]0 S# a; |

$ R" Q# b* o) j, c

ljcjcutfglf64012025932.gif

' o$ ^ o8 c2 A: L! q& M

' o$ ^ o8 c2 A: L! q& M

2 g2 s7 W/ p* x% w% M7 [- V& H4 h

关注我们7 [1 H% `9 p! l! ^' S2 R

; j0 J/ N% Q( i( Q' p; n) D

$ v; k9 T' ^0 J6 @" r

30kekt54zf064012026032.png

! i3 O# Y( j* S$ n

! i3 O# Y( j* S$ n

| , x( Z. j: N7 M# c# u

fpow4c1msdf64012026132.png

' Y( a6 [3 u4 U% K& c

' Y( a6 [3 u4 U% K& c

| W" }7 l! o9 Y, Q% F9 k' U* {( }$ e

1owsrmsnneu64012026232.png

) T8 o0 U" f9 Y1 Q7 G5 Y2 `2 c( m6 Q

) T8 o0 U" f9 Y1 Q7 G5 Y2 `2 c( m6 Q

|

+ {' C& Q0 P$ i' u: v1 o: ]

: |1 D0 i- B% F

2 A! c& C. N$ h- h, G

) [5 j: D. S# M6 {关于我们:

r3 Q3 {2 C" H4 J# }深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。* S+ P0 x6 P. y

" V9 R$ K+ w" q) k/ T$ J3 f7 {http://www.latitudeda.com/

! O) j, {. s# Q8 g- ]/ w! A7 V(点击上方名片关注我们,发现更多精彩内容) |

|